Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве логического элемента сравнения частоты следо вания импульсов задающего генератора, определяющего частоту вращения двигателя в дискретных астатических электроприводах, и частоты следования импульсов датчика обратной связи,, расположенного на валу двигателя, а. т4кже в других системах фазовой синх- рс низации.

Цель изобретения - повьпиение точ- нфсти и надежности работы за счет устранения сбоев при совпадении во времени входных импульсов.

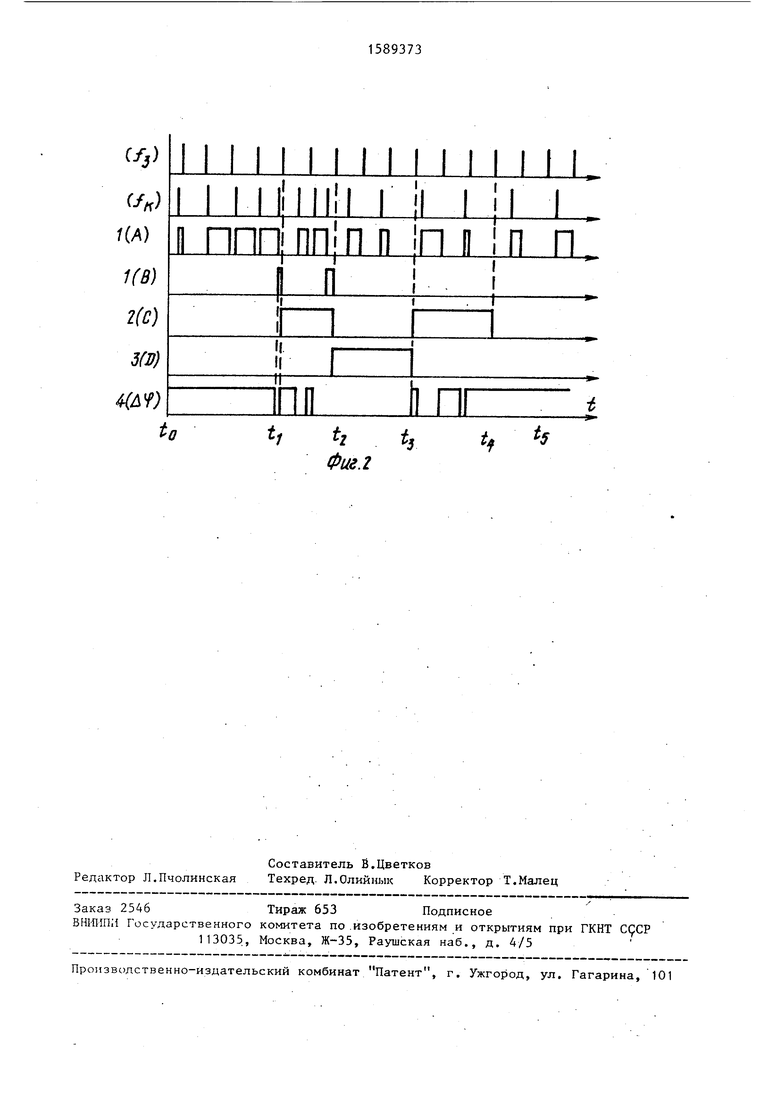

; На фиг. 1 представлена функцио- н льная электрическая схема предлагаемого частотно-фазового дискриминатора; на фиг, 2 - временные диаграммы, пoяcняюu иe его работу.

; Предлагаемый частотно-фазовый дискриминатор содержит блок 1 фазо- в1эго сравнения, блок 2 логической б юкировки, г ервый 3 и второй 4 блокирующие триггеры, RS-триггер 5, пер- вЫй 6, второй 7 элементы И-НЕ, третий элемент И-НЕ 8, первый элемент И 9, дешифратор Ю, первьй 11 и второй 12 D-триггеры, элемент ИЛИ-НЕ 13 Сумматор 14 и второй элемент И 15.

Частотно-Фазовый дискриминатор работает следующим образом.

Блок 1 фазового сравнения служит Для фазового сравнения импульсов талонной и контролируемой частот и формирования последовательности импульсов, снимаемых с первого выхода блока 1, период следования которых равен периоду эталонной частоты, а длительность пропордиональна величине фазового рассогласования сравниваемых частот. Блокирующие триггеры 3 и 4 служат для формирования сигна- , лов блокировки выходного сигнала блока 1 сравнения с помощью блока 2 логической блокировки. При этом высоки уровень сигнала С на выходе первого блокирующего триггера 3 соответствует режиму фазового сравнения, а высокий уровень сигнала D на выходе второго блокирующего триггера 4 - режиму насьщения частотно-фазового дисриминатора при к

Блок 2 логической блокировки служ для формирования выходного сигнала )з соответствии с логической функцией iCf АС (B+D), где А - выходной сигн

с первого выхода блока 1 фазового сравнения, пропорциональный величине фазового рассогласования сравниваемых частот (инверсный сигнал); В - выходной сигнал с второго выхода блока фазового сравнения 1, соответствующий приходу двух или более импульсов контролируемой частоты между двумя импульсами эталонной частоты; С - выходной сигнал первого блокирующего триггера 3; D - выходной сигнал второго блокирующего триггера 4,

Режим фазового сравнения дискриминатора соответствует наличию высокого уровня сигнала С и низких уровней сигналов Б и D, При этом проинверти- рованный сигнал А проходит на выход устройства. Дешифратор 10 в зависимости от состояния блока 1 фазового сравнения и блокирующих триггеров 3 и 4 формирует сигналы, поступающие на информационные входы этих триггеров.

Работу дешифратора 10 можно пояснить таблицей состояния.

2345

Примечание. D3 иВ4- выходы

блокирующих триггеров 3 и 4 соот- BeTCTBetiHO.

Первый 11 и второй 12 D-триггеры вместе с вторым элементом И-НЕ 7 образуют синхронный счетчик импульсов контролируемой частоты. Второй элемент И-НЕ 7 осуществляет требуемую начальную установку триггера 5 и формирует сигнал на информационных входах триггеров 11 и 12. RS-триггер 5 служит для формирования сигнала разрешения сброса счетчика в начальное

51589373

положение по переднему фронту импульса эталонной частоты. Синхронный счетчик импульсов служит для подсчета количества импульсов контролируемой частоты, поступивших между двумя импульсами эталонной частоты. Если счетчик импульсов находится в состоянии, отличном от начального, то на втором входе RS-триггера 5 устанавливается высокий уровень напряжения и в момент прихода импульса эталонной частоты f триггер 5 сохраняет свое состояние, при этом элемент И-НЕ 6 открыт и сигнал проходит на сброс счетчика, т.е. первого 11 и второго 12 D-триггеров. После сброса RS-триггер 5 устанавливается в состояние , элемент И-НЕ 6 закрывается, а счетчику разрешается вести подсчет импульсов контролируемой частоты f.

При отсутствии импульсов контролируемой частоты ц между двумя им- пульсами эталонной частоты f в блокирующих триггерах 3 и 4 происходит изменение информации следующим образом:

а)из режима насьпцения при происходит переход в режим фазового сравнения;

б)из режима фазового сравнения происходит переход в режим насыщения при f к f5 ;

в)режим насыщения при храняется.

При приходе двух и более импульсов контролируемой частоты f . между двуя импульсами эталонной частоты f происходит один из следу.ощих перехоов :

а)из р.ежима насьпцения при f f происходит переход в режим фазового сравнения;

б)из режима фазового сравнения происходит переход в режим со10

15

о к во ни сы за хо и ля ме

дл но

ча f|

20 о(е ча со f в

25 ни -ри на

де а 30 пу

нах На гер пря нал ней

35

тот 40 дву сам нас лен вых 45 лен инт жим ка осу 50 вто уме мом межд возв JJ ния тоты пуль в мо режи

в)

сыщения при f С;

при f-j 00k S

режим насыщения храняется. Устройство может находиться в трех основных режимах работы: насьщения при f f g, фазового сравнения и насьт(ения при f f. Переход из режима в режим синхронизирован по импульсам эталонной частоты f. В каждом режиме работы осуществляется подсчет числа импульсов контролируемой частоты f.j между двумя импульсами эталонной частоты.

Если устройство находится в режиме фазового сравнения, то элемент И-fiE 8 открыт сигналом с выхода первого блокирующего триггера 3 и сигнал А с первого выхода блока 1 фазового сравнения проходит на выход. В режимах насыщения дискриминатора элемент И-НЕ 8 закрыт низким уровнем сигнала с выхода первого блокирующего триггера 3 и выходной сигнал устройства определяется сигналом на втором входе элемента И 9.

Временные диаграммы (фиг. 2) даны для различных режимов работы частотно-фазового дискриминатора.

На интервале

эталонная

частота f превышает контролируемую f|. Дискриминатор находится в насыо(ении. При увеличении контролируемой частоты в момент прихода двух импульсов частоты f 1 между двумя импульсами f (момент t) устройство переходит в режим фазового сравнения. Опережение изменения выходного сигнала диск- -риминатора обусловлено действием сигнала В, передний фронт которого опреК

деляется фронтом второго импульса f а задний фронт - передним фронтом им- пульса fj.

На интервале t - t дискриминатор находится в режиме фазового сравнения. На выходе первого блокирующего триггера 3 находится высокий уровень напряжения, разрешающий прохождение сигнала А на выход устройства. При даль--, нейшем нарастании контролируемой час

тоты f в момент повторного прихода двух импульсов f между двумя импуль-т сами fj устройство переходит в режим насьш1ения при . Опережение появ- ления низкого уровня напряжения на выходе устройства обеспечивается появ- лением высокого уровня сигнала В. На интервале 2 Дискриминатор в режиме насыщения при fy,f.. Блокировка сигнала А с первого выхода блока 1 осуществляется сигналом D с выхода второго блокирующего триггера 4. При уменьшении контролируемой частоты в момент t прихода нуля импульсов fj между двумя импульсами f . устройство возвращается в режим фазового сравне- ния, а при дальнейшем уменьшении частоты f J, (повторном приходе нуля имульсов f, между двумя импульсами f. ) момент t устройство переходит в ежим насьш(ения при . Дальнейшее снижение частоты не приводит к изменению режима работы.

В результате обеспечивается надежная работа дискриминатора при совпадении во времени входных импул1,сов за счет синхронизированного переключения по передним фронтам входных (Импульсов блока 1 фазового сравнения и блокирующих триггеров 3 и 4.

Формула изобретения

: Частотно-фазовый дискриминатор, Содержащий последовательно соединенные блок фазового сравнения, первый и второй входы которого являются соответственно первым и вторым входами (частотно-фазового дискриминатора, и блок логической блокировки, выход которого является выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, 1выходы которых соединены соответственно с вторым и третьим входами бло- ка логической блокировки, при этом блок фазового сравнения содержит последовательно соединенные RS-триггер и первый элемент И-ИЕ, второй вход Которого соединен с первым входом 3-триг1 ера и является -вторым входом ;блока фазового сравнения, и второй |элемент И-НЁ, а блок логической бло- |кировки содержит последовательно соединенные третий элемент И-НЕ, первьй элемент И, причем первый и второй ;Входы третьего элемента И-НЕ являются соответственно первым и вторым входами блока логической блокиро1зки, а выход первого элемента И - его выходом, отличающийся тем, что, с целью повьпиения точности и надежности в работе за счет устранения сбоев при совпадении но времени входных импульсов, в него введен дешифратор, первый и второй входы которого соединены соответственно с

первым и вторым выходами блока фазо- I

0

5

0

5

0

5

0

5

вого сравнения, третий и четвертый входы дешифратора соединены соответственно с выходами первого и второго блокирующих триггеров, информационные входы которых подсоединены соответственно к первому и второму выходам дешифратора,, а тактовые входы - к второму входу блока фазового сравнения, второй выход которого соединен с четвертым входом блока логической блокировки, при этом в блок фазового сравнения введены первый и второй D-триггеры, тактовые входы которых объединены между собой и являются первым входом блока фазового сравнения, инверсный выход первого и прямой выход второго D-григгеров являются соответственно первым и вторым выходами блока фазового сравнения, прямой выход первого и инверсный выход второго D-трйггеров соединены соответственно с первым и вторым входами второго элемента И-НЕ, выход которого соединен с вторым входом RS-триггера и информационными входами первог-о и второго D-тригге- ров, а выход первого элемента И-НЕ соединен с S-входом первого и R-BXO- дом второго D-триггеров, в блок ло- (Гической блокировки введен элемент ШШ-НЕ, первый и ВТОРОЙ входы которого являются соответственно третьим и четвертым входами блока логической блокировки, а выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента И, причем- дешифратор выполнен в виде сумматора, первый, второй, третий и четвертый входы которого являются соответственно одноименными входами дешифратора, и второго элемента И, первый и второй входы которого соединены соответственно с первым и вторым выходами сумматора, при этом выход второго элемента И и выход переноса сумматора являются соответственно первым и вторым выходами дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2011 |

|

RU2469461C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| Частотно-фазовый дискриминатор | 2018 |

|

RU2695986C1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2017 |

|

RU2647678C1 |

| Частотно-фазовый дискриминатор | 1977 |

|

SU699666A1 |

| Устройство для управления ведущим шаговым двигателем | 1981 |

|

SU999022A1 |

| Устройство для регулирования скорости движения магнитного носителя | 1979 |

|

SU932558A1 |

| Частотно-фазовый компаратор | 1979 |

|

SU773907A1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение точности и надежности работы частотно-фазового дискриминатора. Для этого дискриминатор содержит блок 1 фазового сравнения, блок 2 логической блокировки, логические триггеры 3 и 4, RS-триггер 5, элементы И-НЕ 6-8, элементы И 9 и 15, дешифратор 10, D-триггеры 11 и 12, элемент ИЛИ-НЕ 13 и сумматор 14. Цель достигается за счет устранения сбоев при совпадении во времени входных импульсов. 2 ил.

| Частотно-фазовый компаратор | 1974 |

|

SU484621A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-30—Публикация

1988-05-23—Подача