I

Изобретение относится к вычислительной технике и может быть использовано для управления вычислительной машины (в том числе и мультипроцессорной) без снижения ее производительности .

Известен пульт управления, содержащий панель индикации и управления, а также блок контроля и диагностики, включающий в себя специальный адаптер для управления пуйьтовым накопителем на гибком диске У J.

Однако пульт используется для пультовых операций процессор машины, тем самым снижая ее производительность и не обеспечивает пространственного и временного доступа к блокам машины, который необходим для сокращения времени контроля и диагностики оборудования, а также для возможности применения, пульта для управления мультипроцессорной вычислительной машины (ВМ)„

Наиболее близким к предлагаемо му является пульт управления содержащий вычислитель, информационный вход-выход которого соединен с выходом-входом блока оперативной памяти, а управляющий вход-выход С управляницим входом-выходом блока сопряжения с накопителем на магнитном диске, блока сопряжения с каналом, блока сопряжения с панелью

10 управления и индикации и блока .сопряжения с мащиной, к информационным входам-выходам которых подключены соответственно информационные входы-выход 4 накопителя на дисtsке, канала, панели Iуправления и индикации, и машины .

В этом пульте управления пульто„ вые операции не занимают время -процессора, что позволяет увеличить быстродействие на количество пультовых команд. Кроме того, имеется возможность программного доступа 3 к блокам машины через соответствующий блок сопряжения. Однако данное устройство при при менении в быстродействуюпщх мулътипроцессорных вычислительных машинах не обеспечивает нужного быстродействия вследствии большого времени реакции на запрос. Обработка запроса включает в себя формирование массива служебной информации и пере дачу этого массива в процессор. Обращение в память пульта возможно только со стороны вычислителя, поэтому формирование массива служебной информации и обмен могут идти только последовательно, что существенно увеличивает время реакции пульта на запросы цроцессора и не позволяет использовать пульт для уп равления ВМ, работающей в реальном масштабе времени. Таким образом, основным недостат ком устройства является недостаточное быстродействие. Кроме того, при сбое в процессе обмена необходимо повторять обработку запроса сначала, что также уменьшает быстродействие и увеличивает время реакции. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в пульт управления мультипроцессорной вычислительной машины содержащей вычислитель, информационный вход-выход которого соединен информационным выходом-входом блока оперативной памяти и первыми информационными выходами-входами первого и второго адаптеров, а управляющий выход - с первыми управлякщими входами первого и второго адаптеров, блок сопряжения с панелью управлени и индикации, первый вход-выход которого подключен к информационному входу-выходу панели управления и индикации, а второй выход-вход соед нен со вторым информационным входом выходом первого адаптера, третий ин формационный вход-выход которого подключен к первому информационному выходу-входу блока сопряжения с вычислительной машиной, второй информационный вход-выход второго ада тера подключен к входу-выходу блока сопряжения с накопителями, введены блок приоритета, блок формирования прерываний, блок формирования меток времени и блок сопряжения с перифе74рийными абонентами, причем управляющий выход блока приоритета соединен с соответствукщим входом блока оперативной памяти, разрешающий выход - с управляющим входом вычислителя, разрешающими входами первого и второго адаптеров, выход блока формирования прерываний подключен к управляющему входу вычислителя, маскирующий вход - к управлякяцему выходу вычислителя, первый и второй запросные входы - соответственно, к выходам прерываний первого и второго адаптера, третий, четвертый и пятый запросные входы блока формирования прерываний соединены соответственно с выходами прерываний панели управления и индикации всех блоков сопряжений и блока формирования меток времени, управляющий вход которого соединен с управляющим выходом вычислителя, а управляющий выход - с тактовыми входами первого и второго адаптеров и всех блоков сопряжения, первый, второй и третий запросные входы блока приоритета соединены соответственно с управляющими выходами вычислителя, первого и второго адаптеров, первый второй и третий запросные входы блока приоритета соединены соответственно с управляющими выходами вычислителя, первого и второго адаптеров, третий информационный вход-выход которого соединены с входом-выходом блока сопряжения с периферийными абонентами, управляющий вход блока формирования прерываний является управлякхцим входом пульта, вторые информационные входы-выходы блока сопряжения с вычислительной машиной и блока сопряжения с периферийными абонентами являются информационным входами-выходами пульта. Пульт управления мультипроцессорной ЭВМ представляет собой управлякмцую вычислительную машину повышенной надежности, содержащую разветвленную систему обработки и хранения запросов. Запросы от процессоров бывают двух типов. Первый - запросы, связанные с приемом исходных данных с периферийного устройства пульта управления, формированием массива служебной информации и передачей его в процессор. Второй - с приемом массива служебной информаг, ции, анализом этого массива и вьздачей результатов анализа в периферийный абонент пульта управления. Таким образом, время реакции на запрос распадается на три составляющие: время формирования или анализа массива; времена обмена пульта управ ления с процессором; время обмена пульта управления с периферийным устройством. Обмен и формирование (анализ) м 1ссива идут одновременно.

Для повьшения быстродействия обмена сигналы интерфейса между блоками сопряжения и адаптерами, а также между блоками сопряжения и внешними устройствами контролируются времешшми метками, приходящими с блока формирования меток времени. Это позволяет, в случае сбоя программно повторить обмен.

Пульт управления осуществляет индикацию состояния машины. Для этого каждый 10 м«сек, постоянно обновляемая информация о состоянии машины, высвечивается на панели индикации и управления,

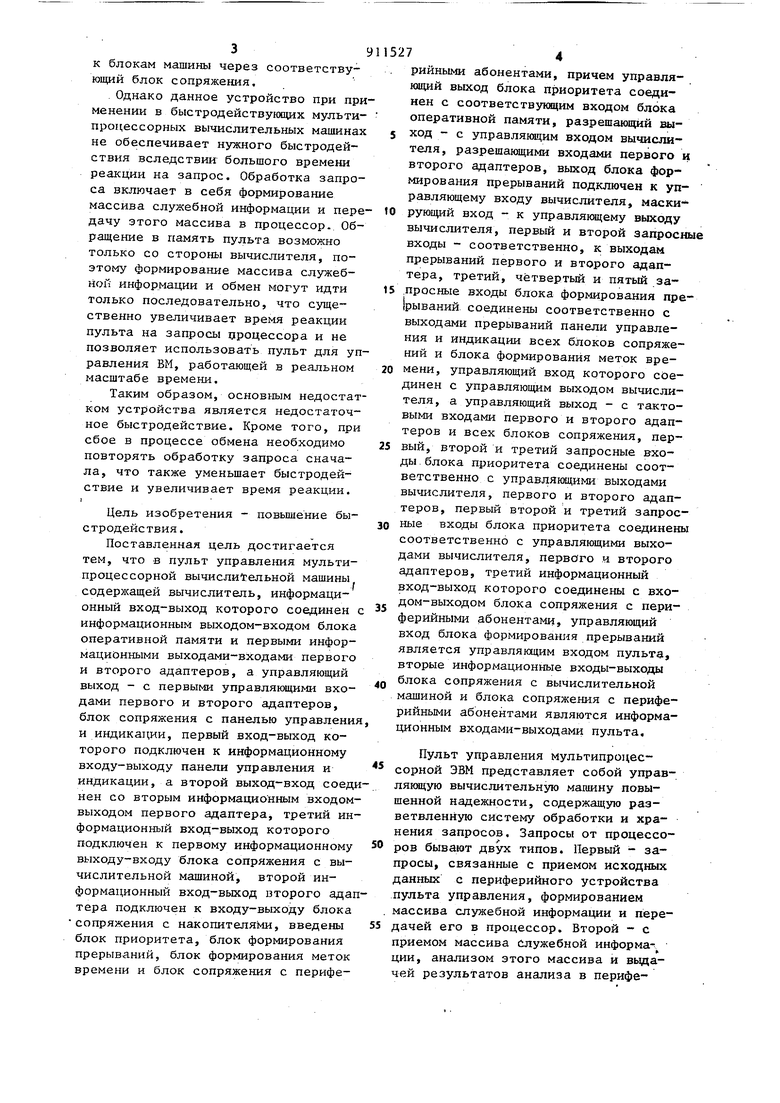

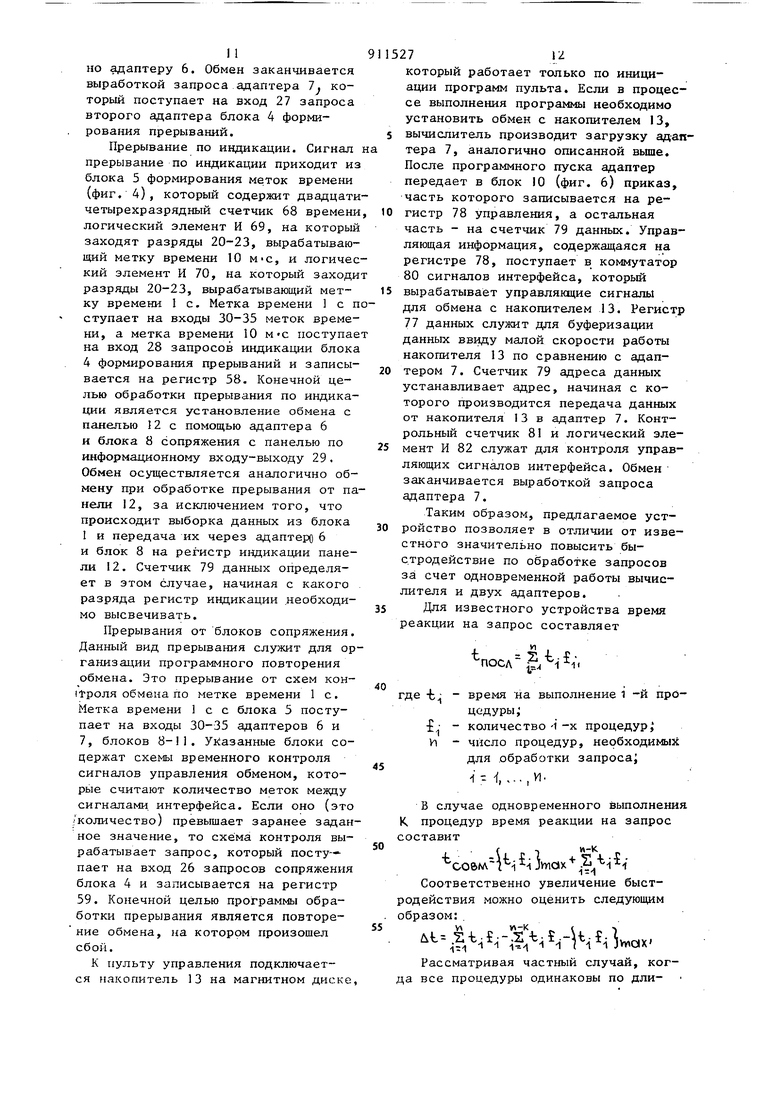

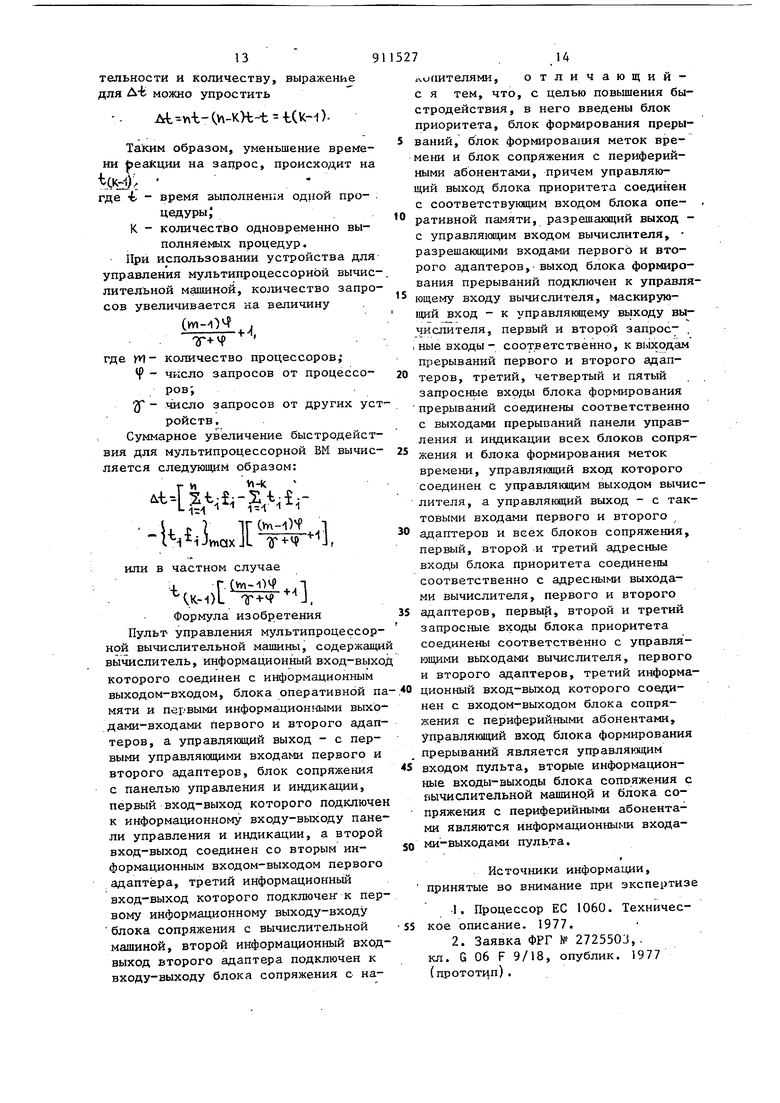

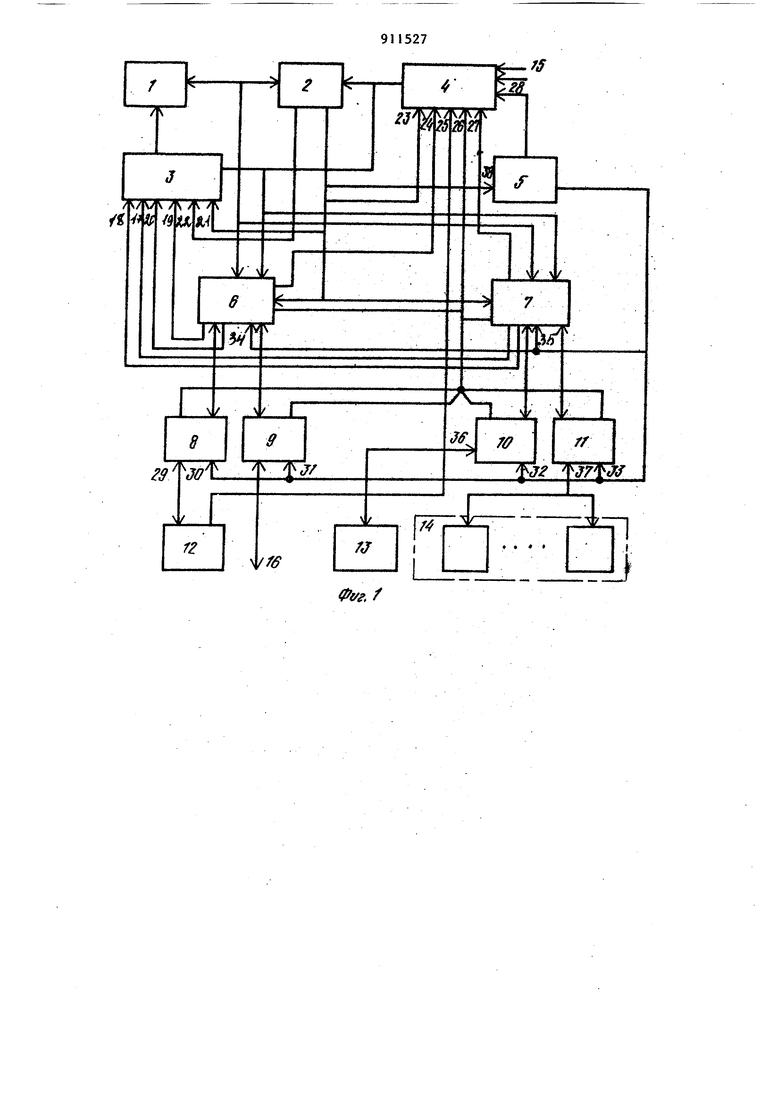

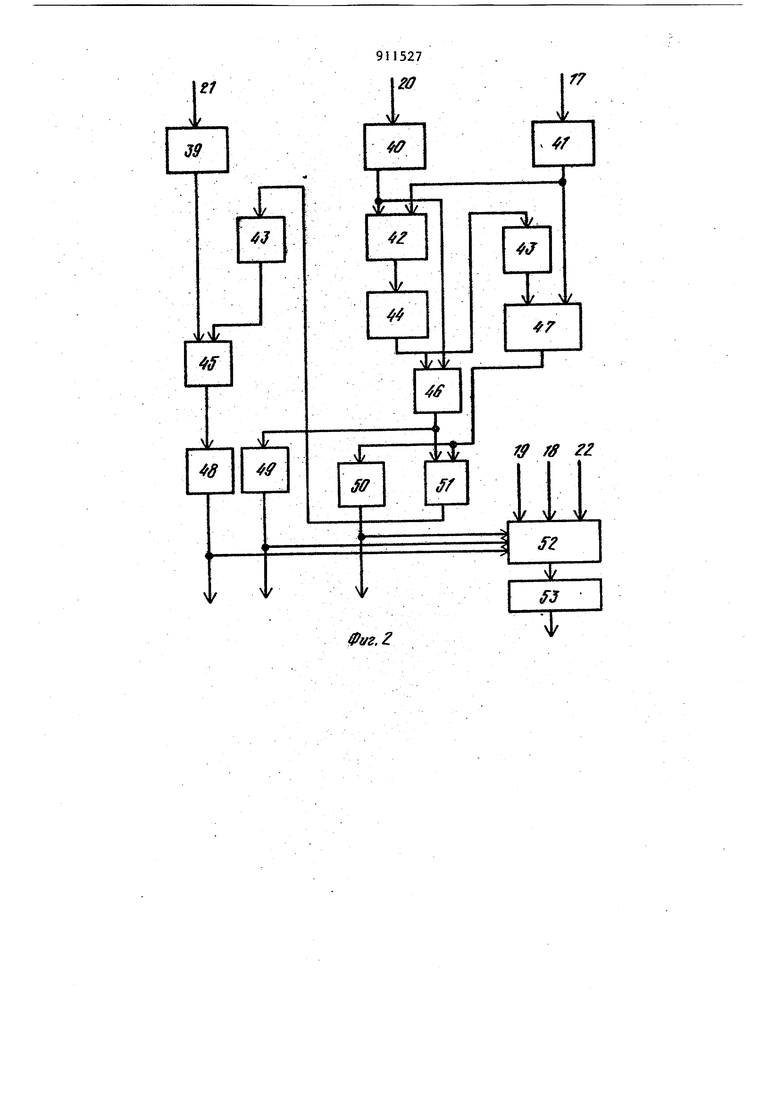

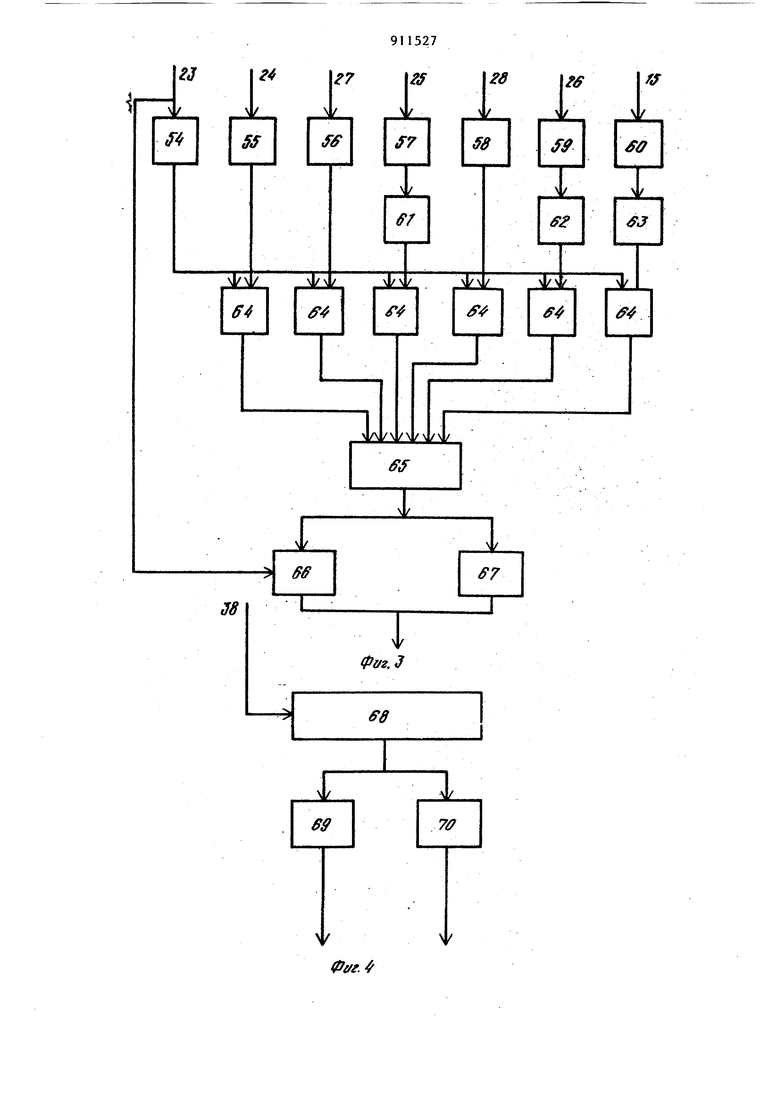

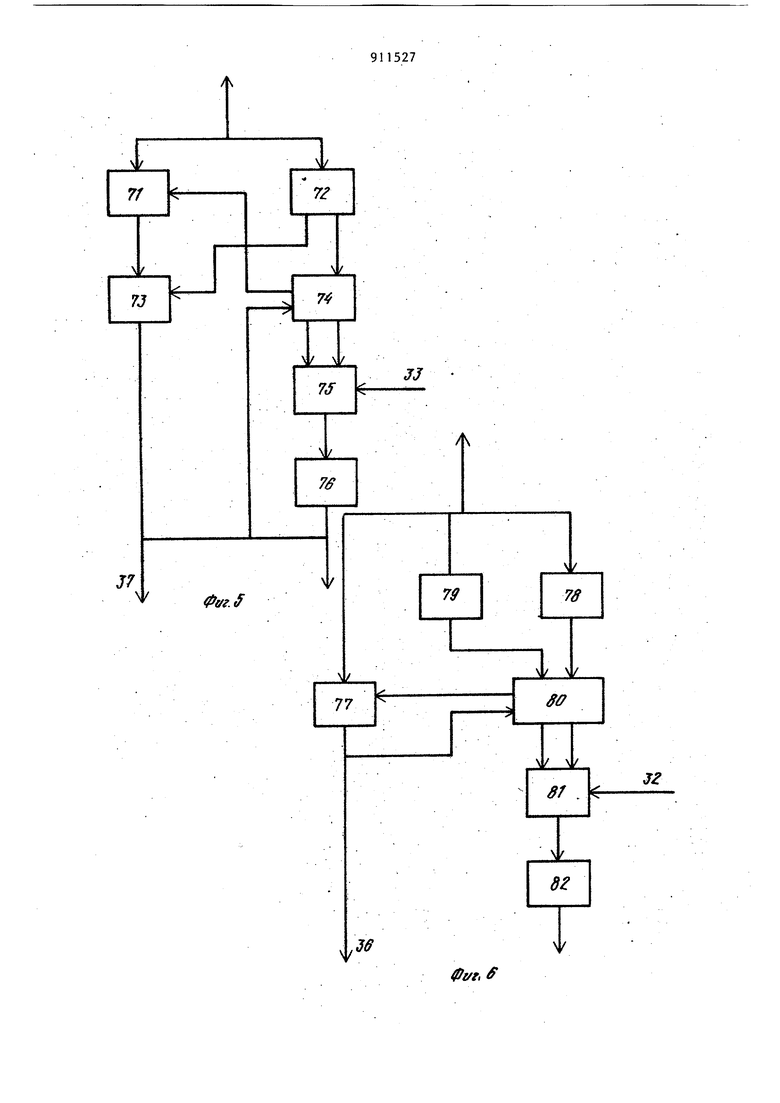

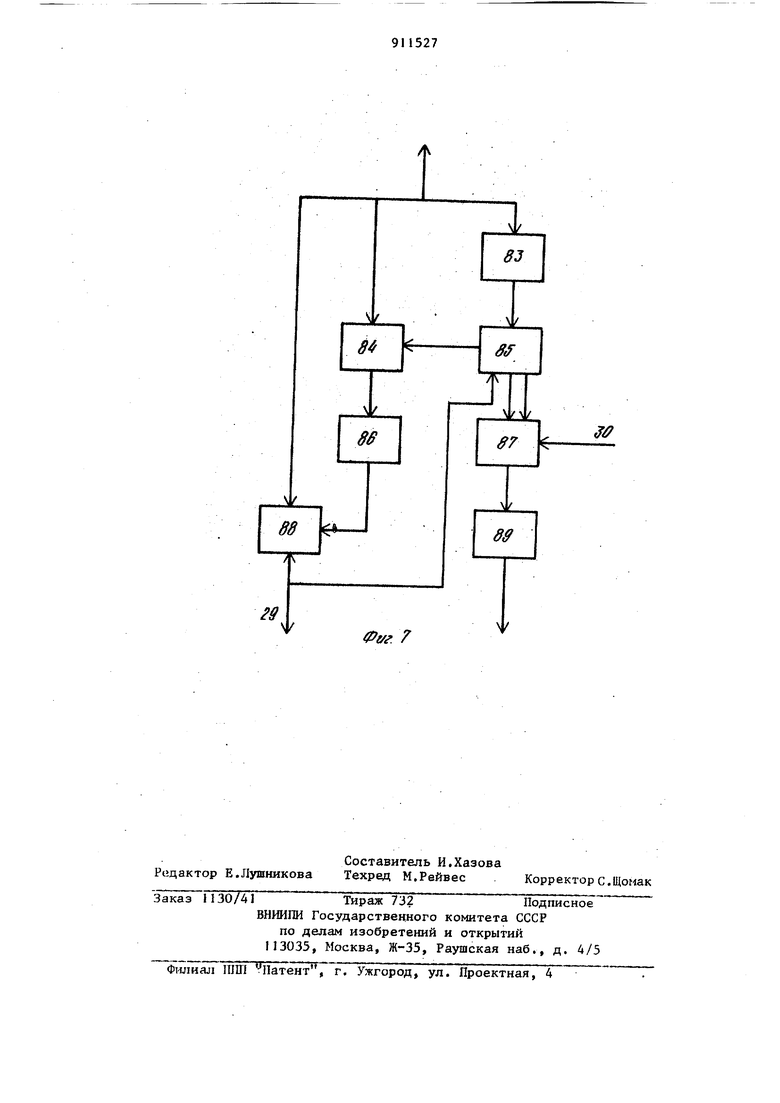

На фиг. 1 представлена блок-схема пульта управления многопроцессорной ЭВМ, на фиг, 2 - блок-схема блока приоритета, на фиг, 3 - блок-схема блока формирования прерываний; на фиг, 4 - блок-схема блока формирования меток времени; на фиг, 5 блок-схема сопряжения с периферийными абонентами, на фиг, 6 - блоксхема блока сопряжения с накопителями, на фиг. 7 - блок-схема блока сопряжения с панелью индикации и управления.

Йульт управления мультипроцессорной вычислительной машины (фиг, 1) содержит блок 1 оперативной памяти, вычислитель 2, блок 3 приоритета, блок 4 формирования прерываний, блок 5 формирования меток времени, первый адаптер 6, второй адаптер 7, блок 8 сопряжения с панелью управления и индикации, блок 9 сопряжения с вычислительной машиной, блок 10 сопряжения с накопителями, блок 11 сопряжения с периферийными абонентами, панель 12 управления и индикации, накопитель 13 на магнитном диске, группу периферийных абонентов 14, управляющий вход 15 пульта, информационные входы-выходы 16 пульта вход 17 запросов второго адаптера вход 18 адреса второго адаптера, вход 19 адреса первого адаптера, вхо

20запросов первого адаптера, вход

21запросов вычислителя, вход 22 адреса вычислителя, вход 23 маски, вход 24 запросов первого адаптера, вход 25 запросов панели, вход 26 запросов сопряжения, вход 27 запросов второго адаптера, вход 28 запросов индикации, информационный вход-выход 29, входы 30-35 меток времени, информационные входы-выходы 36-37 пульта, управляющий вход 38.

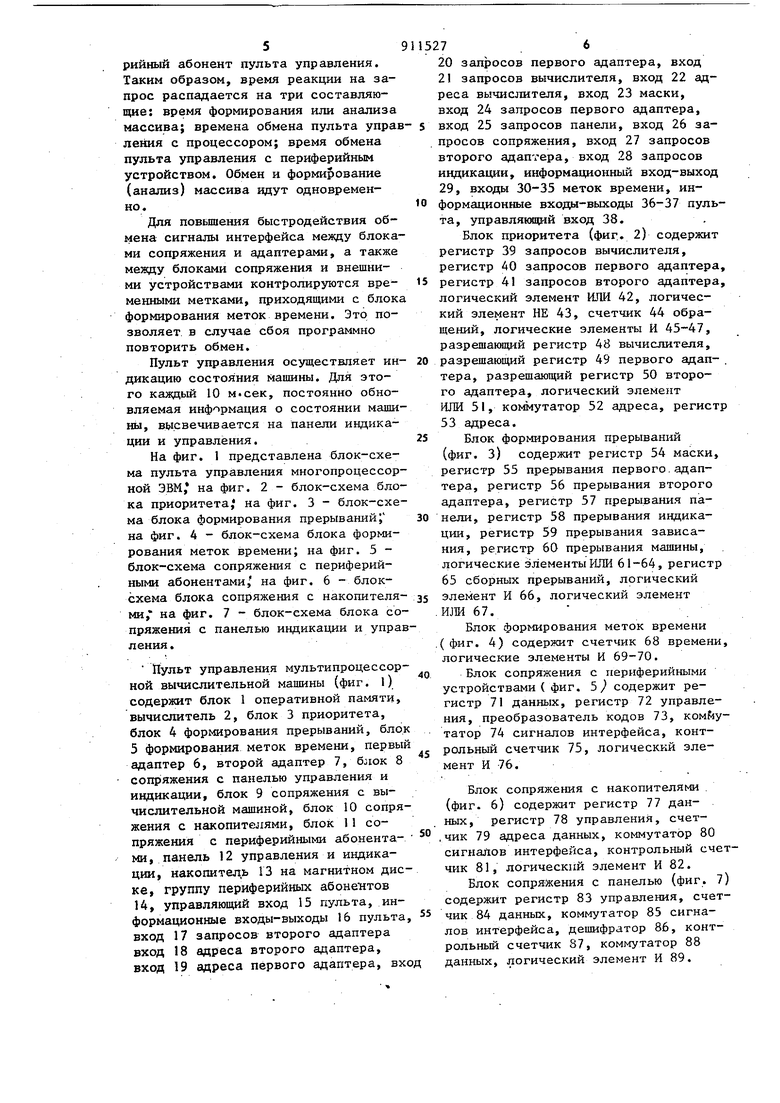

Блок приоритета (фиг. 2) содержит регистр 39 запросов вычислителя, регистр 40 запросов первого адаптера регистр 41 запросов второго адаптера логический элемент Ш1И 42, логический элемент НЕ 43, счетчик 44 обращений, логические элементы И 45-47, разрешающий регистр 48 вычислителя, разрешающий регистр 49 первого адаптера, разрешающий регистр 50 второго адаптера, логический элемент ШШ 51, коммутатор 52 адреса, регист 53 адреса.

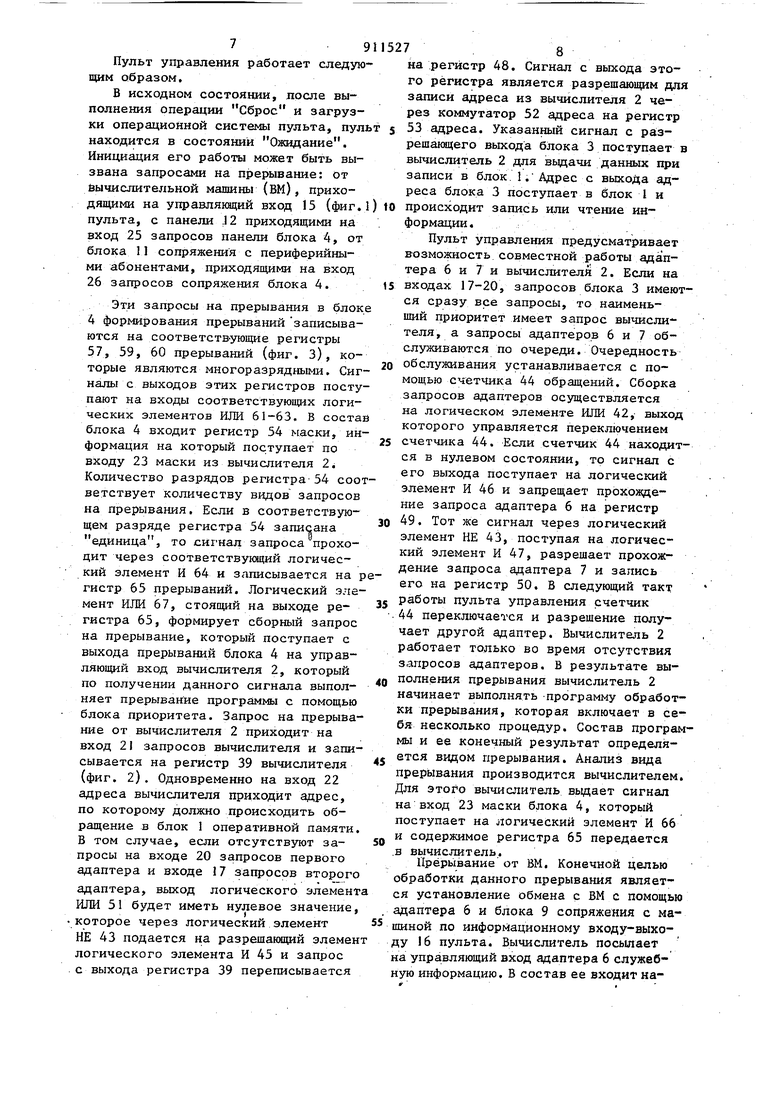

Блок формирования прерываний (фиг, З) содержит регистр 54 маски, регистр 55 прерывания первого, адаптера, регистр 56 прерывания второго адаптера, регистр 57 прерывания панели, регистр 58 прерывания индикации, регистр 59 прерывания зависания, регистр 60 прерывания машины, логические элементы РШИ 61-64, регистр 65 сборных прерываний, логический элемент И 66, логический элемент ИЛИ 67,

Блок формирования меток времени ( фиг, 4) содержит счетчик 68 времени логические элементы И 69-70,

Блок сопряжения с периферийными устройствами ( фиг, 5} содержит регистр 71 данных, регистр 72 управления, преобразователь кодов 73, KOMfiyтатор 74 сигналов интерфейса, контрольный счетчик 75, логический элемент И 76,

Блок сопряжения с накопителями . (фиг, б) содержит регистр 77 данных, регистр 78 управления, счет,чик 79 адреса данных, коммутатор 80 сигналов интерфейса, контрольный счечик 81, логический элемент И 82,

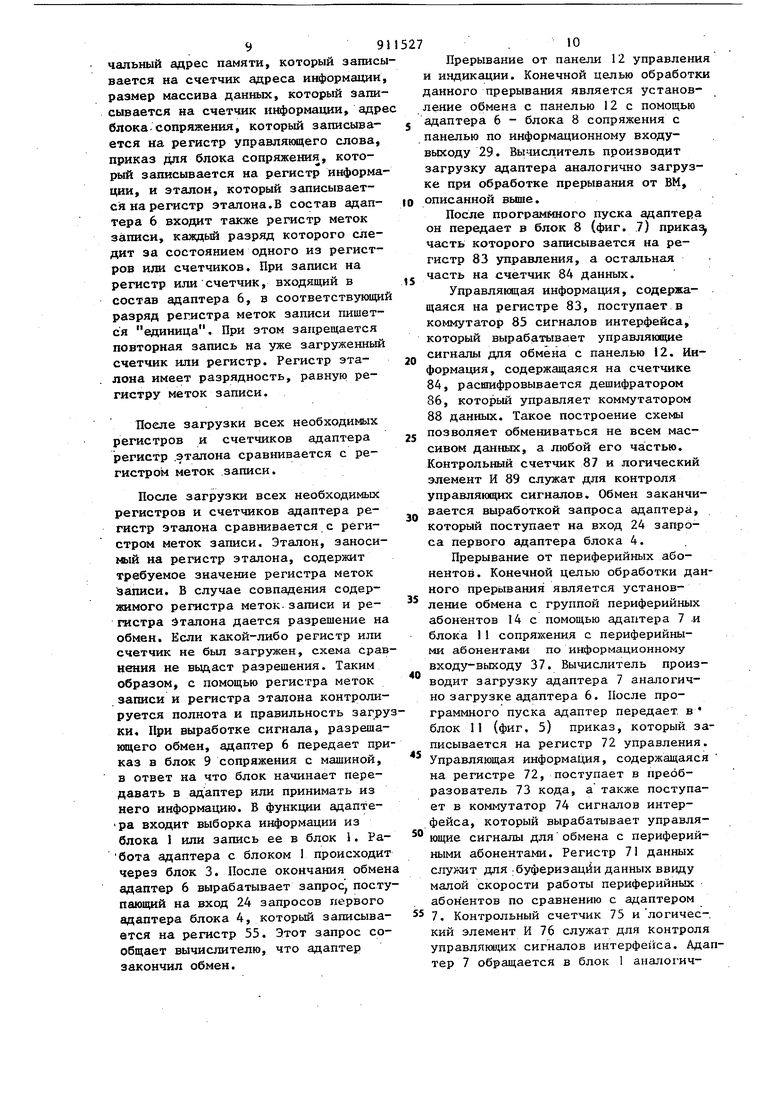

Блок сопряжения с панелью (фиг, 7 содержит регистр 83 управления, счетчик 84 данных, коммутатор 85 сигналов интерфейса, дешифратор 86, контрольный счетчик 87, коммутатор 88 данных, логический элемент И 89, Пульт управления работает следующим образом, В исходном состоянии, после выполнения операции Сброс и загрузки операционной системы пульта, пульт находится в состояний Ожидание. Инициация его работы может быть вызвана запросами на прерывание: от вычислительной машины (ВМ), приходяпшми на управляющий вход 15 (фиг.) пульта, с панели .12 приходящими на вход 25 запросов панели блока 4, от блока 11 сопряжения с периферийными абонентами, приходящими на вход 26 запросов сопряжения блока 4. Эти запросы на прерывания в блок 4 формирования прерываний записываются на соответств-зпощие регистры 57, 59, 60 прерываний (фиг. З), которые являются многоразрядными. Сиг налы с выходов этих регистров посту пают на входы соответствующих логических элементов ИЛИ 61-63. В соста блока 4 входит регистр 54 маски, ин формация на который поступает по входу 23 маски из вычислителя 2 Количество разрядов регистра54 соо ветствует количеству видов запросов на прерывания. Если в соответствуюразряде регистра 54 записана единица, то сигнал запроса проходит через соответствукмдий логический элемент И 64 и записывается на гистр 65 прерываний. Логический эле мент ИЛИ 67, стоящий на выходе регистра 65, формирует сборный запрос на прерывание, который поступает с выхода прерываний блока 4 на управляющий вход вычислителя 2, который по получении данного сигнала выполняет прерывание программы с помощью блока приоритета. Запрос на прерыва ние от вычислителя 2 приходит на вход 2I запросов вычислителя и запи сывается на регистр 39 вычислителя (фиг, 2). Одновременно на вход 22 адреса вычислителя приходит адрес, по которому должно происходить обращение в блок 1 оперативной памяти В том случае, если отсутствуют запросы на входе 20 запросов первого адаптера и входе 17 запросов второго адаптера, выход логического элемент ИЛИ 51 будет иметь нулевое значение которое через логический элемент НЕ 43 подается на разрешающий элемен логического элемента И 45 и запрос с выхода регистра 39 переписывается на регистр 48. Сигнал с выхода этого регистра является разрешающим для записи адреса из вычислителя 2 через коммутатор 52 адреса на регистр 53 адреса. Указанный сигнал с разрешакйцего выхода блока 3 поступает в вьшислитель 2 для выдачи данных при записи в блок. 1.Адрес с выхода адреса блока 3 поступает в блок 1 и происходит запись или чтение ийформации. Пульт управления предусматривает возможность совместной работы адаптера 6 и 7 и вычислителя 2, Если на входах 17-20, запросов блока 3 имеются сразу все запросы, то наименьший приоритет имеет запрос вычисли- теля, а запросы адаптеров 6 и 7 обслуживаются по очереди. Очередность обслуживания устанавливается с помощью счетчика 44 обращений. Сборка запросов адаптеров осуществляется на логическом элементе ИЛИ 42, выход которого управляется переключением счетчика 44. Если счетчик 44 находится в нулевом состоянии, то сигнал с его выхода поступает на логический элемент И 46 и запрещает прохождение запроса адаптера 6 на регистр 49. Тот же сигнал через логический элемент НЕ 43, поступая на логический элемент И 47, разрешает прохождение запроса адаптера 7 и запись его на регистр 50. В следующий такт работы пульта управления счетчик 44 переключается и разрешение получает другой адаптер. Вычислитель 2 работает только во время отсутствия запросов адаптеров, В результате выполнения прерывания вычислитель 2 начинает выполнять программу обработки прерывания, которая включает в себя несколько процедур. Состав программы и ее конечный результат определяется видом прерывания. Анализ вида прерывания производится вычислителем. Для этого вычислитель выдает сигнал на вход 23 маски блока 4, который поступает на логический элемент И 66 и содержимое регистра 65 передается вычислитель. ,в Прерывание от ВМ, Конечной целью обработки данного прерывания является установление обмена с ВМ с помощью адаптера 6 и блока 9 сопряжения с мацщной по информационному входу-выходу 16 пульта. Вычислитель посылает на управляющий вход адаптера 6 служебную информацию, В состав ее входит на99

чальный адрес памяти, который записывается на счетчик адреса информации, размер массива данных, который записывается на счетчик информации, адре блока-сопряжения, который записывается на регистр управляищего слова, приказ для блока сопряжения, который записывается на регистр информации, и эталон, который записываетcia на регистр эталона,В состав адаптера 6 входит также регистр меток записи, каждый разряд которого следит за состоянием одного из регистров или счетчиков. При записи на регистр или счетчик, входящий в состав адаптера 6, в соответствукицнй разряд регистра меток записи пишется единица, При этом запрещается повторная запись на уже загруженный счетчик или регистр. Регистр эталона имеет разрядность, равную регистру меток записи.

После загрузки всех необходимых регистров и счетчиков адаптера регистр .эталона сравнивается с регистром меток .записи.

После загрузки всех необходимых регистров и счетчиков адаптера регистр эталона сравнивается с регистром меток записи. Эталон, заносимый на регистр эталона, содержит требуемое значение регистра меток записи, В случае совпадения содержимого регистра меток.записи и регистра Эталона дается разрешение на обмен. Если какой-либо регистр или счетчик не бьш загружен, схема сравнения не выдаст разрешения, Таким образом, с помощью регистра меток записи и регистра эталона контролируется полнота и правильность загруки. При выработке сигнала, разрешаняцего обмен, адаптер 6 передает приказ в блок 9 сопряжения с машиной, в ответ на что блок начинает передавать в адаптер или принимать из него информацию, В функции адаптера входит выборка информации из блока 1 или запись ее в блок i, Работа адаптера с блоком 1 происходит через блок 3, После окончания обмен адаптер 6 вырабатывает запрос, поступающий на вход 24 запросов первого адаптера блока 4, который записывается на регистр 55, Этот запрос сообщает вычислителю, что адаптер закончил обмен.

27 .10

Прерывание от панели 12 управления и индикации. Конечной целью обработки данного прерывания является установление обмена с панелью 12 с помощью

адаптера 6 - блока 8 сопряжения с панелью по информационному входувыходу 29, Вычислитель производит загрузку адаптера аналогично загрузке при обработке прерывания от ВМ,

описанной выше.

После программного пуска адаптера он передает в блок 8 (фиг, 7) прика часть которого записывается на регистр 83 управления, а остальная

J часть на счетчик 84 данных,

Управлякяцая информация, содержащаяся на регистре 83, поступает в коммутатор 85 сигналов интерфейса, который вырабатывает управляюпще сигналы для обмена с панелью 12, Ин0формация, содержащаяся на счетчике 84, расшифровывается дешифратором 86, который управляет коммутатором 88 данных. Такое построение схемы

J позволяет обмениваться не всем массивом данных, а любой его . Контрольный счетчик 87 и логический элемент И 89 служат для контроля управляющих сигналов. Обмен заканчивается выработкой запроса адаптера, который поступает на вход 24 запроса первого адаптера блока 4,

Прерывание от периферийных абонентов. Конечной целью обработки данного прерывания является установSление обмена с группой периферийных абонентов 14 с помощью адаптера 7 .и блока 11 сопряжения с периферийными абонентами по информационному входу-выходу 37, Вычислитель произ0водит загрузку адаптера 7 аналогично загрузке адаптера 6, После программного пуска адаптер передает, в блок 11 (фиг, 5) приказ, который записывается на регистр 72 управления.

5 Управляющая информаЬуая, содержащаяся на регистре 72, поступает в преобразователь 73 кода, а также поступает в коммутатор 74 сигналов интерфейса, который вырабатывает управляOющие сигналы дляобмена с периферийными абонентами. Регистр 71 данных cjtyKHT для .буферизации данных ввиду малой скорости работы периферийных абонентов по сравнению с адаптером

7, Контрольный счетчик 75 илогический элемент И 76 служат для контроля управляющих сигналов интерфеГюа, Адаптер 7 обращается в блок 1 аналогичHO адаптеру 6. Обмен заканчивается выработкой запроса адаптера 7j который поступает на вход 27 запроса второго адаптера блока 4 формирования прерываний. Прерывание по индикации. Сигнал прерывание по индикации приходит из блока 5 формирования меток времени (фиг. 4), который содержит двадцати четырехразрядный счетчик 68 времени логический элемент И 69, на который заходят разряды 20-23, вырабатывающий метку времени 10 м-с, и логичес кий элемент И 70, на который заходи разряды 20-23, вырабатывающий метку времени 1 с. Метка времени 1 с п ступает на входы 30-35 меток времени, а метка времени 10 МС поступае на вход 28 запросов индикации блока 4 формирования прерываний и записывается на регистр 5В. Конечной целью обработки прерывания по индикации является установление обмена с панелью 12 с помощью адаптера 6 и блока 8 сопряжения с панелью по информационному входу-выходу 29. Обмен осуществляется аналогично обмену при обработке прерывания от па нели 12, за исключением того, что происходит выборка данных из блока I и передача их через адаптере 6 и блок 8 на регистр индикации панели 12. Счетчик 79 данных определяет в этом случае, начиная с какого разряда регистр индикации необходимо высвечивать. Прерывания от блоков сопряжения. Данный вид прерывания служит для ор ганизации программного повторения обмена. Это прерывание от схем кон1Троля обмена по метке времени 1 с. Метка времени 1 с с блока 5 поступает на входы 30-35 адаптеров 6 и 7, блоков 8-11. Указанные блоки содержат схемы временного контроля сигналов управления обменом, которые считают количество меток между сигналами интерфейса. Если оно (это /количество) превышает заранее задан ное значение, то схема контроля вырабатывает запрос, который посту-пает на вход 26 запросов сопряжения блока 4 и записывается на регистр 59. Конечной целью программы обработки прерывания является повторение обмена, на котором произошел сбой. К пульту управления подключается накопитель 13 на магнитном диске который работает только по инициации программ пульта. Если в процессе выполнения программы необходимо установить обмен с накопителем 13, вычислитель производит загрузку ад-аптера 7, аналогично описанной вьпае. После программного пуска адаптер передает в блок 10 (фиг. б) приказ, часть которого записывается на регистр 78 управления, а остальная часть - на счетчик 79 данных. Управляющая информация, содержащаяся на регистре 78, поступает в коммутатор 80 сигналов интерфейса, который вырабатывает управляющие сигналь для обмена с накопителем 13. Регистр 77 данных служит для буферизации данных ввиду малой скорости работы накопителя 13 по сравнению с адаптером 7. Счетчик 79 адреса данных устанавливает адрес, начиная с которого производится передача данных от накопителя 13 в адаптер 7. Контрольный счетчик 81 и логический элемент И 82 служат для контроля управляющих сигналов интерфейса. Обмен заканчивается выработкой запроса адаптера 7. Таким образом, предлагаемое устройство позволяет в отличии от известного значительно повысить быстродействие по обработке запросов за счет одновременной работы вычислителя и двух адаптеров. Для известного устройства время реакции на запрос составляет -b,f время на выполнение i -и прогде -Ь цедуры i -количество -i -х процедур J -число процедур, необходимый для обработки запроса В случае одновременного выполнения К процедур время реакции на запрос составит f ) ( -i ЗУМОХ .S i Соответственно увеличение быстродействия можно оценить следующим образом: -| -i«r| -i - ifiW Рассматривая частный случай, когда все процедуры одинаковы по дли13тельности и количеству, выражение для Afe можно упростить -t(k-1). Таким образом, уменьшение време ни реакции на запрос, происходит н ;см)/ где -t - время выполнения одной процедуры;К - количество одновременно выполняемых процедур. При использовании устройства дл управления мультипроцессорной вычи лительной машиной, количество запр сов увеличивается на величину ) , . т где КИ- количество процессоров; - число запросов от процессоров;У - число запросов от других ус ройств. Суммарное увеличение быстродейст вия для мультипроцессорной ВМ вычис ляется следующим образом: ГЦ -l,,rS,i,r ,, ИЛИ в частном случае ;, U-i)L Т+Ч Формула изобретения Пульт управления мультипроцессор ной вычислительной машины, содержащ вычислитель, информационный вход-вых которого соединен с информационным выходом-входом, блока оперативной

мяти и первыми информационшми выходами-входами первого и второго адаптеров, а управляющий выход - с первыми управляющими входами первого и второго адаптеров, блок сопряжения с панелью управления и индикации, первый вход-выход которого подключен к информационному входу-выходу панели управления и индикации, а второй вход-выход соединен со вторым информационным входом-выходом первого адаптера, третий информационньй вход-выход которого подключен- к первому информационному выходу-входу блока сопряжения с вычислительной машиной, второй информационный входвыход второго адаптера подключен к входу-выходу блока сопряжения с нанен с входом-выходом блока сопряения с периферийными абонентами, управляющий вход блока формирования прерываний является управлягадим входом пульта, вторые информационные входы-выходы блока сопряжения с вычислительной машиной и блока сопряжения с периферийными абонентами являются информационными входами-выходами пульта.

Источники информации, принятые во внимание при экспертизе

1.Процессор ЕС 1060. Техническое описание. 1977.

2.Заявка ФРГ № 2725503,. кл. G 06 F 9/18, опублик. 1977 (прототип). 7 иаителями, отличающийс я тем, что, с целью повьшения быстродействия, в него введены блок приоритета, блок формирования прерываний, блок формирова1шя меток времени и блок сопряжения с периферийными абонентами, причем управляющий выход блока приоритета соединен с соответствуняцим входом блока one- . ративной памяти, разрешающий выход - с управлякшщм входом вычислителя, разрешающими входами первого и второго адаптеров, выход блока формирования прерываний подключен к управляющему входу вычислителя, маскирующий вход - к управляющему вь1ходу вычислителя, первый и второй запросные входы - соответственно, к В1лходам прерываний первого и второго адаптеров, третий, четвертый и пятый запроснь1е входы блока формирования прерываний соединены соответственно с выходами прерываний панели управления и индикации всех блоков сопряжения и блока формирования меток времени, управляющий вход которого соединен с управляющим выходом вычислителя, а управляюпщй выход - с тактовыми входами первого и второго адаптеров и всех блоков сопряжения, первый, второй и третий адресные входы блока приоритета соединены соответственно с адресными выходами вычислителя, первого и второго адаптеров, первый, второй и третий запросные входы блока приоритета соединены соответственно с управляющими выходами вычислителя, первого и второго адаптеров, третий информационный вход-выход которого соедифуе /

Vf.ff

83

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для сопряжения | 1983 |

|

SU1124277A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для ввода-вывода информации | 1985 |

|

SU1325489A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для управления обменом | 1978 |

|

SU750471A1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

Sff

l/ 8

/

ff7

8ff

фуг 7

Авторы

Даты

1982-03-07—Публикация

1980-06-25—Подача