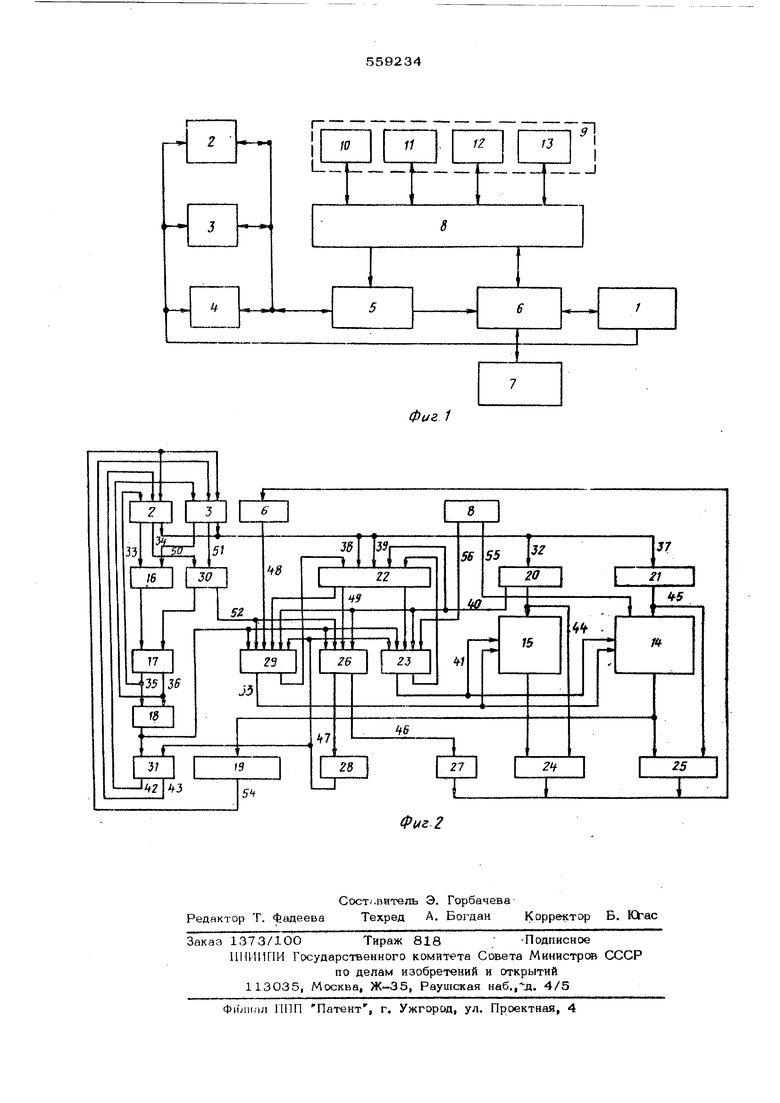

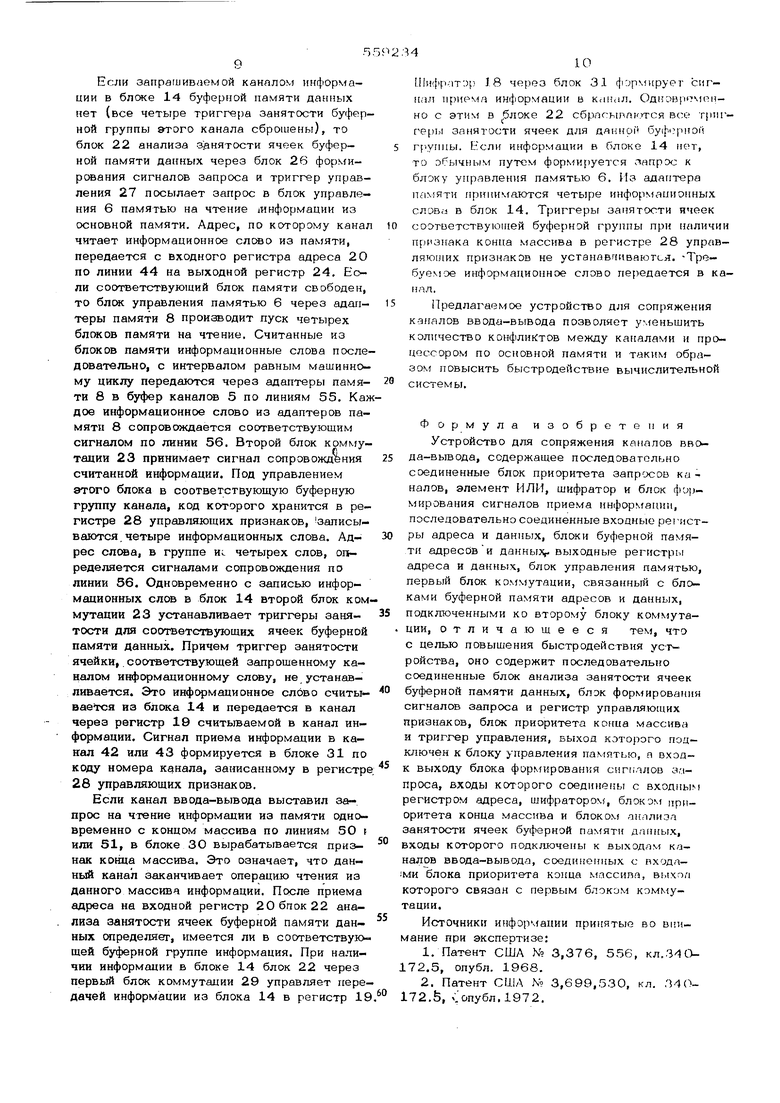

совдннанные блок анализа занятости ячеек буферной памяти данных, блок формирования сигналов запроса и регистр управляющих признаке блок приоритета конца ivfaccHsa и триггер управления, выход которого подкгаочен к блоку управления памятью, авход к .выходу блока формирования сигналов запр са, входы которого соединены с входным регистром ; адреса, шифратороМе блоком npsK орйтета конца массива и блоком анализа занятости ячеек буферной памяти данных, входы которого подключены к выходам каналов ввода-вывода, соединенных с входами блока приоритета конца массива, выход которого связан с первым блоком коммута- На фиг. 1 приведена блок-схемацифрово вычислительной системы| на фиг. 2 - струк турная схема устройства для сопрянчения к а на л ов вв ода-выв ода, Цифровая вычислительная система содер жит центральный вычислитель 1 (процессор), каналы ввода-вывода 2,3, и 4, уст ройство 5 для сопряжения каналов вводавывода, блок управления памятью,6, буферную память 7 nponeccopa, блок 8 сопряжения с основной памятью {адаптер памяти) и основную память 9, разделенную на четы ре логических блока памяти 10-13, Устройство 5 для сопряжения каналов ввода-вывода содержит блок 14 буферной памяти данных, блок 15 буферной памяти адресов, блок 16 приоритета запросов ка--налов, элемент ИЛИ 17, шифратор 18, регистр 19 считываемой в канал информации, входной регистр адреса 20, входной регистр данных 21;, блок 22 анализа занятости ячеек буферной .памяти данных Бторой блок коммутации 23, выходной регистр ад реса 24, выходной регистр данных 25, бло 26 формирования сигналов запроса, триггер управления 27, регистр 28 управляющих признаков, первый блок коммутации 29, бло 30 приоритета конца массива, блок 31 фор мирования сигналов приема информации. Назначение и принципы работы процессора, каналов ввода-вывода и оснсжной памят достаточно хорошо известны и не требуют д полнительных пояснений. В цифровую вычислительную систему включена буферная память 7 процессора объемом 8.192 байта. Цикл работы буферной памяти равен машинному циклу. Обмен информацией между основной и буферной памятью ведется блоками, содержащими четыре информационных слсжа, т.е. при любом -обращении от процессора на чтение информации, если этой инфор мации нет в буферной памяти процессора, из основной памяти считывается четыре информационных слова. Все эти четыре слова Запоминаются в буферной памяти процессора, а одно из них (заь зэшенное) отсылается в процессор. Основная память рабо1ает с четырехкратным чередованием (расслоением). Каналы ввода-вывода работают только с основной памятью, С буферной памятью 7 работает только процессор. Для уменьшения количества конфликтных ситуаций меж.цу каналами ввода вывода к npoueccopofvf по основной памяти в циф ровую вычислительнз э систему введено устройство для сопряжения каналов ввода-вы вода (буфер каналов) 5. При записи массива информации о-т канала ввода-вывода в основную память 9 буфер каналов 5 производит накопление трех информационных слов от этого канала, и как только от канала поступает четвертое информационное caoBDs буфер .- каналов выставляет в блок управления памятью 6 запрос на запись всех четырех слов. Блок управления памя. тыо 6 анализирует состояние блоков памя.ти 10-13 и, если соответствующие блоки памяти свободны, последовательно с интервалом равным машинному циклу запускает эти бпсоки. При этом информационные слова считываются из буфера каналов 5 и пересылаются в основную память 9. Устройство.работает следующим образом-. При чтении массива информации из основной памяти в каналы ввода-вывода по каждому запросу канала производится поиск запрошенной информации в буфере каналов. Если запрошенная информация находится в буфере каналов, то она считывается из.него и передается в канал. Если запрошенной информации в буфере каналов нет, то формируется запрос к блоку управления памятью 6, и, если соответствующие блоки памяти свободны, через время, равное времени выработки памяти, производится чтение четырех информационных слов. Эти слова с интервалом равным машинному циклу передаются из основной памяти 9 через адаптеры памяти 8 в буфер каналов 5. Запрошенное каналом слово непосредственно передается в канал, а остальные три слова запоминаются в. буфере каналов. Информа-. ция по следующему запросу от э-того же канала будет считываться уже из буфера каналов, если эта информация принадлежит тому же массиву. Таким образом, количество об- рашений в основную память от каналов ввода-вывода, а следовательно, и количество конфликтных ситуаций между процессором и каналами по основной памяти уменьшается в четыре раза. Подобный принцип реализации буфера каналов вoзмoжeн тoлькo для тех каналов, которые при передаче данных рабс1тают в моно польном режиме (селекторные и типлекснын каналы). Однако мультиплексной канал, который в режиме передачи дапЕилх может рабо-тать и не по последовагельЕ1Ы } адресам, имеет аначительног. ме 1ыние ско рости передачи данных, и количество этих каналов в вычислительной системе обычно. не превышает двух. Следовательно, отсутст вив буферизации для мультиплексного кана ла существенно не скажется на быстродей--стБИИ вычислительной системы. Адаптеры памяти 8 предназначены дпл Исправления работой логических блоков памяти 10-13, обнаружения и коррекции, ошибок основной памяти. Считанная из DCновной памяти информация через адаптеры памяти 8 передается в блок управления памятью 6 и буфер каналов 5. Информапиа на запись от буфера каналов в ocHOBiryio память передается через блок управпеция памятью. Блок 14 буферной памяти данных, (ск, фиг. 2) предназначен для временного хране ния данных, полуненнь х от каналов вводавывода, до передачи их в блок управлегшя памятью 6, или данных, считанных из адаптеров памяти 8 и еще не переданных в канал. Весь блок буферной памяти данных раз бит на буферные группы каналов. Блок содержит столько буферных групп, сколько кана™ пов ввода-вывода может быть максимально подключено к цифровой вычислительной систе- ме. Адрес буферной группы в блоке буферной памяти данных определяется код ом номера соответствующего канала. Каждая буферная груп па содержит четыре ячейки для хранения соответствующего информационного слова от канала. Адрес каждой ячейки буферной групп определяется двумя разрядами адреса основной памяти, полученными от канала по щин- ным линиям 32. Эти два разряда определяют также адрес .слова в блоке из четыре слов, которые будут получены ОТ канала и помещены в блок буферной памяти данных. Таким образом, если от седьмого канала поступил запрос на запись третьего слова из какого-либо блока массива информации, ТО это слово будет помещено по адресу III Л (в двоичном коде) блока буферной памяти данных. БЛОК 15 буферЕЮй памяти адресов предназначен для временного хранения адресов, получе ных от канапов ввода-вывода, до передачи их в блок упрпвпения памятью 6. Структура бпока буферной памяти адресов позволяет обеспечить временное хранение одно адресного слова для каждого канала. Таким образом, объем этого блока будет определяться максимальны числам подключаемых каналов ввода-вывуда. Указанные блоки должны работать с цик-; пом равнык (или меньшим) мащинному циклу и soryT быть реализованы на бьютродейстеующих микросхемах памяти. При обращении в основную (блоки 10-13) на запись или чтение информп.ции каналы ввода-вывода 2 и 3 выставляют запросы по щинным линиям 33 и 34 в буфер каналов 5. Поскольку каналы работают асинхронно относительно друг-друга и по отнощению к процессору, запросы от них -принимаются на блок 16 приоритета запросов каналов. Блок 16 определяет старщий из одновременно прищедших запросов, и через элемент ИЛИ 17 посылается в выбранный канал сигнал Ючиты вание данных по щинной линии 35 или 36. По этому сигналу соответствующий канал выставляет адрес и данные на щинные линии 32, 37, 38 и 39, и сбрасывает запр:ю по линии 33 или 34. Параллельно с вызовом адреса и данных от кано ла на щифраторе 18 формируется код номера канала, запрос которого выбран блоком приоритета 16, Адрес и данные от соответствующего канала приник1аются на входные регистры 20 и 21 и сохраняются вместе с кодом на шифраторе 18 до получения результатов аЕшлиза принятых от канала данных и адреса в блс«е 26 формирования сигнала запроса. Предположим, что канал ввода-вывода производит запись информации в память (единичный сигнал на линии 38), причем запись ведется в прямом направлении (т.е. в порядке возрастания адресов). Направление записи определяется кодом команды канала и передается в буфер каналов по шиняой линии 39. Блок 26 формирования сигналов запроса расщифровывает код в разрядах адреса, определяющих адрес слова в блоке обмена с памятькр на линии 4О. Если этот код отличен от ч// , то принятое информационное слово записывается в соот- ветству.ющую буферную группу по адресу, определяемому вторым блоком коммутации 23 и поступающему по линии 41 на первый адресный вход блока буферной памяти данных. Этот адрес формируется блоком 23 на кода на выходе шифратора 18 и кода адреса на линии 40. Адрес блока 15 буферной памяти адресов передается также по линии 41, но для адресации используется лишь та часть адреса, которая формируется шифратором 18. Одновременно с записью в блоки 14 и 15 устанавливается триггер занятости соответству.юи1ей : ячейки буферной группы и в канал выставляется сигнал приема информации по . линии 42 или 43. Этот сигнал фop fupyoтcл в блоке 31. Сигнал приема информации всспринимается каналом как конец обмена по данному запросу. Если код на линии 40 равен 11 ., это означает, что канал прислал последнее из четырех слов данного блока информации (т.е. в буфере каналов произошло накопление четырех информационных слов| трив буферной группе, четвертое - на входном регистре 21). В этом случае приня тые адрюс и данные переписьюаются с вход ных регистре 20 и 21 на соответствующие выходные регистры 24 и 25 по линиям 44 и 45. При этом блсж 26 форми рования сигнале® запроса по линии 46 устанавливает триггер управления 27, а код номера канала и двухразрядный код адреса слова переписываются в регистр 28 упраВ ляющих признаке по линии 47. Блсж уп равления памятью в в ответ на запрос выставпяет сигнал Принято по линии 48, если блок памяти, к которому обращается буфер каналов, свободен. По сигналу Принято первый блок коммутации 29 производит считывание трех слов, накопленнь х в блоке 14 буферной памяти данвыХд и передачу этих слов в блок управления памятью в с интервалом равным ма« шинному циклу, Адрес этих еле® в блгасе 41 определяется регистром 28 управляющих признаков, который через первьй блок ком мутации 29 формирует сигналы по второму адресному входу блока буфернойпамяти данных. Порядок считывания данных из бло ка 14 определяется первым блоком комму« тации 29. Если канал ввода вывода производит запись информации в обратном направленки т.е. в порядке убывания адресов (единичны сигнал на шинной линий 39) и код адреса на линии 40 отличай от 00, то принятое информационное Ciioeo записывается в соот ветегеуюшую буферную группу по адресуа определяемому вторым блоком коммутаций 23 и поступающему по линии 41 нб первы

адресный вход блока 14. Если код адреса на лннии 4О равен ООуто блок 22 запятос1И ячеек буферной памяти дан ных формирует сигнал по линш 49, который через блок 26 формирует запрос в блок уп. равления памятью 6. Одновременно с формированием запроса производится передача адреса и данных с входных регистров 20 и 21 на соотъет-ств тощие выходные : ре гистры 24 н 25 буфера каналев, В ааль нейшем работа буфера каналсв аналогична описанному выше.

В прсжессе записи массива информации от каналов ввода-вывода в осне®ную па мять адрас последнего слсжа из этого мао

Если запрашиваемая канапом информация на одйтся в блоке 14 буферной памяти аан ных, что подтЕерждается единичным состоянием соответствующего триггера занятости, формируется адрюс на линии 53 и первый блсж коммутации 29 обеспечивает считывание этой информадии в регистр 19 считываемой Б канал иаформации и передачу ее в канал по шинным-линкям 54. При этом триггер занятости соответствующей ячейки буферной группы сбрасгзгоается, В Йлсже 31 формирования сигналов приема информации с помощью шифратора 18 формируется сигнал Г1рие;ла информации по шинной ли1ти 42 или 43. снва может оказаться не кратным четырем слгжам, В этом случае канал одновременно с последним запросом должен выставить сигнал Конец массива . При наличии этого сигнала канал обратится к основной памяти и перепишет оставшуюся в блоке буферной памяти данных информацию в память. Такое сообщение передается от канала по шинной линии 50 или 51 одновременно с запросом по шинной линии 33 или 34. В ответ на запрос элемент ИЛИ 17 формирует сигнал считывания данных, который сбросит в канале запрос по шинной линии 33 или 34 и конец массива шинной линии 50 или 51 и устансжит адрес шинной линии 32 и дан ные шинных линий 37 н 38, на выходной шине. Блок 30 формирует признак конца массива на линии 52. После приема данных н адреса на входные регистры при нбитйчии сигнала на линии 52 блсяс 26 формирования сигналов запроса устанавливает код номера канала в регистре 28 управляющих признаков, запрос в основную па мять на триггер 27 и разрешает прием данных и адреса с входных регистре 20 и 21 по линиям 44 и 45 на выходные регистры 24 и 25„ Обработка запроса от буфера канале© 5 а блоке управления памятью 6 и порядоа считывания информации из блока 14 буферной памяти аналогичны описанному выше. Рассмотрим процесс чтения информации ив основной памяти в канал ввода-вывода. Процесс установки приоритета запроса и считьюания данных и адреса от канала не отличается от описанного выше. Пеюле приема н адреса на входные регистры блсж 22 анализа занятости ячеек буферной памяти данных просматривает признак запис чтения на линии 38,Ёсли на линии 38 нулевой сигнал (кинал читает инфсрмацизо из памяти) блок 22 анализирует состояние триггере© занятости всех четырех1ячеек буферной группы соответствующего канала. Если запрагииваемой каналом информации в блоке 14 буферной памяти данных нет (все четыре триггера занятости буферной группы этого канала сброшены), то блок 22 анализа з анятости ячеек буфер- ной памяти данных через блок 26 форк1ирования сигналов запроса и триггер управления 27 посылает запрос в блок управления 6 памятью на чтение информации из основной памяти. Адрес, по которому канал читает информационное слсжо из памяти, передается с входного регистра адреса 20 по линии 44 на выходной регистр 24, Если соответствующий блок памяти свободен, то блсж управления памятью 6 через адаптеры памяти 8 производит пуск четырех блоков памяти на чтение. Считанные из блоков памяти информационные слова после довательно, с интервалом равным машинному циклу передаются через адаптеры памяти 8 в буфер каналсж 5 по линиям 55, Каж дое информационное слово из адаптеров памяти 8 сопровождается соответствующим сигналом по линии 56, Второй блок коммутации 23 принимает сигнал сопровождения считанной информации. Под управлением этого блока в соответствующую буферную группу канала, код которого хранится в регистре 28 управляющих признаков, -записываются, четыре информационных слова. Адрее слсжа, в группе ис четырех слов, определяется сигналами сопровождения по линии 56. Одновременно с записью информационных слов в блок 14 второй блок ком мутации 23 устанавливает триггеры занятости для соответствующих ячеек буферной памяти данных. Причем триггер занятости ячейки,. соответствующей запрошенному каналом информационному слову, не устанавливается. Зто информационное слово считы- вается из блока 14 и передается в канал через регистр 19 считываемой в канал информации. Сигнал приема информации в канал 42 или 43 формируется в блоке 31 по коду номера канала, занисанному в регистр 28 управляющих признаков, Если канал ввода-вывода выставил запрос на чтение информации из памяти одновременно с концом массива по линиям 50 t или 51, в блоке 3О вырабатывается призкак конца массива. Это означает, что данный канал заканчивает операцию чтения из данного массива информации. После приема адреса на входной регистр 20 бпок 22 анализа занятости ячеек буферной памяти данных отределяет, имеется ли в соответствузо щей буферной группе информация. При наличии информации в блоке 14 блок 22 через первьй блс« коммутации 29 управляет пере дачей информации из блока 14 в регистр 19 Нифратэр 18 через блок 31 ф:;р нруег сигнал приема информации в , Однэир(7мпино с этим в .блоке 22 сбрасывпк.п-ся все триггеры занятости ячеек для даннр бу(1О|-|ЦОй rfiyiiiibi. Если информации в блоке 14 нет, то обычным путем формируется запрос к блоку управления памятью б. Из адаптера памяти приии таются четыре информационных спова в блок 14, Триггеры загштости нчеек соответствующей буферной группы при наличии признака конца NjaccHBa в регистре 28 управляюишх признаков не устанавпнваютсл, -Требуемое информационное слово передается в капап. Предлагаемое устройство для сопряжения каналов ввода-вывода позволяет уменьшить количество конфликтов между ка1 алами и процессором по основной памяти и таким образом повысить быстродействие вычислительной системы. Формула изобретения Устройство для сопряжения каналов ввода-вывода, содержащее последовательно соединенные блок приоритета запросов каналов, элемент ИЛИ, шифратор и блок формирования сигналов приема информации, последовательно соединенные входные регистры адреса и данных, блоки буферной памяти адресов и данны выходные регистры адреса и данных, блок управления памятью, первый блок ко {Ч5утации, связанный с блоками буферной памяти адресов и данных, подключенными ко второму блоку коммутации, отличающееся тем, что с целью повышения быстродействия ус-тройства, оно содержит последовательно соединенные блсж анализа занятости ячеек буферной памяти данных, блок формирования сигналов запроса и регистр управляющих признаков, блок приоритета KOPiua массива и триггер управления, выход которого подключен к блоку управления памятью, а входк выходу блока фt)p fиpoвaнкя сигналов запроса, входы котОрого соединены с входным регистром адреса, шифратором, блоком приоритета конца массива и блоком анализа занятости ячеек буферной данных, ходы которого подкаюченьг к выходам каналов ввода-вывода, соединегп1ых с пхода- мк блока приоритета конца массива, выхол которого связан с первым блоком KOMNtyации. Источники информации принятые во вниание при экспертизе: 1,Патент США № 3,376, 556, кл.З-Ю72.5, опубл, 1968, 2,Патент США № 3,699,530, кл. Л-1О72,ё, :опубл, 1972,

фиг 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1977 |

|

SU670936A1 |

| Устройство для сопряжения основной памяти цифровой вычислительной машины с каналами ввода-вывода | 1977 |

|

SU689438A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

Авторы

Даты

1977-05-25—Публикация

1975-04-10—Подача