(5А) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1652982A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

1

I Изобретение относится к вычисли-Л, тельной технике и может быть использовано в полупостоянных запоминающих устройствах специализированных процессоров и вычислительных систем, а также для хранения знаков цифровой индикации, защиты, шифрования и передачи дискретной информации.

Известно запоминающее устройство, содержащее регистры сдвига, состоящие из последовательно соединенных . элементов памяти tl.

Недостатком известного устройства является наличие в нем большого количества элементов памяти, что усложняет устройство и приводит к снижению его информационной емкости и надежности его работы.

Известно также запоминающее устройство, содержащее шины тактовых импульсов, регистр .сдвига, группы элементов И по штук в каждой группе, где -I-- разрядность отрезков слов, образующих считанное слово 12.1.

Недостатком известного устройст- ва является его малая информационная емкость, вызванная наличием в нем большого количества элементов памяти. Это приводит также к снижению надежности его работы.

Наиболее близким по технической сущностей к изобретению является запоминающее устройство, содержащее регистры сдвига, схему совпадения, дополнительный регистр, группы элементов И, другую группу элементов И, выходами соединенных со входами элемента ИЛИ, RS-триггер, шину тактовых импульсов и шину записи

Недостатком известного устройства является наличие в его регистрах сдвига большого количества элементов памяти. Это приводит к тому, что для его реализации требуются большие аппаратурные затраты, усложняющие устройство и приводящие к снижению надежности работы устройства.

39

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем НТО в запоминающее устройство, содержащее сдвиговый регистр, выходы которого подключены к первым входам соответствующих элементов И первой труппы, а первый вход - к выходу схемы сравнения, первый элемент ИЛИ, входы которого подключены к выходам элементов И второй группы, а выходы - к первому входу триггера, дополнительно введены элемент задержки, выход которого подключен к первому входу схемы сравнения и к второму входу триггера, второй элемент ИЛИ, 1выход которого подключен к входу элемента задержки, третий элемент ИЛИ, выход которого подключен к второму входу сдвигового- регистра, элементы И, выход первого из которых подключен к третьему входу сдвигового ре-, гистра, выход второго элемента И .подключен к первому входу третьего элемента ИЛИ, первый вход первого элемента И подключен к выходу третьего элемента И, первый вход которого подключен к первому выходу триггера, первый вход второго элемента И подключен к выходу четвертого элемента И, первый вход которого подключен к второму, выходу триггера, второй вход первого элемента И подключен к второму входу второго элемента И и является так-товым входом устройства,Второй вход третьего элемента И подключен к второму входу четвертого элемента И и является управляющим входом устройства, входной информационный регистр, выход которого подключен к второму входу схемы сравнения, а вход подключен к второму входу третьего элемента ИЛИ и является информационным входом устройства, выходной информационный регистр, входы которого подключены к выходам элементов И первой группы, а выходы выходного информационного регистра являются информационными выходами устройства, элементы И третьей группы, первые входы которых подключены к второму входу первого элемента И, выходы .элементов И третьей группы подключены к первым входам соответствующих элементов И второй группы, адресные счетчики, первые входы которых являются адресными входами устройства, вторые входы адресных счетчиков подключены к выходам соответствующих эле

234

элементов И третьей группы, формирователи сигнала переполнения, вход каждого из которых подключен к выходу соответствующего адресного счетчика и к второму входу соответствующего элемента И второй группы, управ. ляющий регистр,, входы которого подключены к выходам формирователя сигналов переполнения, к входам второго

O элемента ИЛИ и к вторым входам соответствующих элементов И второй группы, выходы первой группы управляющего регистра подключены к вторым входам соответствующих элементов И третьей

5 группы, выходы второй группы управляющего регистра подключены к третьим входам соответствующих элементов И третьей группы.

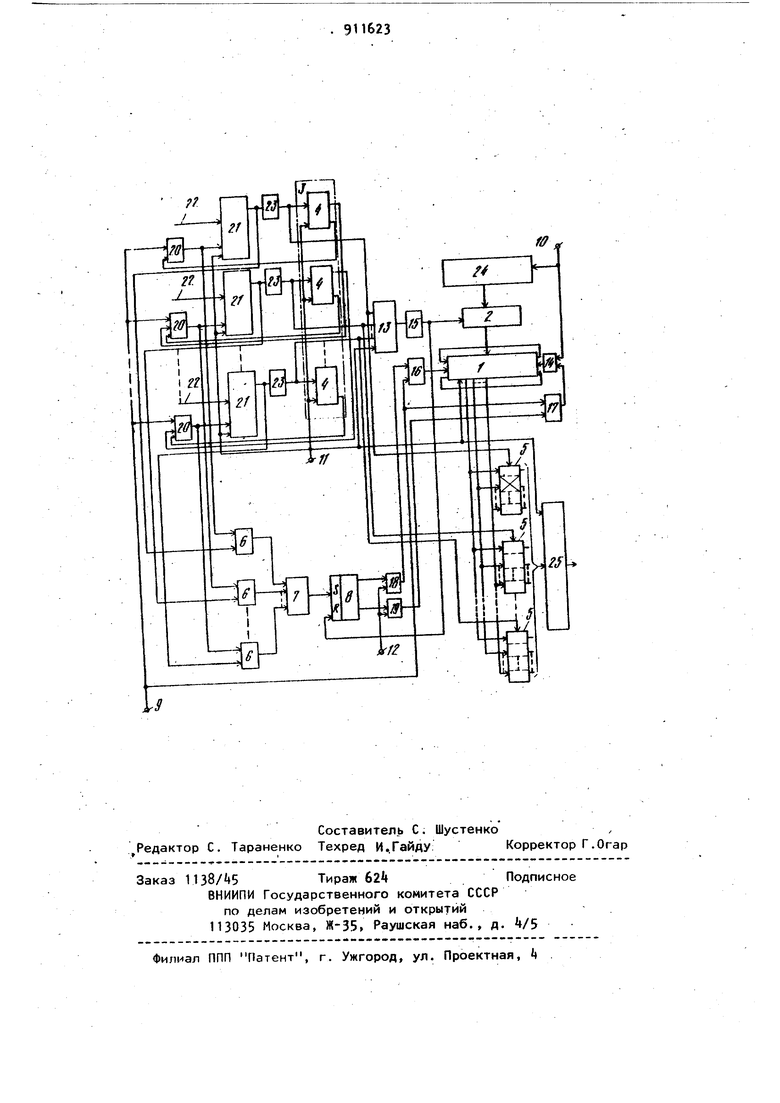

На чертеже представлена функциод нальная схема предлагаемого устройства.

ij. . Устройство содержит сдвиговой регистр 1, схему 2 сравнения, управляющий регистр 3 с триггерами ,первую группу элементов И 5, вторую группу элементов И 6, первый элемент ИЛИ 7, триггер 8, тактовый вход 9, информационный вход 10, вход 11 начальной установки, вход 12 управлений реверсом регистра сдвига, элементы ИЛИ 13и И, элемент 15 задержки, элементы И 16-19 третью группу элементов И 20 по числу выбираемых отрезков слов, образующих одно слово, адресные счетчики 21, информационные входы которых подключены к соответствующим адресным входам 22, информационные формирователи 23 сигналов переполнения, входной регистр

2, входной информационный, регистр

Так, например, в последовательности 0000110010111101 при объединении в ней по четыре разряда со сдви пом вправо на один разряд с охватом в общее кольцо будут расположены числа 0,1,3.6,12,9,2,5,11,7,15,1,13, 10,t,8.

Формирование уплотненной последовательности производится с помощью вычислительной машины по специальной программе.

Адресом отрезка слова является . его номер в записи последовательности. Двоичные счетчики 21 адреса вы полнены с числом разрядов, равным г llogrj M g , где М - количество г.-раз,рядных отрезков слов, хранящихся в регистре сдвига.

Количество адресных счетчиков 21, элементов И 20 третьей группы, триггеров k дополнительного регистра 3 элементов И 5 первой группы и элементов И 6 второй группы в устройстве определяется числом выбираемых С-разрядных отрезков слов q, образующих п-разрядное слово при считывании

.п q -р- .

Рациональное число счетчиков в устройстве с указанными элементами их обслуживания определяется конкретным вариантом использования запоминающего устройства. Каждому полноразрядному слову информации по п разрядов в каждом слове соответствует определенный адрес, состоящий из г-разрядных групп по числу выбираемых отрезков слов, образующих одно слово.

Формирователи сигналов переполнения счетчика адреса в простейшем случае представляют собой дифференцирующие цепочки с усилителями сигналов, формирующими импульсные сигналы вмомент перехода триггеров старших разрядов счетчиков адресов из состояния 1 в О ,.

Входной информационный регистр 24 позволяет уменьшить период обращения к памяти так как после выборки отрезка слова по. заданному г-разрядному адресу возможно считывание очередного отрезка слова, не ожидая восстановления исходного сбстояния содержимого сдвигового peгиctpa 1. Дальнейшее сокращение периода обращения к памяти достигается за счет реверсивного изменения направления перемещения информации в регистре. сдвига. Для этого производится анализ старшего разряда адреса в каждом счетчике 21..

Единичному состоянию триггера старшего разряда счетчика адреса соответствуют старшие адреса в половине, хранящейся в сдвиговом регистре

1 последовательности, а нулевому состоянию триггера старшего разряда счетчика адреса соответствуют младшие адреса в половине последовательности. В первом случае целесообразно направление перемещения содержимого регистра 1 сдбига слева направо-,а во втором случае - в противоположном направлении.

0 Анализ содержимого триггеров старших разрядов счетчиков 21 адресов и реверсивное переключение перемещения содержимого регистра 1 сдвига обеспечивается с помощью .группы элементов

5 И 6, первого элемента ИЛИ J, третьего элемента ИЛИ k, триггера 8, элементов И 16-19.

Устройство работает следующим образом.

0 Перед обращением к запоминающему устройству сигналом по данным на вход 11 начальной установки устанавливаются в исходное (нулевое) состояние адресные счетчики 21, триггеры

5 управляющего регистра 3, сдвиго вый регистр 1, выходной информационный регистр 25 и триггер 8. .

При записи информации в устройство по информационному входу VO уплотненная последовательность последовательным кодом заносится во входной информационный регистр 2, а через элемент ИЛИ Ik в сдвиговый регистр 1. Считывание подноразрядного слова

информации производится по заданному полноразрядному адресу, состоящему из г-разрядных групп, которые поступают по адресным шинам 22 и распределяются по соответствующим

0 счетчикам 21 адресов (синхронизация момента занесения адреса в счетчики адреса на чертеже не показана).

После поступления в устройство полноразрядного адреса считываемого

слова в шину 12 управления реверсом регистра сдвига подается сигнал обращения к памяти, которым открываются по управляющему входу элементы

И 18 и 19.

При исходном состоянии триггеров k управляющего регистра 3 и триггера 8 удержи-вается в открытом состоянии первый элемент И 20 третьей группы элементов, четвертый элемент И 19 и второй элемент И 17 при этом задается перемещение информации в сдвиговом регистре 1 в направлении справа налево и разрешается поступление тактовых импульсов на его второй вход и на счетный вход первого адресного счетчика 21. При нулевом состоянии триггера старшего разряда первого адресного счетчика 21 первый элемент И 6 второй группы будет закрыт, тогда три|- гер 8 останется в исходном состоянии при этом сохраняется ранее установленное направление перемещения содержимого сдвигового регистра 1. ,При единичном состоянии триггера старшего разряда первого адресного счетчика 21 первый элемент И 6 второй группы будет открыт, тогда первым тактовым импульсом, поступающим на счетный вход первого адресного счетчика 21 через открытый первый элемент И 20 третьей группы, первый элемент И 6 второй группы и первый элемент ИЛИ 7, устанавливается в единичное состояние триггер 8, при этом закрываются элементы И 19 и 17 и открываются элементы И 18 и 16 и устанавливается перемещение информации в сдвиговом регистре 1 в направлении слева направб и разрешается поступление тактовых импульсов на третий вход сдвигового регистра 1.По каждому тактовому импульсу, поступающему на тактовый вход 9 на счетный вход первого адресного счетчика ведется счет тактовых импульсов. Одновременно по каждому тактовому импул су производится сдвиг хранящейся в сдвиговом регистре 1 последовательности на один разряд вправо или влево в заеисимости от состояния триггера 8. В момент.времени, когда код г-разрядного считываемого отрезг ка слова содержимого сдвигового регистра 1 находится в разрядах регист ра, имеющих выходы в соответствии с заданным адресом отрезка слова, происходит обнуление первого адресного счетчика 21, при этом его формироватрпк rtinnMMnvpT гигндп прпрппп- ( тель 23 формирует сигнал перепол нения счетчика адреса, который устанавливает в. единичное состояние первый триггер А управляющего регистра 3. Одновременно этот сигнал поступает на управляющий вход первой группы элементов И 5 и обеспечивает выборку 1-разрядного отрезка слова из регистра 1 сдвига и занесение его на первые разрядов выходного информационного регистра 25. Сигналом логической 1 с прямого выхода первого триггера управляющего регистра 3 открывается второй элемент И дополнительной группы элементов И 20, и сигналом переполнения счетчика через элемент ИЛИ 13, элемент 15 задержки и схему 2 сравнения производится перезапись информации из входного информационного регистра 2 в сдвиговый регистр 1 и установка в исходное состояние (сброс) триггера 8. Сигналом логического О с(инверсного выхода первого триггера Ц управляющего регистра 3 закрывается первый элемент И 20 третьей группы. Далее производится обработка второго г-разрядного адреса аналогичным образом, при этом в отличие от указанного в работе задействованы второй адресный счетчик 21, второй элемент И 20 третьей группы, второй элемент И 6 второй группы, формирователь 23 сигнала переполнения второго адресного счетчика, второй триггер дополнительного управляющего регистра 3- В результате тактовые импульсы подаются на второй адресный счетчик 21. Сформированный формирователем 23 второго адресного счетчика 21 сигнал переполнения счетчика устанавливает в единичное состояние второй триггер управляющего регистра 3. поступает на управляющий вход соответствуюдих элементов И 5 первой группы и обеспечивает выборку второго С разрядного отрезка слова по заданному адресу из сдвигового регистра 1 и занесение его на вторые v разрядов входного информационного регистра 25. после чего этим же сигналом через элемент ИЛИ 13 и элемент 15 задержки устанавливается в исходное состояние Триггера 8, а через схему 2 сравнения вновь производится перезапись информации из входного информационного регистра 2Ц в сдвиговый регистр 1. Сигналом логическойс прямого выхода второго триггера ч управляющего регистра 3 открывается Очередной (третий) элемент И 20 третьей группы, а сигналом логического О с инверсного выхода этого же триггера закрывается второй элемент И 20 третьей группы, тем самым запрещается подача тактовых импульсов в предыдущие адресные счётчики 21, ,по адресам которых была произведена выборка отрезка слова по заданному очередному адресу отрезка слова последующего счетчика 21 адреса. После завершения выборки последнего {-разрядного отрезка слова в

выходном информационном регистре 25 будет сформировано считанное из устройства п-разрядное слово, которое к моменту очередного обращения к памяти из выходного регистра передается потребителю;

Таким образом, предлагаемое устР0ЙСТВО позволяет производить считывание слов информации с числом разрядов п, кратным f-разрядным отрезком слов.

Так, например, при выборке четырехразрядных отрезков слов, можно формировать при считывании восьмиразрядные, двенадцатиразрядные или шестнадцатиразрядные слова информации .

Кроме того, устройство обеспечивает выборку слов переменного формата, в данном случае отдельные счетчики адресов из группы счетчиков и элементы, связанные с ними, в работе не задействуются, при этом разрядность считанных слов уменьшается дискретами по С разрядов.

Техни-ческий эффект от использования предлагаемого устройства в отличие от известного заключается в упрощении устройства за счет уменьшения числа элементов памяти при хранении в нем одного и того же объема информации .

Формула изобретения

Запоминающее устройство, содержащее сдвиговый регистр, выходы которого подключены к первым входам соответствующих элементов И первой группы, а первый вход - к выходу схемы сравнения, первый элемент ИЛИ, входы которого подключены к выходам элементов И второй группы, а выходы к первому входу триггера,о т л и чающееся тем, что, с целью упрощения устройства, оно содержит элемент задержки, выход которого подключен к первому входу схемы сравнения и к второму входу триггера, второй элемент ИЛИ, выход которого подключен к входу элемента задержки, третий элемент ИЛИ, выход которого подключен к второму входу сдвигового регистра, элементы И, выход первого из которых подключен к третьему входу сдвигового регистра, выход t второго элемента И подключен к пёр вому входу третьего элемента ИЛИ, первый вход первого, элемента И подключен к выходу третьего элемента И, первый вход которого подключен к пев,вому выходу триггера, первый вход второго элемента И подключен к выходу четвертого элемента И, первый вход которого подключен к второму 5 выходу триггера, второй вход первого элемента И подключен к второму входу второго элемента И и является тактовым входом устройства, второй вход третьего элемента И подключен

0 к второму входу четвертого элемента И и является управляющим входом устройства, входной информационный регистр , выход которого подключен к второму входу схемы сравнения, а

5 вход подключен к второму входу

третьего элемента -ИЛИ и является информационным входом устройства, выходной информационный регистр, входы которого подключены к выходам элементов И первой группы, а выходы выходного информационного регистра являются информационными выходами устройства, элементы И третьей группы , первые входы которых подключены

5 к второму входу первого элемента И, выходы элементов И третьей группы подключены к первым входам соответствующих элементов И второй группы, адресные счетчики, первые входы ко- .

0 торых являются адресными входами устройства, вторые входы подключены к выходам соответствую1цих элементов И третьей группы, формирователи сигналов переполнения, вход каждого из которых подключен к выходу соответствующего адресного счетчика и к второму входу соответствующего элемента И второй группы, управляющий регистр, входы которого подключены к выходам формирователя сигналов переполнения, к входам второго элемента ИЛИ и к вторым входам соответствующих элементов И второй группы, выходы первой группы управляющего регистра подключены к вторым входам соответствующих элементов И третьей группы, выходы второй группы управляющего регистра подключены к третьим входам соответствующих элементов И третьей группы.

Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1982-03-07—Публикация

1980-08-25—Подача