Изобретение относится к вычислительной и цифровой измерительной технике.

Известен аналого-цифровой преобразователь, содержащий блок упра.вления, 1ВЫХОД которого является выходом .аналого-цифрового преобразователя и соединен со входом преобразователя код-аналог, выход которого соединен с первым входом компаратора,второй вход которого является входом аналого-цифрового преобразователя выход компаратора соединен со входом блока управления 1,

Недостатком данного аналого-цифрового преобразователя является сложный метрологический контроль линейности выходной характеристики.

Цель изобретения - упрощение.метрологического контроля линейности выходной характеристики.

Указанная цель достигается тем, что в аналого-цифровой преобразователь содержащий блок сравнения, первый вход которого соединен с входной шиной, второй вход - с выходом цифроаналогового преобразователя, а выход - с первым входом блока управления, дополнительно введены блок свертки кода,блок анализа кода.

блок контроля, при этом выход блока сравнения соединен с первым входом блока контроля, выход блока анализа

с кода соединен с первым входом блока, свертки кода и ссэвторым входом блока управления, выход блока свертки кода соединен с входом цифроаналогового преобразователя, с первым вхо4Q дом блока анализа кода и первой выходной шиной, второй вход блока свертки кода соединен с цервым выходом блока управления,второй выход которого соединен со вторым входом блока анализа,кода, второй вход блока

5 контроля соединен с третьим выходом блока управления, а его выход со второй выходной шиной аналогоцифрового преобразователя.

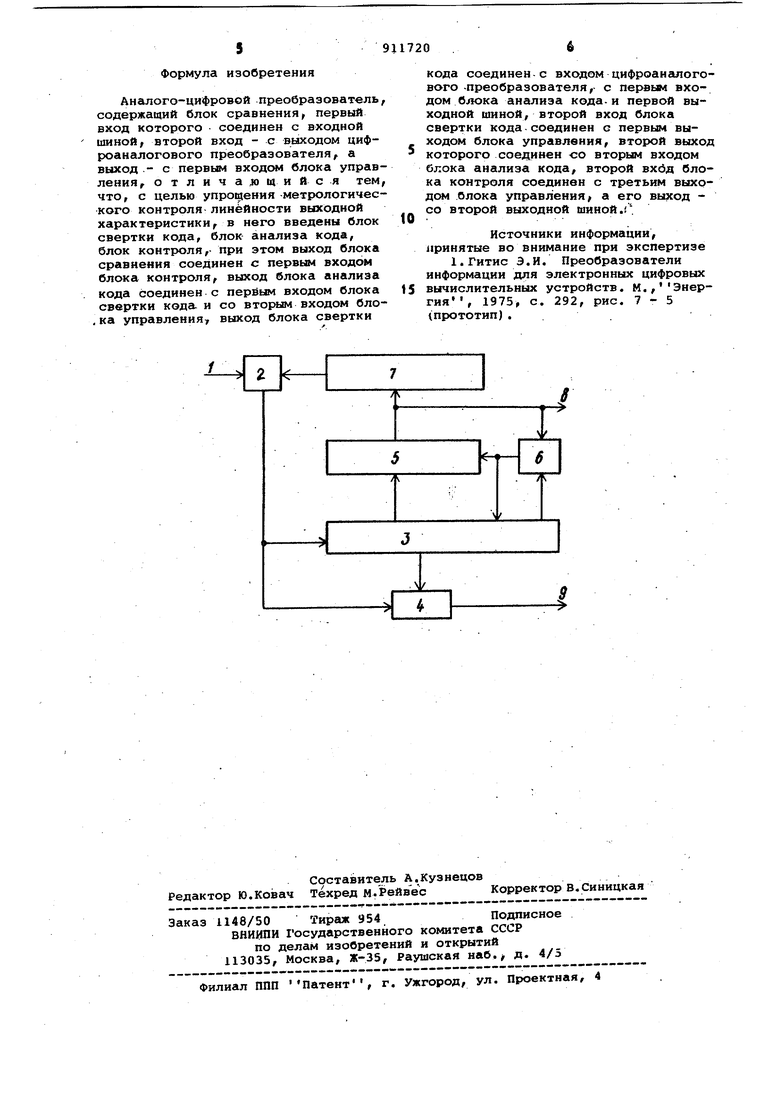

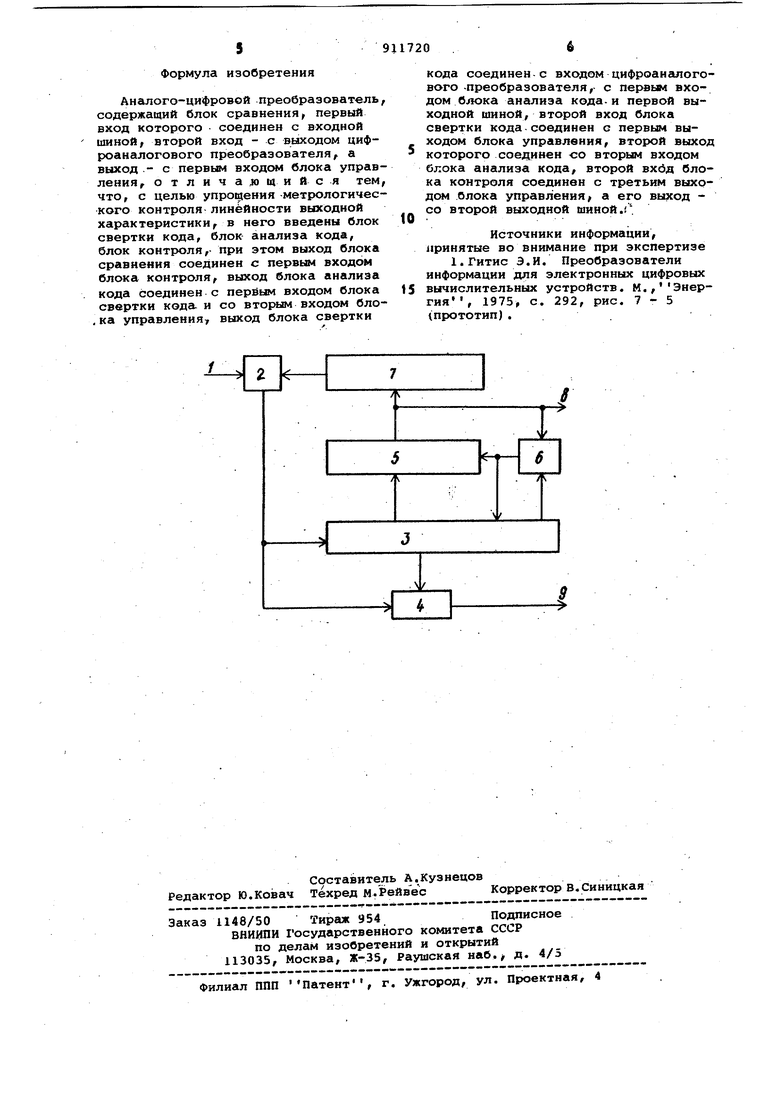

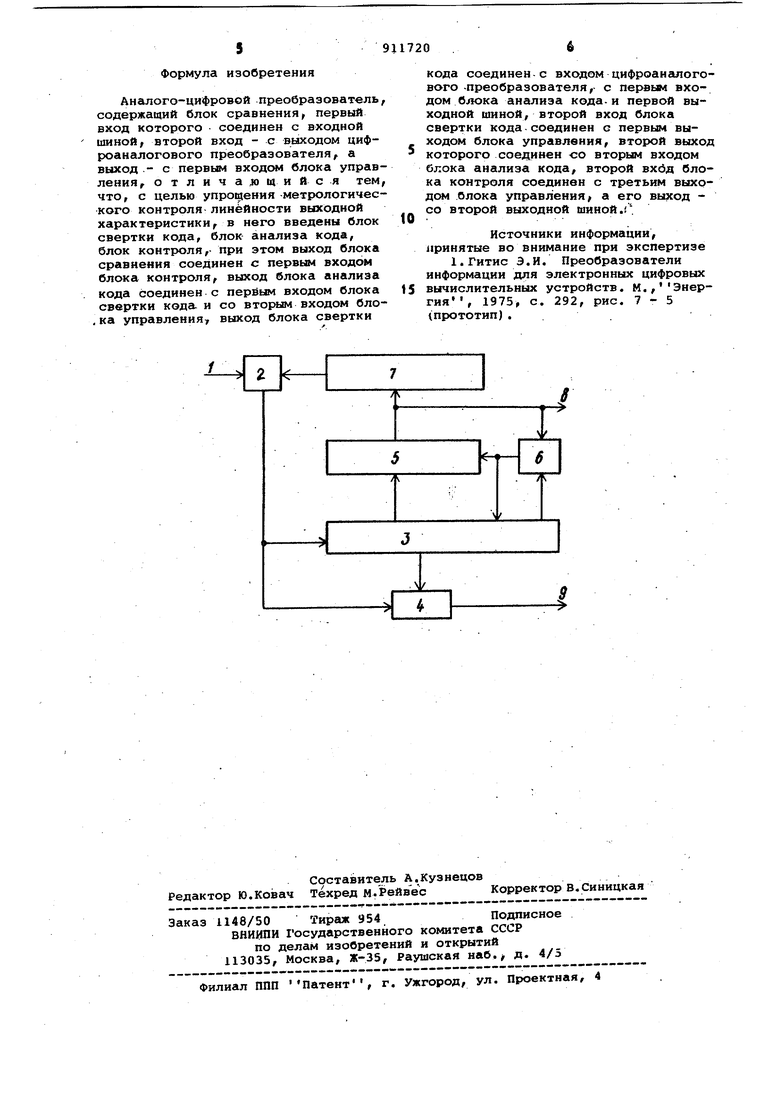

На чертеже представлена функциональная схема аналого-цифрового преобразователя.

Схема содержит входную шину 1 аналого-цифрового преобразователя,

25 блок 2 сравнения, блок 3 управления, блок 4 контроля, блок 5 свертки.кода, блок 6 анализа кода, цифроаналоговый преобразователь 7, информационный выход 8 аналого-цифро30 ;вого преобразователя и контрольной выход 9 аналого-цифрового преобразователя. Первый вход блока 2 сравнения соединен с входной шиной 1 аналогоцифрового преобразователя, на которую подается преобразуемая аналоговая величина А. Выходной сигнал блок 2 сравнения поступает на первый вход блока 3 управления, обес печивающего работу устройства, и на первый вход блока 4 контроля, формирующего сигнал, свидетельствующий о несоответствии весов разрядов цифроаналогового преобразователя 7 требуемым значениям. Выход блока 4 конт роля является контрольным выходом 9 аналого-цифрового преобразователя. Первый, второй и третий выходы блок 3управления соединены соответствен но с первым входом блока 5 свертки кода, .со BTOptiw входом блока 6 анализа кода, управляющего сверткой в блоке 5, и со вторым входом блока 4контроля, Выход блока 6 анализа кода соединен со, вторым входом блока 5 сверггки кода и со вторым входом блока 3 управления. Выход блока 5 свертки кода является информационным выходом 8 аналого-цифрового преобразователя и соединен со входом цифроаналогового преобразователя 7 и с первым -входом блока 6 анализа кода. Выходной сигнал цифроаналогового преобразователя -7 поступает на второй вход блока 2 сравнения. Контроль линейности выходной характеристики аналого-цифрового преобразователя происходит в процессе преобразования входной аналоговой величины в код иррациональным основанием. Преобразователь работает следующим образом. Со входной шины 1 преобразовател преобразуемый аналоговый сигнал А подается на первый вход блока 2 сравнения, на второй вход которого поступает компенсирующий аналоговый сигнал A)f,,формирующийся на выходе цифроаналогового преобразователя 7 Разность вышеуказанных величин ЛА,; преобразуется в код с А иррациональным основанием по метод последовательного счета с помощью блока 2 сравнения, блока 3 управле НИН и блока 5 свертки кода. При э блок 5 свертки кода работает в реж ме счета импульсов, причем счет ос ществляется с-помощью операции све ки. Управление процессом счета импульсов производится с помощью б ка б анализа кода. Выполнение опер ции свертки в каждый последующий i-й разряд производится после уста новки в единичное состояние (i-l)младших разрядов. Цифровой код с выхода блока 5 вертки кода поступает на вход цифоаналогового преобразователя 7, на выходе которого появляется аналоговый эквивалент данного кода. После выполнения свертки кода в i-й разряд происходит срабатывание блока 2 сравнения и по команде блока 3 управления младший разряд блока 5 свертки кода устанавливается в нулевое состояние. Если при зтом выходной сигнал блока 2 сравнения не изменится, то на выходе блока 4 контроля появляется сигнал, свидетельствующий об отклонении веса1-го разряда от требуемого значения, определяемого рекуррентным соотношением. Если блок 2 сравнения изменил свое состояние, то величина отклонения веса 1-го разряда от требуемого значения пренебрежительно мала (меньше меньшего кванта). Процесс преобразования на этом заканчивается. Если, посла выполнения операции свертки в i-й разряд блок 2 сравнения не меняет своего состояния, то производится дальнейшее уравновешивание входной величины А выходным сигналом А It цифроаналогового преобразователя 7 до срабатывания блока 2 сравнения. После срабатывания блока 2 сравнения по команде блока 3 управления производится последовательная свертка кода (со старших разрядов) в блоке 5 свертки кода. Если после выполнения операции свертки блок 2 сравнения изменил свое состояние,то производится установка в единичное состояние младшего разряда блока 5 свертки кода. При этом, если блок 2 сравнения не изменил свое состояни на выходе блока 4 контроля появляется сигнал, свидетельствукяций о несоответствии весов разрядов цифроаналогового преобразователя 7 требуемым значениям. Если после оператдаи свертки блок 2 сравнения не изменил своего состояния, то производится установка в нулевое состояние младшего разряда блока 5 свертки кода. При этом, если блок 2 сравнения не изменил свое состояние, на выходе блока 4 контроля появляется сигнал, свидетельствующий о несоответствии весов разрядов цифроаналогового преобразователя 7 требуемьм значениям. . введениеблоков свертки кода, анализа кода, контроля и.связей позволяет непосредственно в проце.ссе основного преобразования.вести оперативный метрологический контроль линейности выходной характеристики аналого-цифрового преобразователя во всем диапазоне входного сигнала.

Формула изобретения

Аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого соединен с входной шиной; второй вход - с выходом цифроаналогового преобразователя а выход .- с первым входом блока управления отличающийся тем, что, с целью упрок|ения -метрологического контроля линейности выходной характеристики, в него введены блок свертки кода, блок анализа кода, блок контроля,- при этом выход блока сравнения соединен с первым входом блока контроля, выход блока анализа кода соединен с перйым входом блока свертки кода и со вторым входом бло, ка управления выход блока свертки

кода соединен-с входом цифроаиалогового -преобразователя, с первым входом блока анализа кода.и первой выходной шиной, второй вход блока свертки кодасоединен с первым выходом блока управления, второй выход которого соединен со вторым входом блока анализа кода, второй вхбд блока контроля соединен с третьим выходом блока управления, а его выход со второй выходной шиной..

Источники информации, принятые во внимание при экспертизе

1. Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М.,Энергия , 1975, с. 292, рис. 7-5 {прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU928632A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU783979A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

Авторы

Даты

1982-03-07—Публикация

1980-04-02—Подача