10

1279064

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

Цель изобретения - повышение достоверности аналого-цифрового преобразователя за счет более эффективного метрологического контроля,

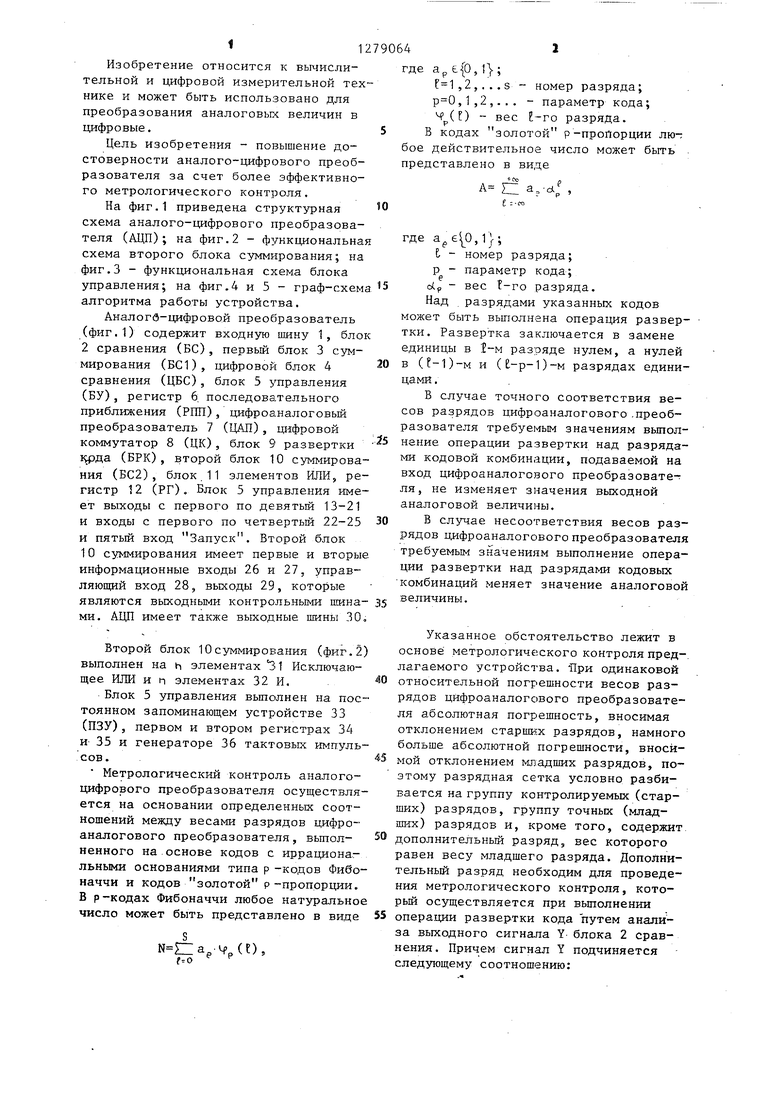

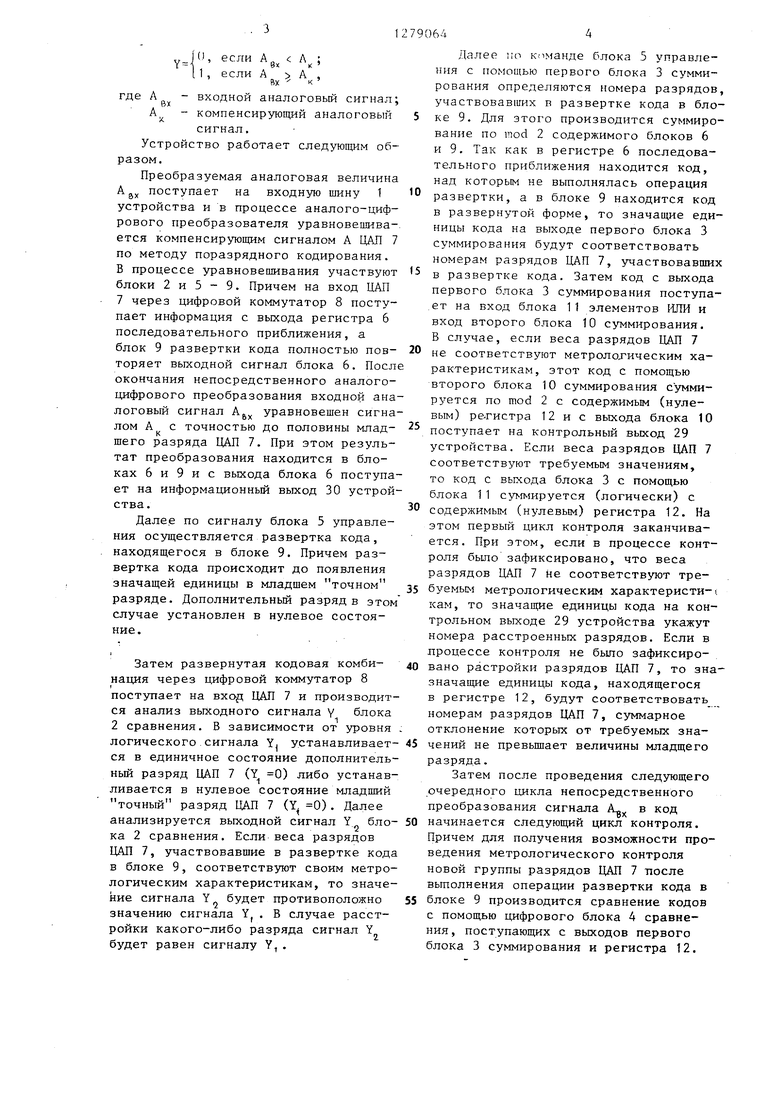

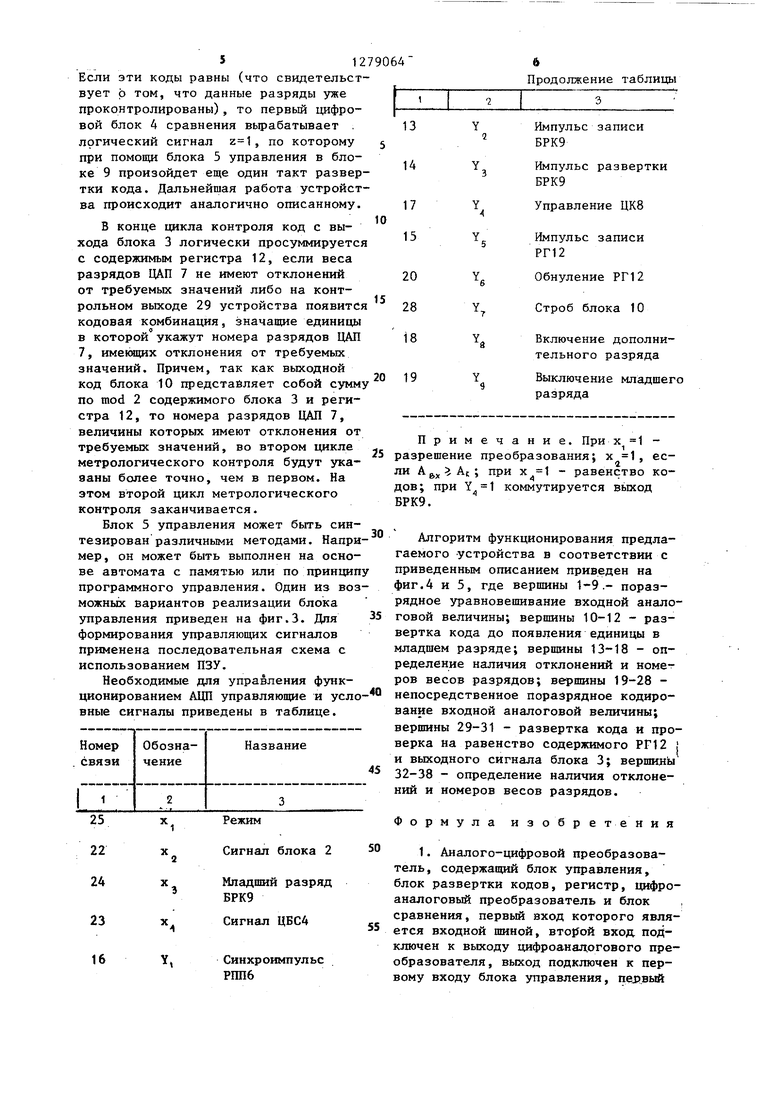

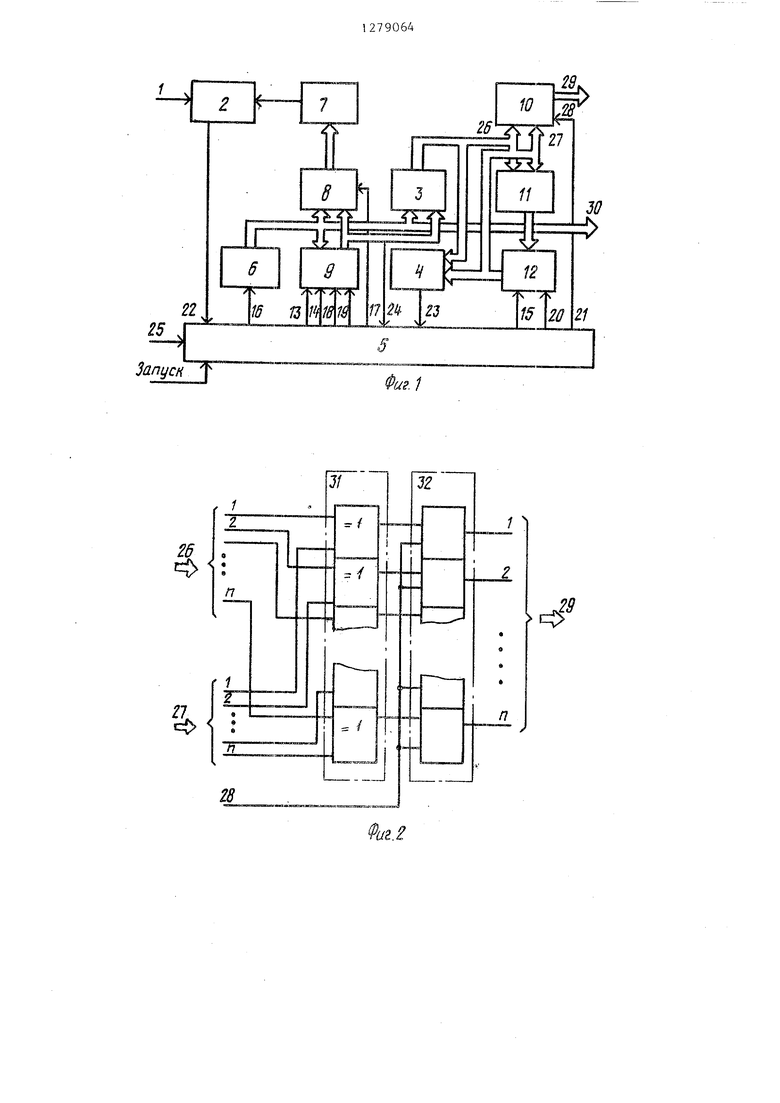

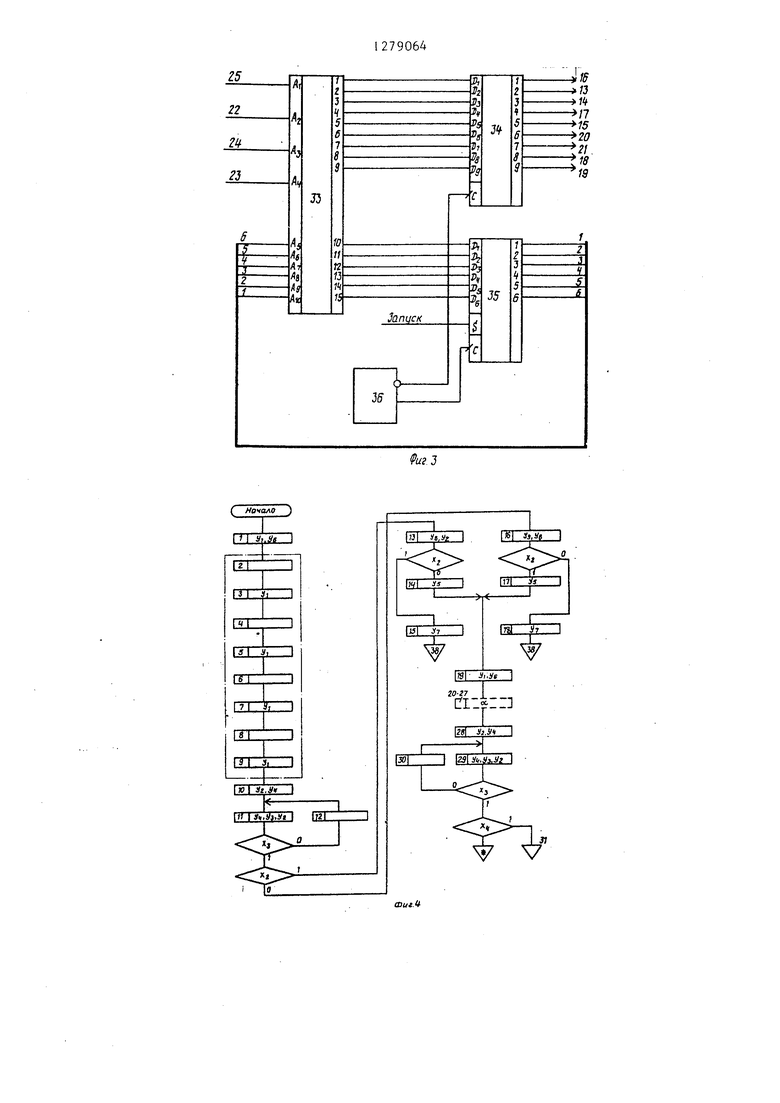

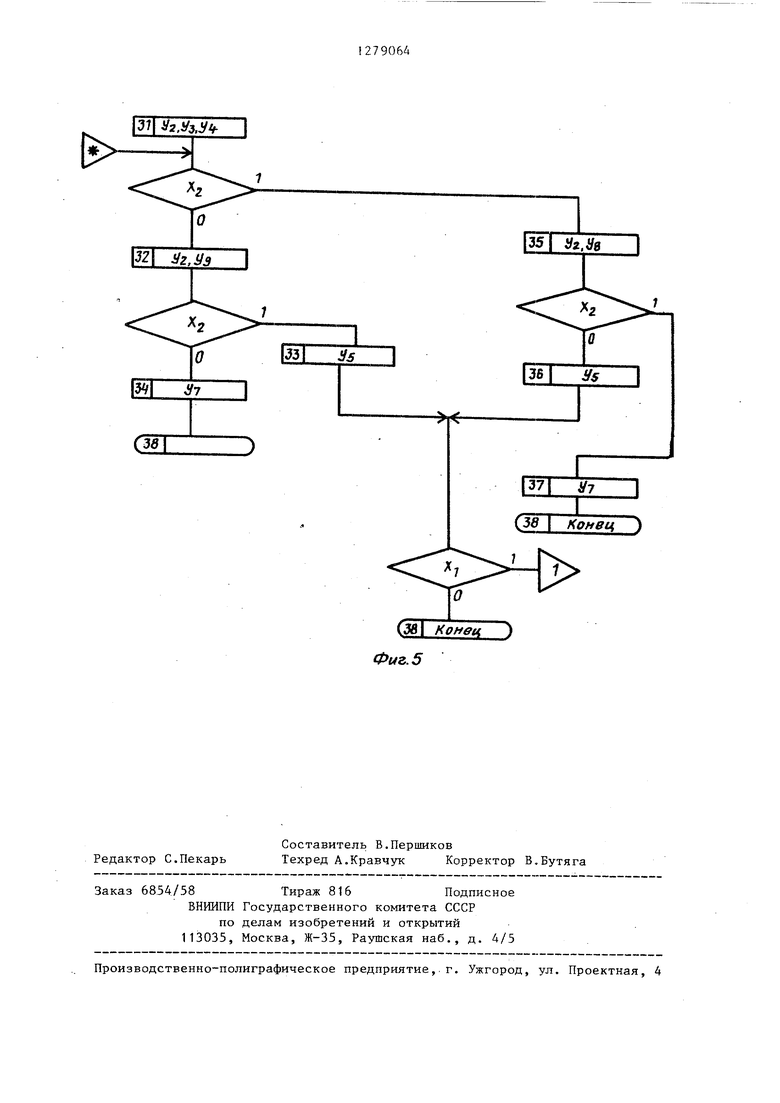

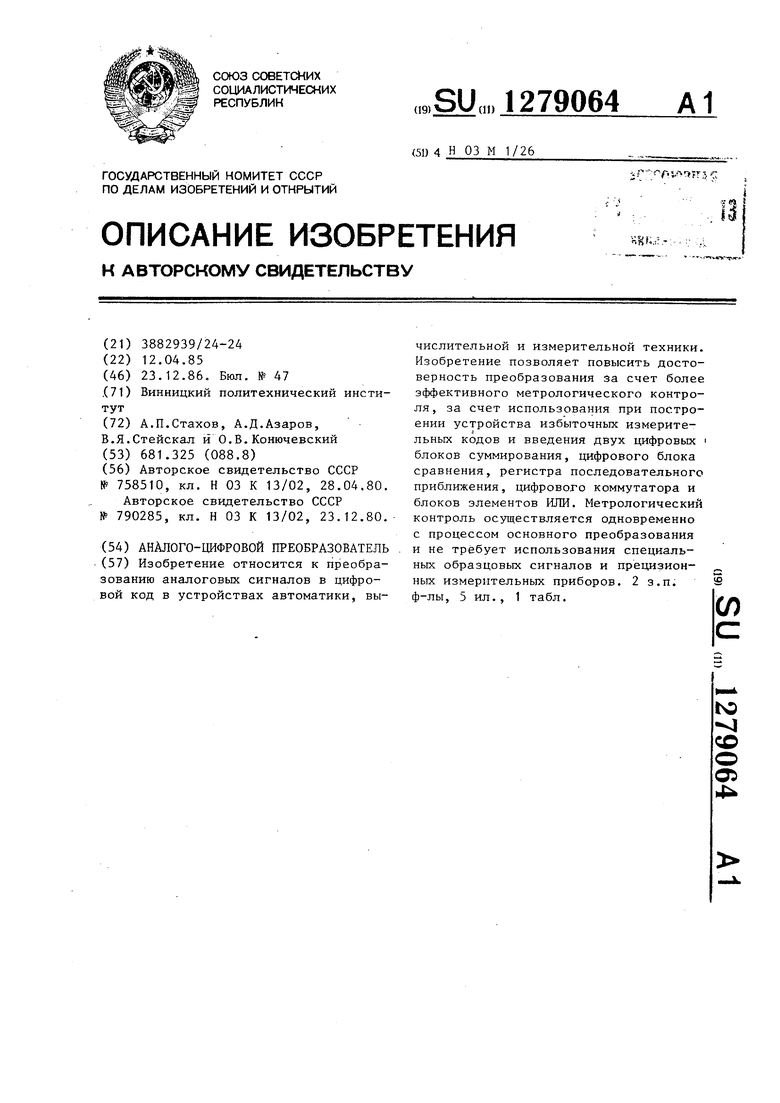

На фиг,1 приведена структурная схема аналого-цифрового преобразователя (АЦП); на фиг.2 - функциональная схема второго блока суммирования; на фиг.3 - функциональная схема блока управления; на фиг.4 и 5 - граф-схема алгоритма работы устройства,

Аналогд-цифровой преобразователь (фиг,1) содержит входную шину 1, блок 2 сравнения (БС), первый блок 3 суммирования (BG1), цифровой блок 4 сравнения (ЦБС), блок 5 управления (БУ), регистр 6 последова.тельного приближения (РПП), цифроаналоговый преобразователь 7 (ЦАП), цифровой коммутатор 8 (ЦК), блок 9 развертки Щ}ца (БРК), второй блок 10 суммирования (БС2), блок.11 элементов ИЛИ, регистр 12 (РГ), Блок 5 управления имеет выходы с первого по девятый 13-21 и входы с первого по четвертый 22-25 и пятый вход Запуск. Второй блок 10 суммирования имеет первые и вторые информационные входы 26 и 27, управляющий вход 28, выходы 29, которые являются выходными контрольными шина- 35

20

:35

30

где аре{0,1};

,2,,..s - номер разряда;

,1,2,.,. - параметр кода;

Ч (О - вес Е-го разряда. В кодах золотой р-пропорции любое действительное число может быть представлено в виде

-йг л

А П: а,-а„ ,

где ,Г};

t - номер разряда; р - параметр кода;

Ыр - вес t-ro разряда.

Над разрядами указанных кодов может быть выполнена операция развертки. Развертка заключается в замене единицы в разряде нулем, а нулей в (Е-1)-м и (Е.-р-1)-м разрядах единицами ,

В случае точного соответствия весов разрядов цифроаналогового .преобразователя требуемым значениям выполнение операции развертки над разрядами кодовой комбинации, подаваемой на вход цифроаналогового преобразователя, не изменяет значения выходной аналоговой величины,

В случае несоответствия весов разрядов цифроаналогового преобразователя требуемым значениям выполнение операции развертки над разрядами кодовых комбинаций меняет значение аналоговой величины.

ми. АЦП имеет также выходные шины 30

Указанное обстоятельство лежит в основе метрологического контроля пред-. лагаемого устройства. При одинаковой относительной погрешности весов разрядов цифроаналогового преобразователя абсолютная погрешность, вносимая отклонением старших разрядов, намного больше абсолютной погрешности, вносимой отклонением младших разрядов, поэтому разрядная сетка условно разбивается на группу контролируемых (старших) разрядов, группу точных (младВторой блок 10суммирования (фиг.2) выполнен на ь элементах З 1 Исключающее ИЛИ и п элементах 32 И,

Блок 5 управления выполнен на постоянном запоминающем устройстве 33 (ПЗУ), первом и втором регистрах 34 и- 35 и генераторе 36 тактовых импульсов.

Метрологический контроль аналого- цифрового преобразователя осуществляется на основании определенных соотношений между весами разрядов цифро- аналогового преобразователя, выполненного на-основе кодов с иррациональными основаниями типа р-кодов Фибоначчи и кодов золотой р-пропорции. в р-кодах Фибоначчи любое натуральное число может быть представлено в виде

50

55

ших) разрядов и, кроме того, содержит. дополнительный разряд, вес которого равен весу младшего разряда. Дополнительный разряд необходим для проведения метрологического контроля, кото- рьй осуществляется при выполнении операции развертки кода путем анализа выходного сигнала Y блока 2 сравнения. Причем сигнал Y подчиняется следующему соотношению:

f.O

(O

где аре{0,1};

,2,,..s - номер разряда;

,1,2,.,. - параметр кода;

Ч (О - вес Е-го разряда. В кодах золотой р-пропорции любое действительное число может быть представлено в виде

-йг л

А П: а,-а„ ,

где ,Г};

t - номер разряда; р - параметр кода;

Ыр - вес t-ro разряда.

Над разрядами указанных кодов может быть выполнена операция развертки. Развертка заключается в замене единицы в разряде нулем, а нулей в (Е-1)-м и (Е.-р-1)-м разрядах единицами ,

В случае точного соответствия весов разрядов цифроаналогового .преобразователя требуемым значениям выполнение операции развертки над разрядами кодовой комбинации, подаваемой на вход цифроаналогового преобразователя, не изменяет значения выходной аналоговой величины,

В случае несоответствия весов разрядов цифроаналогового преобразователя требуемым значениям выполнение операции развертки над разрядами кодовых комбинаций меняет значение аналоговой величины.

ших) разрядов и, кроме того, содержит. дополнительный разряд, вес которого равен весу младшего разряда. Дополнительный разряд необходим для проведения метрологического контроля, кото- рьй осуществляется при выполнении операции развертки кода путем анализа выходного сигнала Y блока 2 сравнения. Причем сигнал Y подчиняется следующему соотношению:

Y ABX I 1 если A A ,

где A - входной аналоговый сигнал: вх

А, - компенсирующий аналоговый сигнал.

Устройство работает следующим образом.

Преобразуемая аналоговая величина А поступает на входную шину 1 устройства и в процессе аналого-цифрового преобразователя уравновешивается компенсирующим сигналом А ЦАЛ 7 по методу поразрядного кодирования. В процессе уравновешивания участвуют блоки 2 и 5 - 9. Причем на вход ЦАП 7 через цифровой коммутатор 8 поступает информация с выхода регистра 6 последовательного приближения, а блок 9 развертки кода полностью повторяет выходной сигнал блока 6. После окончания непосредственного аналого- цифрового преобразования входной аналоговый сигнал А уравновешен сигналом А с точностью до половины младшего разряда ЦАП 7. При этом результат преобразования находится в блоках 6 и 9 и с выхода блока 6 поступает на информационный выход 30 устройства.

Далее по сигналу блока 5 управления осуществляется развертка кода, находящегося в блоке 9. Причем развертка кода происходит до появления значащей единицы в младшем точном разряде. Дополнительный разряд в этом случае установлен в нулевое состояние.

Затем развернутая кодовая комбинация через цифровой коммутатор 8 поступает на вхор ЦАП 7 и производится анализ выходного сигнала у блока 2 сравнения. В зависимости от уровня логического сигнала Y устанавливается в единичное состояние дополнительный разряд ЦАП 7 (Y 0) либо устанавливается в нулевое состояние младший точный разряд ЦАП 7 (Y 0). Далее анализируется выходной сигнал Y блока 2 сравнения. Если веса разрядов ЦАП 7, участвовавшие в развертке кода в блоке 9, соответствуют своим метрологическим характеристикам, то значение сигнала Y. будет противоположно значению сигнала Y, . В случае расстройки какого-либо разряда сигнал Y будет равен сигналу У,.

Далее ло команде блока 5 управления с помощью первого блока 3 суммирования определяются номера разрядов, участвовавших в развертке кода в блоке 9. Для зтого производится суммирование по mod 2 содержимого блоков 6 и 9. Так как в регистре 6 последовательного приближения находится код, над которым не выполнялась операция

развертки, а в блоке 9 находится код в развернутой форме, то значащие единицы кода на выходе первого блока 3 суммирования будут соответствовать номерам разрядов ЦАП 7, участвовавших

в развертке кода. Затем код с выхода первого блока 3 суммирования поступа- .ет на вход блока 11 элементов 1ШИ и вход второго блока 10 суммирования. В случае, если веса разрядов ЦАП 7

не соответствуют метролод ическим характеристикам, этот код с помощью второго блока 10 суммирования суммируется по mod 2 с содержимым (нулевым) ре/гистра 12 и с выхода блока 10

поступает на контрольный выход 29 устройства. Если веса разрядов ЦАП 7 соответствуют требуемым значениям, то код с выхода блока 3 с помощью блока 11 су шируется (логически) с

содержимым (нулевьЕм) регистра 12. На этом первый цикл контроля заканчивается. При этом, если в процессе контроля было зафиксировано, что веса разрядов ЦАП 7 не соответствуют требуемым метрологическим характеристи-( кам, то значащие единицы кода на контрольном выходе 29 устройства укажут номера расстроенных разрядов. Если в процессе контроля не было зафиксировано растройки разрядов ЦАП 7, то зна- значащие единицы кода, находящегося в регистре 12, будут соответствовать номерам разрядов ЦАП 7, суммарное отклонение которых от требуемых значений не превьш1ает величины младщего разряда.

Затем после проведения следующего очередного цикла непосредственного преобразования сигнала А в код

начинается следующий цикл контроля. Причем для получения возможности проведения метрологического контроля новой группы разрядов ЦАП 7 после вьтолнения операции развертки кода в

блоке 9 производится сравнение кодов с помощью цифрового блока 4 сравнения , поступающих с выходов первого блока 3 суммирования и регистра 12.

Если эти коды равны (что свидетельствует о том, что данные разряды уже проконтролированы), то первый цифровой блок 4 сравнения вьфабатывает . логический сигнал , по которому при помощи блока 5 управления в блоке 9 произойдет еще один такт развертки кода. Дальнейшая работа устройства происходит аналогично описанному.

В конце цикла контроля код с выхода блока 3 логически просуммируется с содержимым регистра 12, если веса разрядов ЦАП 7 не имеют отклонений от требуемьк значений либо на контрольном выходе 29 устройства появится кодовая комбинация, значащие единицы в которой укажут номера разрядов ЦАП 7, имекяцих отклонения от требуемых значений. Причем, так как выходной код блока 10 представляет собой сумму по mod 2 содержимого блока 3 и регистра 12, то номера разрядов ЦАП 7, величины которых имеют отклонения от требуемых значений, во втором цикле метрологического контроля будут указаны более точно, чем в первом. На этом второй цикл метрологического контроля заканчивается.

Блок 5 управления может быть синтезирован различными методами. Например, он может быть выполнен на основе автомата с памятью или по принципу программного управления. Один из воз- можньк вариантов реализации блока управления приведен на фиг.З. Для формирования управляющих сигналов применена последовательная схема с использованием ПЗУ.

Необходимые для управления функционированием АЦП управляющие и условные сигналы приведены в таблице.

РШ16

6

Продолжение таблиць

20 28

18

19

РГ12 Обнуление РГ12

Строб блока 10

Включение дополнительного разряда

Выключение младшего разряда

Примечание. При х 1 - разрешение преобразования; х 1, если Ag,A(;; при X 1 - равенство кодов; при коммутируется вькод ВРК9.

Алгоритм функционирования предлагаемого устройства в соответствии с приведенным описанием приведен на фиг.4 и 5, где вершины 1-9.- поразрядное уравновешивание входной аналоговой величины; вершины 10-12 - развертка кода до появления единицы в младшем разряде; вершины 13-18 - определение наличия отклонений и номеров весов разрядов; вершины 19-28 - непосредственное поразрядное кодирование входной аналоговой величины; вершины 29-31 - развертка кода и проверка на равенство содержимого PF12 j и выходного сигнала блока 3; вершины 32-38 - определение наличия отклонений и номеров весов разрядов.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий блок управления, блок развертки кодов, регистр, цифро- аналоговый преобразователь и блок сравнения, первый вход которого является входной шиной, второй вход подключен к выходу цифроанадогового преобразователя , выход подключен к первому входу блока управления, пелвый

и второй выходы которого подключены Соответственно к первому и второму управляющим входам блока развертки кодов, третий выход подключен к первому управляющему входу регистра, отличающийся тем, что, с целью повышения достоверности результатов преобразования, в него введены цифровой блок сравнения, первый и второй блоки суммирования, блок элементов ИЛИ, цифровой коммутатор, регистр последовательного приближения, вход которого подключен к четвертому выходу блока управления, выходы которого являются выходными информационными шинами и подключены к соответствующим первым входам первого блока суммирования, информационным входам блока развертки кода и первым информационным входам цифрового коммутато- ра, выходы которого подключены к входам цифроаналогового преобразователя управляющий вход подключен к пятому выходу блока управления, шестой и седьмой выходы которого подключены к третьему и четвертому управляющим входам блока развертки кода, выходы которого подключены к вторым информационным входам цифрового коммутатора и вторым входам первого блока суммирования-, выходы которого подключены к соответствующим первым информационным входам второго блока суммирования, первым входам блока элементов

или и первым входам цифрового блока сравнения, выход которого подключен к второму входу блока управления, вторые входы объединены с соответствующими вторыми информационными входами второго блока суммирования, вторыми входами блока элементов ИЛИ и подключены к coojBeTCTByronyiM выходам регистра, информационные входы которого подключены к соответствующим выходам блока элементов ИЛИ, второй управляющий вход подключен к восьмому выходу блока уравления, третий вход которого подключен к выходу младшего разряда блока развертки кода, четвертый вход является шиной Режим работы, пятый вход является

10

15

20

790648

шиной Запуск, девятый выход подключен к управляющему входу второго блока суммирования, выходы которого являются выходными контрольными шинами. 5 2. Преобразователь по п.1, о т - личающийся тем, что второй блок суммирования выполнен на кь элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, где и,- число разрядов аналого-цифрового преобразования, и п-элементах И, выходы которых являются соответствующими выходами второго блока суммирования, первые входы объединены и являются управляющим входам второго блока суммирования, вторые входы подключены к совт- ветствующим выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых являются первыми информационными входами второго блока суммрования, а вторые входы являются вторь}ми информационными входами второго блока суммирования.

3. Преобразователь по п.1, о т - личающийся тем, что блок управления выполнен на первом и втором регистрах, генераторе тактовых импульсов и постоянном запоминающем устройстве, выходы с первого по девятый которого подключены к соответствующим информационным входам первого регистра, адресные входы с первого по четвертый являются соответственно четвертым, первым, третьим и вторым входами блока управления, адресные входы с пятого по десятый подключены к соответствующим выходам второго регистра, информационные входы которого подключены соответственно к выходам постоянного запоминающего устройства с десятого по пятнадцатый, первый управляющий вход является пятым входом блока управления, второй управляющий вход подключен к прямому выходу генератора тактовых импульсов, инверсный выход которого подключен к управляющему входу первого регистра, выходы с первого по девятый которого являются соответственно четвертым, первым, пятым, третьим, восьмым, девя25

30

35

40

45

50 тым, шестым и седьмым выходами блока управления.

anyciTj

Фиг.1

Лт

Т

г

3

и

5 6 7

X«

AT

« II к

13 ( i

3

i г

3

ч

5 tf 7 S 3

W

:t t

/5

JV

I

Д,

35

hngcK

c

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU953721A2 |

| Цифро-аналоговый преобразователь | 1978 |

|

SU947955A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

Изобретение относится к преобразованию аналоговых сигналов в цифровой код в устройствах автоматики, вычислительной и измерительной техники. Изобретение позволяет повысить достоверность преобразования за счет более зффективного метрологического контроля, за счет использования при построении устройства избыточных измерительных кодов и введения двух цифровых i блоков суммирования, цифрового блока сравнения, регистра последовательного приближения, цифрового коммутатора и блоков элементов ИЛИ. Метрологический контроль осуществляется одновременно с процессом основного преобразования и не требует использования специальных образцовых сигналов и прецизионных измерительных приборов. 2 з.п. ф-лы, 5 ил., 1 табл. Ф (Л ю со о 05 4

( Начало j I I

LH

I

Ш ii.nt.

|g| ii.nt I

LH.

j1

El.

. I

(ji/l yj IП71 p1

1)1 7I

LH.

ЕЕ

JL

m:

3 s, I

J,.yV 1

31 У2,у I

|

(3fl I /fg/fg2j )

Редактор С.Пекарь

Составитель В.Першиков

Техред А.Кравчук Корректор В.Бутяга

Заказ 6854/58 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,,г. Ужгород, ул. Проектная, 4

(381 f( ) Фиг. 5

| Аналого-цифровой преобразователь | 1978 |

|

SU758510A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-23—Публикация

1985-04-12—Подача