(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU750721A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU783979A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU758510A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

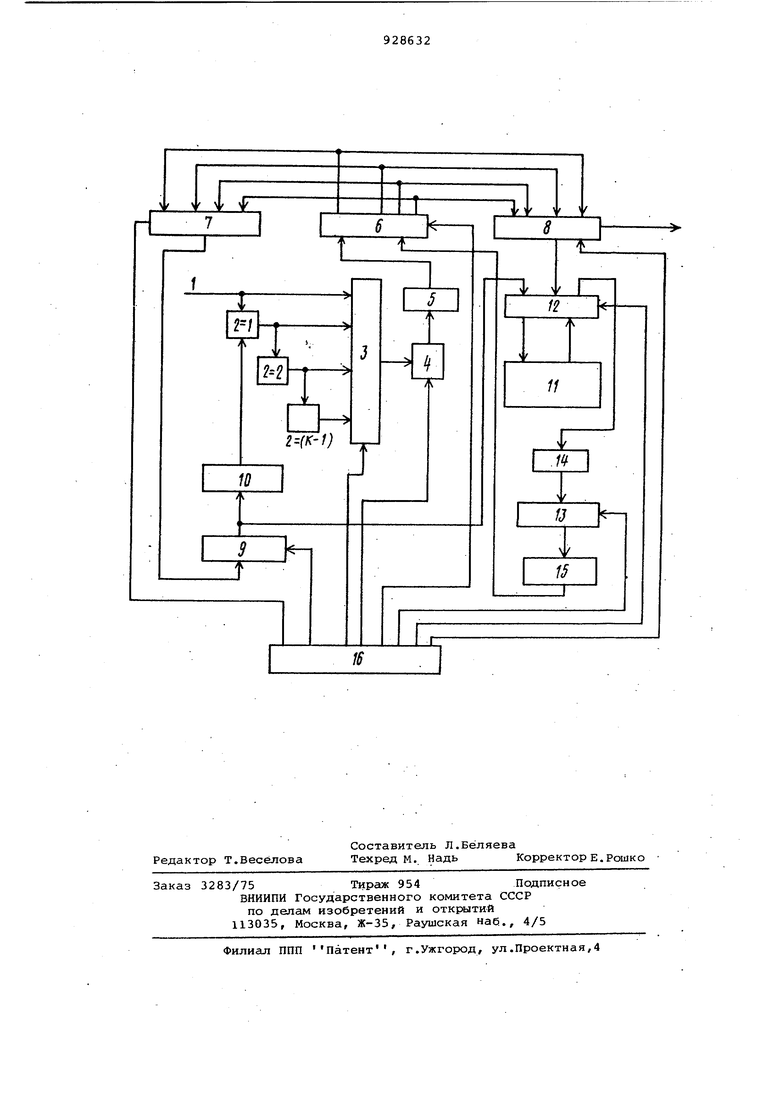

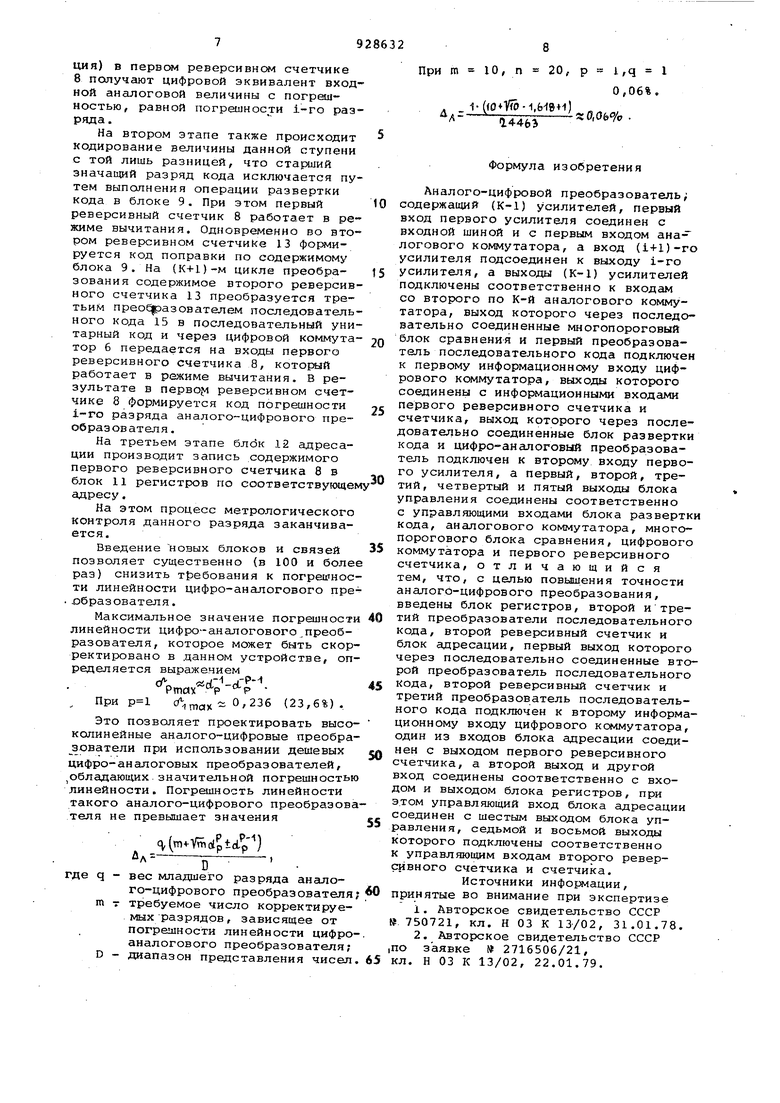

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Известен аналого-цифровой -преобразователь, содержащий (К-1) усилите лей, (К-1) цифро-аналоговых преобразователей, многопороговый блок.сравнения, преобразователь параллельного кода, аналоговый коммутатор, первый и второй цифровые коммутаторы, преоб разователь последовательного кода, счетчик, блок контроля и блок управления 1 . Недостатком такого аналого-цифрового преобразователя является зависимость погрешности линейности выход ной характеристики от линейности выходной характеристики цифро-аналогового преобразователя. Наиболее близким к предлагаемому по технической сущности является аналого-цифровой преобразователь, со держащий (К-1) усилителей, цифро-ана логовый преобразователь, аналоговый коммутатор, многопороговый блок срав нения, блок управления, преобразователь последовательного кода, счетчик цифровой коммутатор, реверсивный счетчик, цифровой блок сравнения, блок анализа кода, регистр, блок свертки и развертки кода, причем выход цифро-аналогового преобразователя соединен со вторым входом первого усилителя, первый вход которого соединен с первым входом аналогового коммутатора и является входом аналогоцифрового преобразователя, вход i-ro усилителя соединен с выходом (i-1)го усилителя, выходы (К-1) усилителей соединены со второго по К-й входами аналогового коммутатора, выход которого соединен со входом многопорогового блока сравнения, выход многопорогового блока сравнения соединен со входом преобразователя последовательного кода, выход которого соединен с информационным входом цифрового коммутатора, выходы цифрового коммутатора соединены с информационными входами реверсивного счетчика и с информационными входами счетчика, выход которого соединен с первым информационным входом блока свертки и развертки кода и информационным входом блока анализа кода, выход блока свертки и развертки кода соединен со входом цифро-аналогового преобразователя, выход блока анализа кода соединен с информационным входом регистра, выход которого соединен со вторым информационным входом блока свертки и развертки кода, выход ревер сивного счетчика соединен со входом цифрового блока сравнения и является выходом аналого-цифрового преобразователя-, выход цифровой схемы сравнения соединен со вторым управляющим входом блока анализа кода, управляющие входы аналогового коммутатора, многопорогового блока сравнения, цифрового коммутатора, счетчика, блока свертки и развертки кода, регистра, реверсивного счетчика и первый управляющий вход блока анализа кода соедииены соответственно с первым, вторлм третьим, четвертым, пятым, шестым, и восьмым входами блока управ ления 2 . Недостатком данного анапого-цифрового преобразователя является то, что линейность выходной характеристики в значительной,степени зависит от погрешности линейности цифро-аналогового преобразователя. Цель изобретения - повышение точности аналого-цифрового преобразования. Поставленная цель достигается тем что в аналого-цифровой преобразователь, содержащий (К-1) усилителей, первый вход первого усилителя соеди-: нен со входной шиной и с первым входом аналогового коммутатора, а вход (i+l)-ro усилителя подсоединен к выходу i-TO. усилителя, а выходы (К-1) усилителей подключены соответственно к входам со второго по К-й аналогово го коммутатора, выход которого через последовательно соединенные многопороговый блок сравнения и первый преобразователь последовательного кода подключен к первому информационному входу цифрового коммутатора, выходы которого соединены с информационными входами первого реверсивного счетчик и счетчика, выход которого через последовательно соединенные блок развертки кода и цифро-аналоговый преоб разователь подключен ко второму вход первого усилителя, а первый, второй третий, четвертый и пятый выходы бло ка управления соединены соответствен но с управляющими входами блока развертки кода, аналогового коммутатора многопорогового блока сравнения, циф рового коммутатора и первого реверсивного счетчика, введены блок регистров, второй и третий преобразова тели последовательного кода,второй реверсив.ный счетчик и блок адресации первый выход которого через последо тельно соединенные второй преобразо ватель последовательного кода, второй реверсивный счетчик и третий пр образователь последовательного кода одключен ко второму информационному ходу цифрового коммутатора, один из ходов блока адресации соединен с выодом первого реверсивного счетчика, второй выход и другой вход соединеы соответственно с входом и выходсм блока регистров, при этом управляюий вход блок.а адресации соединен с естым выходом блока управления, седьой и восьмой выходы которого подклюены соответственно к управляющим входам второго реверсивного счетчика счетчика. На чертеже представлена функциональная схема аналого-цифрового преобразователя. Аналого-цифровой преобразователь содержит входную шину 1, (К-1) усилителей 2, аналоговый коммутатор 3, многопороговый блок 4 сравнения, преобразователь 5 последовательного кода, цифровой коммутатор б, счётчик 7, реверсивный счетчик 8, блок 9 развертки кода, цифро-аналоговый преобразователь 10, блок 11 регистров, блок 12 адресации, второй реверсивный счетчик 1-3, второй 14 и третий 15 преобразователи последовательного кода, блок 16 управления. Аналого-цифровой преобразователь , работает в следующих режимах: режиме поверки и режиме непосредственного преобразования аналоговой величины в код золотой р-пропорции. Процесс преобразования входной аналоговой величины в п-разрядный код золотой р-пропорции происходит за (К+1)циклов. В каждом из К циклов формируется m разрядов кода и производится вычисление погрешности линейности. В (К+1)-м цикле происходят цифровая коррекция результата преобразования. В режиме поверки определяются коды погрешностей линейности выходной характеристики аналого-цифрового преобразователя. В коде золотой р-пропорции любое действительное число D представляется в виде + о ,, где VtOHl dip - вес 1-го разряда; р О, 1, 2... Имеется множество представлений данного вида, среди которалх существует единственная минимальная форма, для которой после каждой единицы следует не менее р нулей. Веса разрядов кода связаны между собой рекуррентным соотношением .С ,. .) . которое лежит в основе операции свертки и развертки.разрядов кода. Свертка заключается в замене нуля в

J-M и единиц в. (B-l)-M и (Е-р-1)-м разрядах их отрицаниями. Развертка является операцией, обратной свертке, и состоит в замене единицы J-ro разряда и нулей (t-l)-ro и (B-p-l)-r разрядов их отрицаниями. Особенность этих операций состоит в том, что они не изменяют величины отображаемого кодом числа, а изменяют лишь форму представления кода.

В режиме преобразования входной аналоговой величины в код золотой р-пропорции устройство работает следующим образом.,

В первом цикле входная аналоговая величина со входной.шины 1 подается на первый вход аналогового коммутатора. 3, кото1 лй под действием управляющего сигнала, поступающего из блока 16 управления, передает ее на вхо многопорогового блока сравнения 4, который преобразует входную аналоговую величину в параллельный код, который преобразуется в последовательный унитарный код преобразователем 5 последовательного кода. Последовательный унитарный код через цифровой кои утатор 6 поступает на первые , входы счетчика 7 и реверсивного счетчика 8. По команде из блока 1.6 управления блок 12 адресации производи последовательную выборку из блока 11 регистров, в котором хранятся коды погрешностей весов разрядов цифроаналогового преобразователя 10. Шбранные коды погрешностей, соответствующие кодовой комбинации, полученной на первом цикле преобразовани преобразуются вторым преобразователем 14 последовательного кода в последовательный унитарный код, с его выхода последовательный унитарный код поступает на вход второго реверсивного счетчика 13, в котором формируется результирующий код поправки, соответствующий первому циклу преобразования. На этом первый цикл ttpeобразования заканчивается.

Во втором цикле золотой р-код из счетчика 7 передается в блок 9 « развертки кода, с его выхода кодовая комбинация поступает на вход цифроанёшогового преобразователя 10. Аналоговый экривалент входной кодовой комбинации с выхода цифро-аналогового преобразователя. 10 поступает на второй вход усилителя 2-1, на первый вход которого подана входная преобразуемая величина. Разность этих величин Д усиливается усилителем 2-1 в /LK, раз и подается на второй вход аналогового коммутатора 3. По команде из блока 16 управления величина ц./и, передается на вход многопорЬговогО 4 сравнения. Параллельный унитарный код, соответствующий этой величине, преобразуется преобразователь 5 последовательного кода в последовательный унитарный код, который передается через цифровой коммутатор б на вторые входы счетчика 7 и первого реверсивного счетчика 8, тем самым к их содержимому добавляется результат преобразования второго цикла. По команде блока 16 управления блок 12 адресации производит последовательную выборку из блока 11 регистров кодов погрешностей, соответствующих кодовой комбинации, полученной во втором цикле преобразования. Выбранные коды погрешностей преобразуются в последовательный унитарный код во втором преобразователе 14 последовательного кода и поступают на вход второго реверсивного счетчика 13, в котором формируется суммарный код поправки первого и второго цикла преобразования. На этом второй цикл преобразовгния закачиваётся.

Третий и четвертый циклы преобразования осуществляются аналогичным образе, причем в работу включаются усилитель 2-2 и усилитель 2-3 соотвественно в третьем и четвертом циклах

В К-том цикле преобразования по комайде из блока 16 управления резултирующий код поправки, формирующийся за (К-1) цикл преобразования, с выхода второго реверсивного сметчика 13 поступаетна вхОд третьего преобразователя 15 последовательного ко-; да, преобразованная кодовая комбинация через цифровой коммутатор 6 передается на входы первого реверсивного счетчика 8. Таким образом по окончан К-го цикла преобразования в первом реверсивном счетчике 8 формируется скорректированный цифровой эквивален входной аналоговой величины.

Режим метрологического контроля линейности выходной характеристики аналого-цифрового преобразователя за клк)чается в определении кодов отклонений весов разрядов от требуемых значений. Процесс контроля начинается с (р+2}-гЬ разряда цифро-аналогового преобразователя при условии, что (P+I) младших разрядов точные.

На входную шину 1 аналого-цифрового преобразователя подается ступенчато нарастающая аналоговая величина, i-я ступень которой используется для

проверки i-ro разряда. Процесс контроля Любого разряда состоит из трех этапов.

На первом этапе производится преобразование величины 1-й ступени в код описанным способом. При этом за К циклов преобразования во втором реверсивном счетчике 13 формируется результирующий код поправки, учитывающий погрешности (i-l) младщих разрядов. Таким образом, после (К+1)-Го цикла преобразования (цифровая коррекция) в первом реверсивном счетчике 8 получают цифровой эквивалент входной аналоговой величины с пограиностью, равной погрешности i-ro разряда . На втором этапе также происходит кодирование величины данной ступени с той лишь разницей, что старший значащий разряд кода исключается путем выполнения операции развертки кода в блоке 9. При этом первый реверсивный счетчик 8 работает в режиме вычитания. Одновременно во втором реверсивном счетчиКе 13 формируется код поправки по содержимому блока 9. На (К+1)-м цикле преобразования содержимое второго реверсив ного счетчика 13 преобразуется третьим прео азователем последователь ного кода 15 в последовательный уни тарный код и через цифровой коммута тор 6 передается на входы первого реверсивного счетчика 8, КОТОЕМЙ работает в режиме вычитания. В результате в nepBOf реверсивном счетчике 8 формируется код погрешности i-ro разряда аналого-цифрового преобразователя. На третьем этапе блок 12 адресации производит запись содержимого первого реверсивного счетчика 8 в блок 11 регистров по соответствующе адресу. На этом процесс метрологического контроля данного разряда заканчивается. Введение новых блоков и связей позволяет существенно (в 100 и боле раз) снизить т{5ебования к погрешнос ти линейности цифро-аналогового пре . сбразователя. Максимальное значение погрешност линейности цифро-аналогового.преобразователя, которое может быть скор ректировано в данном устройстве, оп ределяется выражением Pmc..«V TПри сЛ,дх 0,236 (23,6%). Это позволяет проектировать высо колинейные аналого-цифровые преобра зователи при использовании дешевых цифро-аналоговых преобразователей, обладаюищх значительной погрешность линейности. Погрианость линейности такого аналого-цифрового преобразов теля не превышает значения cv((iJt4) вес младшего разряда аналого-цифрового преобразователя требуемое число корректируемых разрядов , зависящее от погрешности линейности цифро аналогового преобразователя диапазон представления чисел При m 10, п 20, р i,q 1 0,06%. 1-(101 Ь-ЬИви) .s(J,a69c. Формула изобретения Аналого-цифровой преобразователь; содержащий (К-1) усилителей, первый вход первого усилителя соединен с входной шиной и с первым входом ана- логового коммутатора, а вход (i+l)-ro усилителя подсоединен к выходу i-ro усилителя, а выходы (К-1) усилителей подключены соответственно к входам со второго по К-й аналогового коммутатора, выход которого через последовательно соединенные многопороговый блок сравнения и первый преобразователь последовательного кода подключен к первому информационному входу цифрового коммутатора, выходы которого соединены с информационными входами первого реверсивного счетчика и счетчика, выход которого через последовательно соединенные блок развертки кода и цифро-аналоговый преобразователь подключен к второму входу первого усилителя, а первый, второй, третий, четвертый и пятый выходы блока управления соединены соответственно с управляющими входами блока развертки кода, аналогового коммутатора, многоПорогового блока сравнения, цифрового коммутатора и первого реверсивного счетчика, отличающийся тем, что, с целью повышения точности аналого-цифрового преобразования, введены блок регистров, второй и третий преобразователи последовательного кода, второй реверсивный счетчик и блок адресации, первый выход которого через последовательно соединенные второй преобразователь последовательного кода, второй реверсивный счетчик и третий преобразователь последовательного кода подключен к второму информационному входу цифрового коммутатора, один из входов блока адресации соединен с выходом первого реверсивного счетчика, а второй выход и другой вход соединены соответственно с входом и выходом блока регистров, при этом управляющий вход блока адресации соединен с шестым выходом блока управления, седьмой и восьмой выходы которого подключены соответственно к управляющим входам второго реверсивного счетчика и счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №750721, кл. Н 03 К 13/02, 31.01.78. 2.Авторское свидетельство СССР |ПО заявке № 2716506/21, кл. Н 03 К 13/02, 22.01.79.

Авторы

Даты

1982-05-15—Публикация

1980-08-04—Подача