Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговьрс величин в цифровые.

Цель изобретения - повышение быстродействия аналого-цифрового преобразователя.

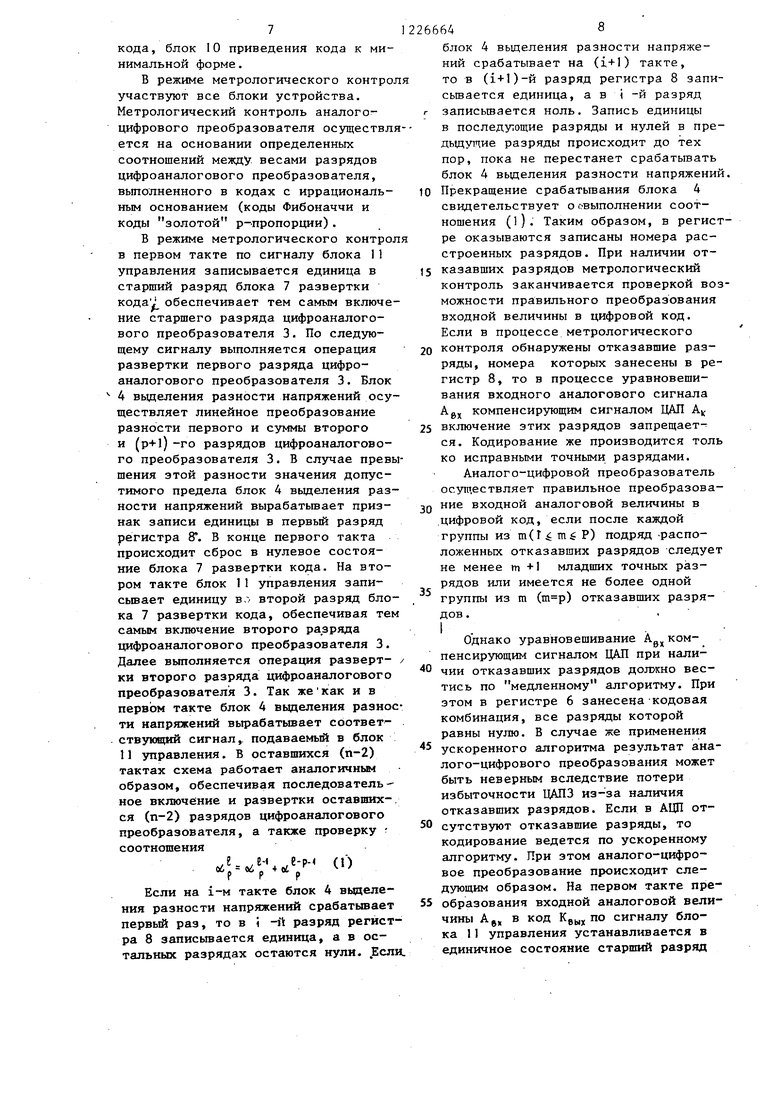

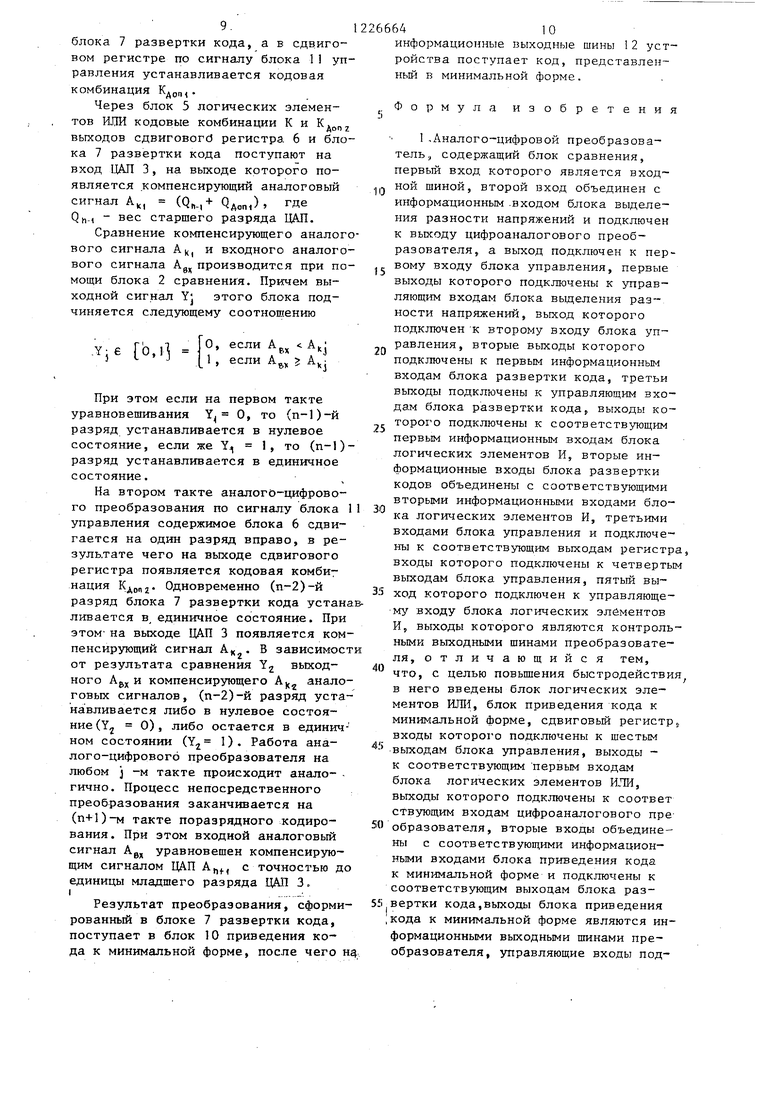

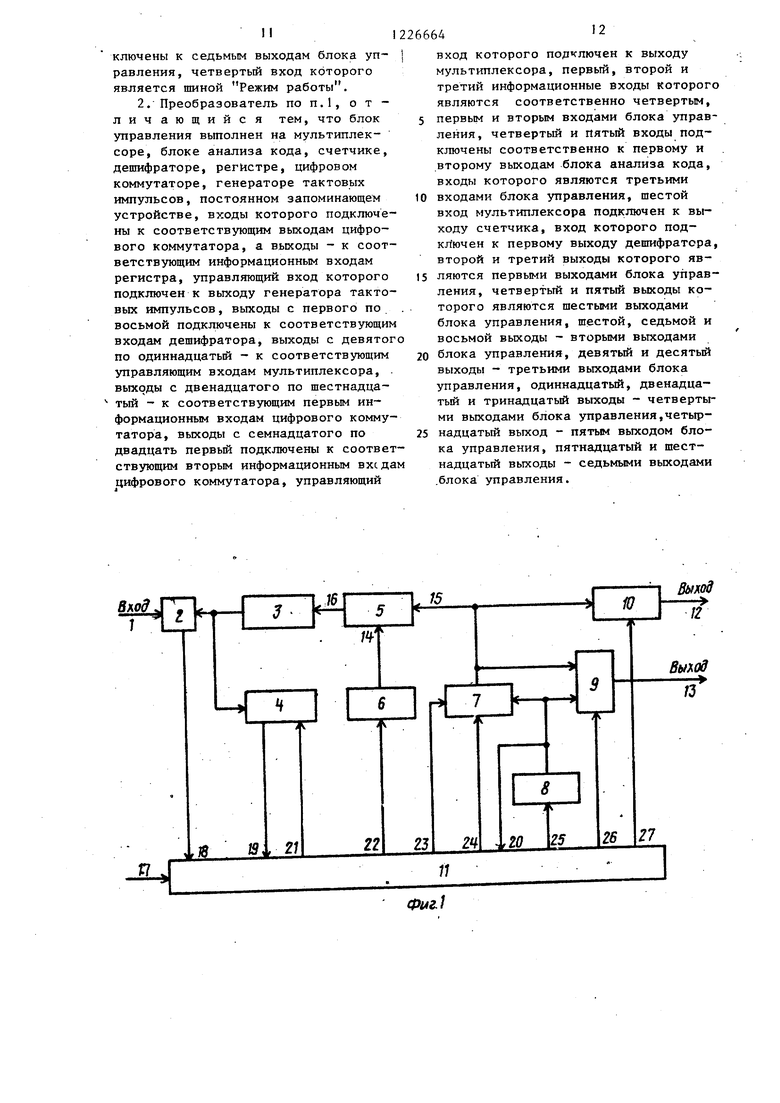

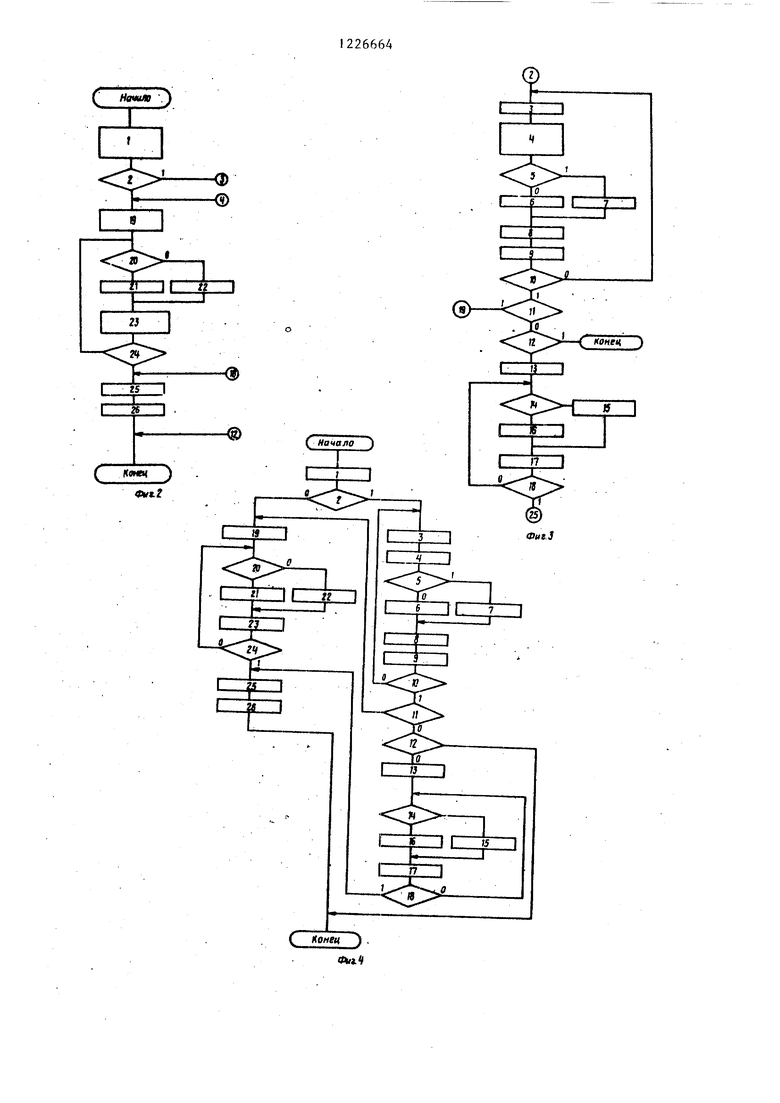

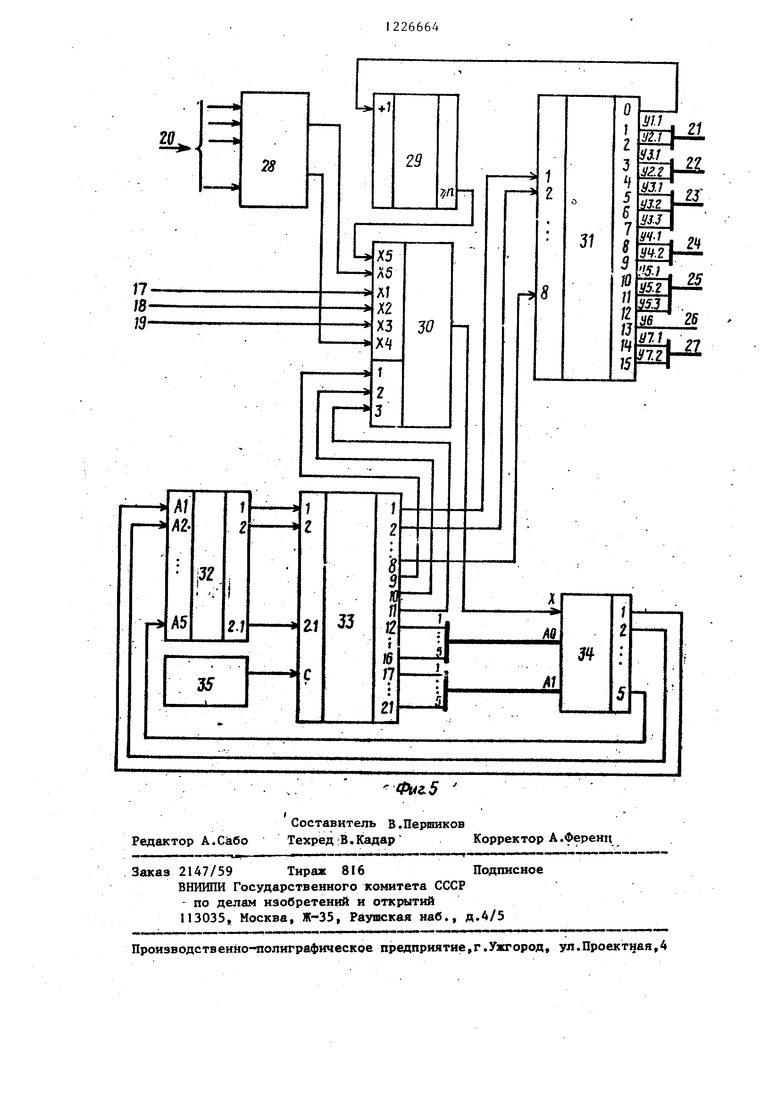

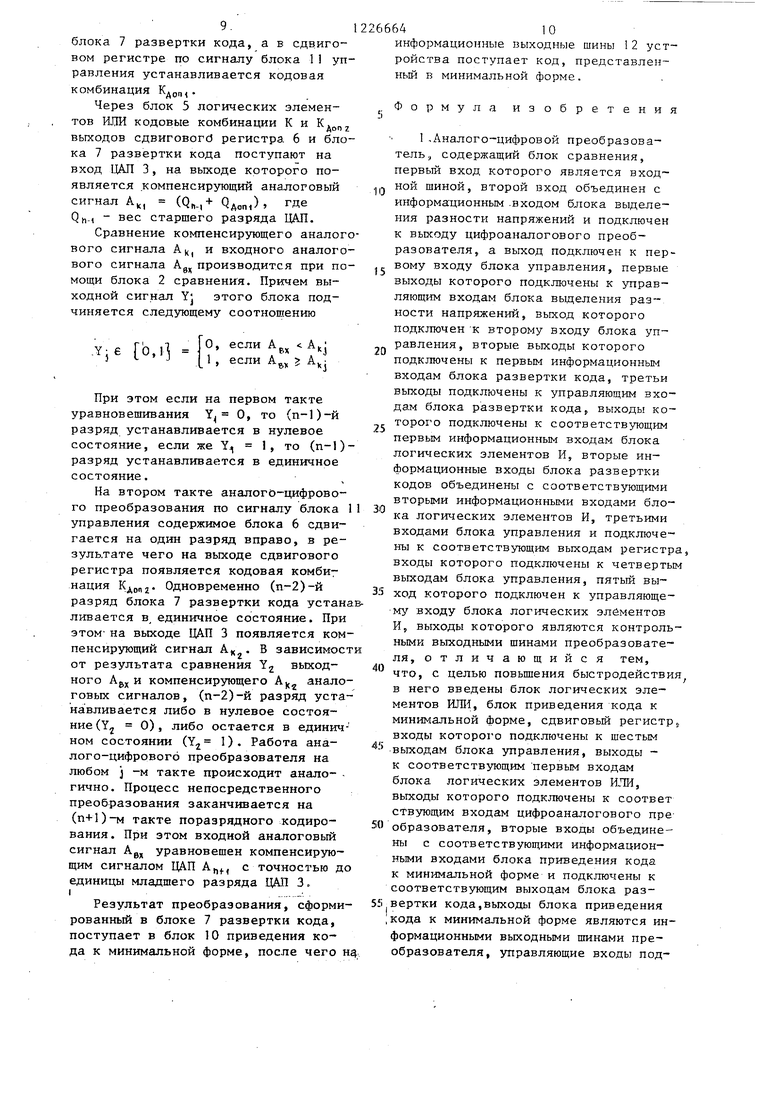

На фиг.1 приведена структурная схема аналого-цифрового преобразователя; на фиг.2 и 3 - микропрограмма работы блока управления; на фиг.4 - закодированный граф микропрограммы; на фиг.5 - функциональная схема блока управления с принудительной адресацией.

Аналого-цифровой преобразователь содержит входную шину 1, блок 2 сравнения (БС), цифроаналоговый преобразователь 3 (ЦАП), блок 4 выделения разности напряжений (БВР), сдвиго- вьй регистр 6 (СР) , блок 5 логичес ких элементов ИДИ (БЛЭ ИЛИ), блок 7

Обозначение связи

Назначение

1.1

1.2 2.1

2.2 3.1

3.2 3.3 4.1

4.2 5.1

5.2

5.3 6

7.1

7.2 8

Режим записи БВР4

Режим выдачи БВР4

RG

СА

к

%

RG,, : R, (RG,)

БРК : о

1 О . Развертка

Синхроимпульс RG : О

1 RGtn О Управление БЛЭ

Разрешение записи в

Приведение кода к минимальной форме (МФ) СЧ (1-п) : - О

5

0

развертки кода (БРК), регистр 8 (Р), блок 9 логических элементов И (БЛЭ И), блок 10 приведения кода к минимальной форме (БПМФ), блок 11 управления, информационные выходные шины 12, контрольные выходные шины . 13. Блок 5 логических элементов ИЛИ содержит первые входы 14 и вторые входы 15 и 16. Устройство содержит также входную шину 17 Режим работы , Блок 11 управления содержит первый и второй входы 18 и 19, третьи входы 20, первые выходы 21, шестые выходы 22, вторые выходы 23, третьи выходы 24, четвертые выходы 25, пятый вьтход 26, седьмой выход 27, четвертый вход блока 11 управления является входной шиной 17 Режим работы.

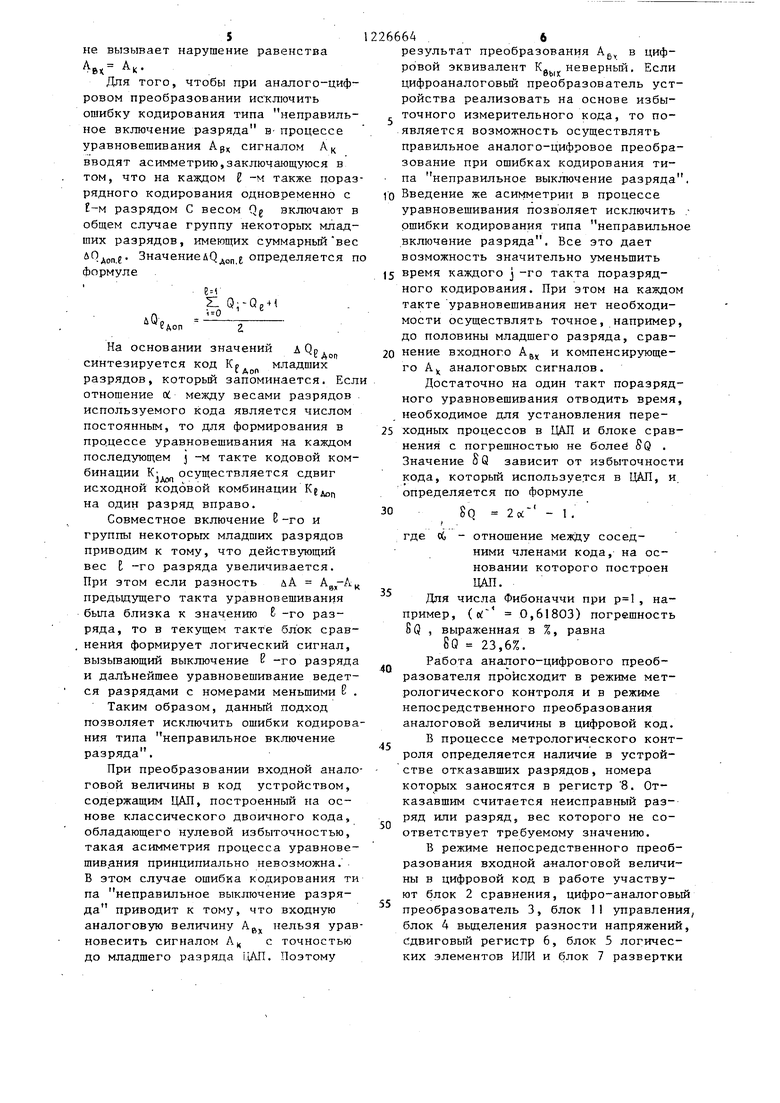

В табл.1 представлены микрооперации, используемые в микропрограмме (работы аналого-цифрового преобразо- , вателя.

Таблица I

связи

Номер связи

21

СА

к

%

22

23

24 25

25 26

27

312266644

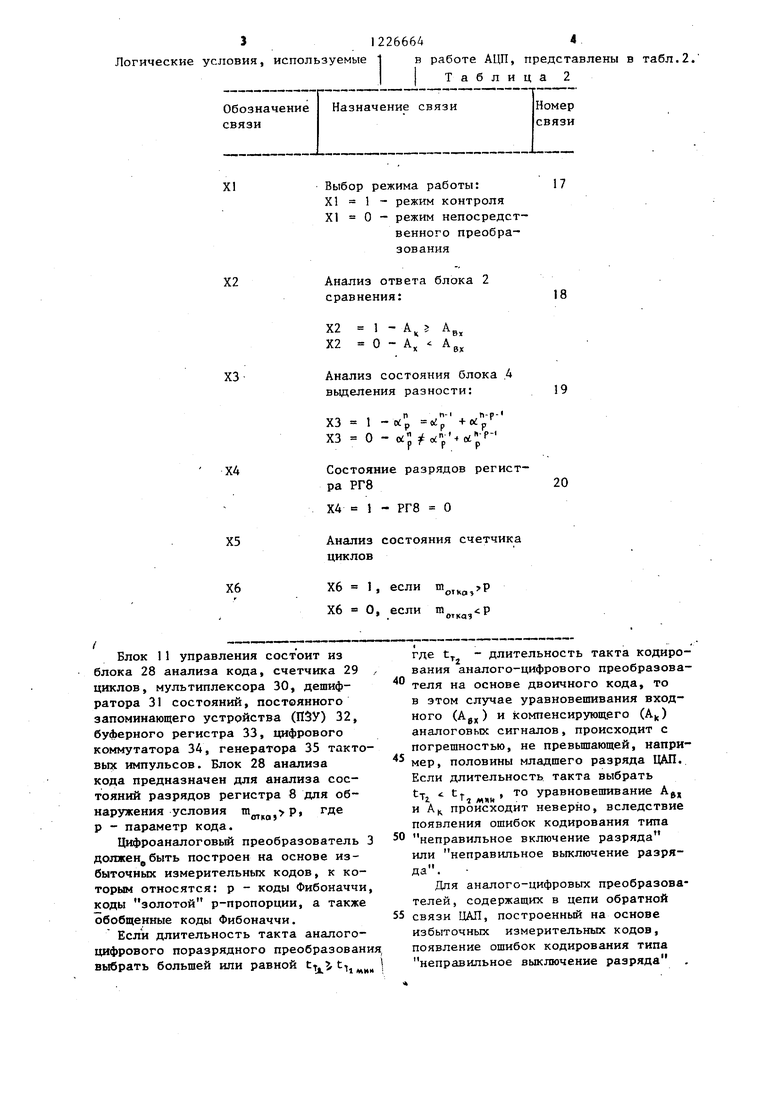

Логические условия, используемые в работе АЦП, представлены в табл.2,

Таблица 2

Обозначение связи

Назначение связи

Выбор режима работы: XI 1 - режим контроля XI О - режим непосредственного преобразования

Х2

Анализ ответа блока 2 сравнения:

Х2 1 - А, Х2 О - А.

Анализ состояния блока Л вьщеления разности: 19

ХЗ 1 -о.; ; -к.; ХЗ о - « p oi p 4od pfСостояние разрядов регистра РГ820

Х4

Х5

Анализ состояния счетчика циклов

Х6

Х6 1 , если П1,р Х6 О, если

Блок 1 1 управления сост оит из блока 28 анализа кода, счетчика 29 циклов, мультиплексора 30, дешифратора 31 состояний, постоянного запоминающего устройства (ПЗУ) 32, буферного регистра 33, цифрового коммутатора 34, генератора 35 тактовых импульсов. Блок 28 анализа кода предназначен для ангшиза состояний разрядов регистра 8 для обнаружения условия т р, где р - параметр кода.

Цифроаналоговый преобразователь 3 должеНдбыть построен на основе избыточных измерительных кодов, к которым относятся: р - коды Фибоначчи, коды золотой р-пропорции, а также обобщенные коды Фибоначчи.

Если длительность такта аналого- цифрового поразрядного преобразовани выбрать большей или равной

Номер связи

17

18

Вх ВХ

1 - РГ8 О

40

45

где t - длительность такта кодирования аналого-цифрового преобразователя на основе двоичного кода, то в этом случае уравновешивания входного (Ag) и компенсирующего (А) аналоговых сигналов, происходит с погрешностью, не превьшгающей, например, половины младшего разряда ЦАП. Если длительность такта выбрать tj tf , то уравновешивание А, и АИ происходит неверно, вследствие появления ошибок кодирования типа 50 неправильное включение разряда или неправильное выключение разряда. Для аналого-цифровых преобразователей, содержащих в цепи обратной 55 связи ЦАП, построенньй на основе избыточных измерительных кодов, появление ошибок кодирования типа неправильное выключение разряда

не вызывает нарушение равенства Лвх А,,.

Для того, чтобы при аналого-цифровом преобразовании исключить ошибку кодирования типа неправильное включение разряда в- процессе уравновешивания сигналом А вводят асимметрию,заключающуюся в том, что на каждом С -м также поразрядного кодирования одновременно с t-M разрядом С весом Qj включают в общем случае группу некоторых младших разрядов, имеющих суммарньш вес йОдр„. ЗначениеAQ определяется п формуле

iQc

М

QrQe

UO

едоп

младших

едоп 2

На основании значений синтезируется код К

V Аоп

разрядов, который запоминается. Есл отношение oi. между весами разрядов используемого кода является числом постоянным, то для формирования в про.цессе уравновешивания на каждом последующем j -м такте кодовой комбинации К; осуществляется сдвиг

jAon - .

исходной КОДОВОЙ комбинации на один разряд вправо.

Совместное включение В-го и группы некоторых младших разрядов приводим к тому, что действующий вес t -го разряда увеличивается. При этом если разность л А предыдущего такта уравновешивания была близка к значению Е -го разряда, то в текущем такте блок сравнения формирует логический сигнал, вызывающий выключение -го разряда и дальнейшее уравновешивание ведется разрядами с номерами меньшими Е

Таким образом, данный подход позволяет исключить ошибки кодирования типа неправильное включение разряда.

При преобразовании входной аналоговой величины в код устройством, содержащим ЦАП, построенный на основе классического двоичного кода, обладающего нулевой избыточностью, такая асимметрия процесса уравновешивания принципиально невозможна. В этом случае ошибка кодирования ти па неправильное выключение разряда приводит к тому, что входную аналоговую величину нельзя уравновесить сигналом Ац с точностью до младшего разряда LiAn. Поэтому

26664 . . 6

результат преобразования А в цифровой эквивалент К- „ неверный. Если оых

цифроаналоговый преобразователь устройства реализовать на основе избыточного измерительного кода, то появляется возможность осуществлять правильное аналого-цифровое преобразование при ошибках кодирования типа неправильное выключение разряда.

10 Введение же асимметрии в процессе уравновешивания позволяет исключить . ошибки кодирования типа неправильное включение разряда. Все это дает возможность значительно уменьшить

)5 время каждого j -го такта поразрядного кодирования. При зтом на каждом такте уравновешивания нет необходимости осуществлять точное, например, до половины младшего разряда, срав20 нение входного А и компенсирующего А аналоговых сигналов.

Достаточно на один такт поразрядного уравновешивания отводить время, необходимое для установления пере25 ходных процессов в ЦАП и блоке сравнения с погрешностью не более SQ . Значение SQ зависит от избыточности кода, который используется в ЦАП, и. определяется по формуле

30 8q 2сс - 1.

I

где oG - отношение межлу соседними членами кода, на основании которого построен ЦАП. .

Для числа Фибоначчи при , например, (о; 0,61803) погрешность Б Q , выраженная в %, равна 6Q 23,6%.

Работа аналого-цифрового преобразователя происходит в режиме метрологического контроля и в режиме непосредственного преобразования аналоговой величины в цифровой код.

В процессе метрологического контроля определяется наличие в устройстве отказавших разрядов, номера которых заносятся в регистр 8. Отказавшим считается неисправный разряд или разряд, вес которого не соответствует требуемому значению.

В режиме непосредственного преобразования входной аналоговой величины в цифровой код в работе участвуют блок 2 сравнения, цифро-аналоговый преобразователь 3, блок 11 управления, блок 4 вьщеления разности напряжений. Сдвиговый регистр 6, блок 5 логических элементов ИЛИ и блок 7 развертки

35

40

45

50

55

кода, блок 10 приведения кода к минимальной форме.

В режиме метрологического контроля участвуют все блоки устройства. Метрологический контроль аналого- цифрового преобразователя осуществляется на основании определенных соотношений между весами разрядов цифроаналогового преобразователя, вьтолненного в кодах с иррациональным основанием (коды Фибоначчи и коды золотой р-пропордии).

В режиме метрологического контроля в первом такте по сигналу блока 11 управления записывается единица в старший разряд блока 7 развертки кода обеспечивает тем самым включение старшего разряда цифроаналогового преобразователя 3. По следующему сигналу выполняется операция развертки первого разряда цифро- аналогового преобразователя 3. Блок 4 выделения разности напряжений осуществляет линейное преобразование разности первого и суммы второго и (p+l) -го разрядов цифроаналогового преобразователя 3. В случае превышения зтой разности значения допустимого предела блок 4 выделения разности напряжений вырабатьшает признак записи единицы в первый разряд регистра 8. В конце первого такта происходит сброс в нулевое состояние блока 7 развертки кода. На втором такте блок 11 управления запи- сьшает единицу вл второй разряд блока 7 развертки кода, обеспечивая тем самым включение второго разряда цифроаналогового преобразователя 3. Далее выполняется операция разверт- / ки второго разряда цифроаналогового преобразователя 3. Так же как и в первом такте блок 4 выделения разности напряжений вырабатьшает соответ- . ствующий сигнал, подаваемьй в блок 11 управления. В оставшихся (п-2) тактах схема работает аналогичным образом, обеспечивая последовательное включение и развертки оставших-. ся (п-2) разрядов цифроаналогового преобразователя, а также проверку - соотношения

J. (О

Если на i-M такте блок 4 в«еделе- ния разности напряжений срабатывает первый раз, то в i -и разряд регистра 8 записьшается единица, а в остальных разрядах остаются нули. .Если.

блок 4 выделения разности напряжений срабатывает на (i+1) такте, то в (1+1)-й разряд регистра 8 запи- сьгоается единица, а в i -и разряд записьшается ноль. Запись единицы в последутощие разряды и нулей в пре- дьщу1дие разряды происходит до тех пор, пока не перестанет срабатывать блок 4 вьщеления разности напряжений,

Прекращение срабатывания блока 4 свидетельствует о -выполнении соотношения (l). Таким образом, в регистре оказываются записаны номера расстроенных разрядов, При наличии отказавших разрядов метрологический контроль заканчивается проверкой возможности правильного преобразования входной величины в цифровой код. Если в процессе метрологического

контроля обнаружены отказавшие разряды, номера которых; занесены в регистр 8, то в процессе уравновешивания входного аналогового сигнала Ag компенсирующим сигналом А|

включение этих разрядов запрещает- ся. Кодирование же производится толь ко исправными точными разрядами.

Аналого-цифровой преобразователь осуществляет правильное преобразование входной аналоговой величины в цифровой код, если после каждой группы из m(I mg Р) подряд -расположенных отказавших разрядов -следует не менее m +1 младших точных разрядов или имеется не более одной группы из га () отказавших разрядов.

Однако уравновешивание k компенсирующим сигналом ЦАП при наличии отказавших разрядов должно вестись по медленному алгоритму. При зтом в регистре 6 занесена кодовая комбинация, все разряды которой равны нулю, В случае же применения

ускоренного алгоритма результат аналого-цифрового преобразования может быть неверным вследствие потери избыточности ЦАПЗ из-за наличия отказавших разрядов. Если в АЦП отсутствуют отказавшие разр1зды, то кодирование ведется по ускоренному алгоритму. При зтом аналого-цифровое преобразование происходит следующим образом. На первом такте преобразования входной аналоговой величины Ag, в код Kgy по сигналу блока 11 управления устанавливается в единичное состояние старший разряд

блока 7 развертки кода, а в сдвиговом регистре по сигналу блока 1 управления устанавливается кодовая комбинация Кдоп,.

Через блок 5 логических элементов ИЛИ кодовые комбинации К и Кд выходов сдвигового регистра 6 и блока 7 развертки кода поступают на вход ЦАЛ 3, на выходе которого появляется компенсирующий аналоговый сигнал Aj(, (Q,+ Qдon,) , где Qf,., - вес старшего разряда ЦДП.

Сравнение компенсирующего аналогового сигнала А к, и входного аналогового сигнала А производится при помощи блока 2 сравнения. Причем выходной сигнал YJ этого блока подчиняется следующему соотношению

Sje

ь.

если Ар AHJ если А г

При этом если на первом такте уравновешивания Y О, то (п-1)-й разряд устанавливается в нулевое состояние, если же Y 1, то (п-1)- разряд устанавливается в единичное состояние.

На втором такте аналого-цифрового преобразования по сигналу блока 1 управления содержимое блока 6 сдвигается на один разряд вправо, в результате чего на выходе сдвигового регистра появляется кодовая комбинация Кдо„2 Одновременно (п-2)-й разряд блока 7 развертки кода устаналивается в единичное состояние. При ЭТОМ на выходе ЦАП 3 появляется компенсирующий сигнал АХ-. В зависимост от результата сравнения выходного А и компенсирующего А аналоговых сигналов, (п-2)-й разряд устанавливается либо в нулевое состояние (Yj О), либо остается в единич- ном состоянии (Yj ) Работа аналого-цифрового преобразователя на любом -м такте происходит анало- - гично. Процесс непосредственного преобразования заканчивается на (п+1)-м такте поразрядного кодирования . При этом входной ана,поговый сигнал Ард уравновешен компенсирующим сигналом ЦАП А, с точностью до единицы младшего разряда ЦАП З.

Результат преобразования, сформированный в блоке 7 развертки кода, поступает в блок 10 приведения кода к минимальной форме, после чего нд

5

0

5

0

5

0

0

5

информационные выходные шины 12 устройства поступает код, представленный в минимальной форме.

Формула изобретения

1-Аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого является входной шиной, второй вход объединен с информационным .входом блока выделения разности напряжений и подключен к выходу цифроаналогового преобразователя, а выход подключен к первому входу блока управления, первые выходы которого подключены к управляющим входам блока вьщеления разности напряжений, выход которого подключен К второму входу блока управления, вторые вькоды которого подключены к первым информационным входам блока развертки кода, третьи выходы подключены к управляющим входам блока развертки кода, выходы которого подключены к соответствующим первым информационным входам блока логических элементов И, вторые информационные входы блока развертки кодов объединены с соответствующими вторь1ми информационными входами блока логических элементов И, третьими входами блока управления и подключе- ны к соответствующим выходам регистра, входы которого подключены к четвертым выходам блока, управления, пятый выход которого подключен к управляюще- му входу блока логических элементов И, выходы которого являются контрольными выходными шинами преобразователя, отличающийся тем, что, с целью повьшения быстродействия в него введены блок логических элементов ИЛИ, блок приведения кода к минимальной форме, сдвиговьш регистр, входы которого подключены к шестым выходам блока управления, выходы - к соответствующим первым входам блока логических элементов ИЛИ, выходы которого подключены к соответ ствующим входам цифроаналогового преобразователя, вторые входы объединены с соответствующими информационными входами блока приведения кода к минимальной форме и подключены к соответствующим выходам блока развертки кода,выходы блока приведения ,кода к минимальной форме являются информационными выходными шинами преобразователя, управляющие входы под

ключены к седьмым выходам блока управления, четвертый вход которого является шиной Режим работы.

2. Преобразователь по п.1, от - личающийся тем, что блок управления выполнен на мультиплексоре, блоке анализа кода, счетчике, дешифраторе, регистре, цифровом коммутаторе, генераторе тактовых импульсов, постоянном запоминающем устройстве, входы которого подключены к соответствующим выходам цифрового коммутатора, а выходы - к соответствующим информационным входам регистра, управляющий вход которого подключен к выходу генератора тактовых импульсов, выходы с первого по восьмой подключены к соответствующим входам дешифратора, выходы с девятог по одиннадцатый - к соответствующим управляющим входам мультиплексора, выходы с двенадцатого по шестнадцатый - к соответствующим первым информационным входам цифрового коммутатора, выходы с семнадцатого по двадцать первьй подключены к соответствующим вторым информационным вхсдам ;ифрового коммутатора, управляющий

1226664

12

вход которого подключен к выходу мультиплексора, первый, второй и третий информационные входы которого являются соответственно четвертым, первым и вторым входами блока управления, четвертый и пятый входы подключены соответственно к первому и .второму выходам блока анализа кода, входы которого являются третьими входами блока управления, шестой вход мультиплексора подключен к выходу счетчика, вход которого под- кл ючен к первому выходу дешифратора, второй и третий выходы которого яв- ляются первыми выходами блока управления, четвертый и пятый выходы которого являются шестыми выходами блока управления, шестой, седьмой и восьмой выходы - вторыми выходами блока управления, девятый и десятый выходы - третьими выходами блока управления, одиннадцатый, двенадцатый и тринадцатый выходы - четвертыми выходами блока управления,четыр- надцатый выход - пятым выходом блока управления, пятнадцатый и шестнадцатый выходы - седьмыми выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1288913A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU788372A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU758510A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

Изобретение позволяет повысить быстродействие аналого-цифрового преобразователя путем сокращения длительности такта кодирования и исключения возникающих при этом ощибок типа неправильное включение разряда или неправильное выключение разряда за счет использования избьггочных измерительных кодов. В режиме непосредственного преобразования входной аналоговой величины в цифровой код в работе участвуют блок сравнения, цифроаналоговый преобразователь, блок управления, блок выделения разности напряжений, сдвиговый регистр, блок логических элементов ИЛИ, блок развертки кода, блок приведения кода к минимальной форме. В режиме метрологического контроля участвуют все блоки устройства. По сигналу блока управления записьшает- ся единица в старший разряд блока развертки кода и обеспечивается тем самым включение старшего разряда цифроаналогового преобразователя. По следующему сигналу выполняется операция развертки первого разряда цифроаналогового преобразователя. Блок вьщеления разности напряжений осуществляет линейное преобразование разности первого и суммы второго и ( цифроаналогового преобразователя, где р параметр используемого избыточного измерительного кода. В случае превьппения этой разности значения допустимого предела блок вьщеления разности вырабатьюа- ет признак записи единицы в первый разряд регистра. В конце первого такта происходит сброс в нулевое состояние блока развертки кода. В оставшихся тактах схема работает аналогичным образом. 1 з.п.ф-лы, 5 ил., 2 табл. (Л с ю ю О) О) Од 4

О)

( Ценен

«Utt-l

. . - .5

Составитель В.Першиков Редактор А.Сабо Техред :В.Кадар Корректор А.Ференц

Заказ 2147/59 Тираж 816Подписное

ВНИИПИ Государствениого комитета СССР - по делам изобретений и откгялтий 113035, Москва, Ж-35, Раушская иаб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород, ул.Проектная,4

| Аналого-цифровой преобразователь | 1978 |

|

SU758510A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-23—Публикация

1984-04-21—Подача