(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для редактирования информации на экране электронно-лучевой трубки | 1983 |

|

SU1091153A1 |

| Устройство для контроля операционных усилителей в электронных блоках | 1988 |

|

SU1674018A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| Устройство для задания программы обучения | 1986 |

|

SU1310874A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Дискретный согласованный фильтр | 1980 |

|

SU871314A2 |

| Устройство для ввода учебной информации | 1990 |

|

SU1732369A1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

Устройство относится к радиоэлектроиике и может быть применено в различных устройствах контроля.

Известны коммутаторы, применяющиеся в- системах контроля, при обегающем контроле контролируемых точек , содержащие управляемые коммутационные элементы и обеспечивающие коммутацию входных сигналов по коммутирующим входам 1.

Однако в данных коммутаторах для обнаружения ошибки в коммутировании необходимо применять дополнительную обработку.

Наиболее близок к предлагаемому коммутатор, содержащий триггеры, диодный дешифратор и корректирующее устройство, каждый выход дешифратора через дифференцирующую цепь и схемы антисовпадения выбора отрицательного и положительного импульсов, вторые входы которых срединены со входом первого триггера коммутатора, соединен с шиной сброса триггеров , к которой также подключены попарно соседние выходы дешифратора через схемы антисовпадения и инвертор 2 .

Известный коммутатор позволяет мгновенно обнаружить ошибку. Однако

при ее обнаружении на определенном такте коммутации сбрасывается в исходное состояние и коммутатор повторяет предыдущие такты, при которых ошибок в работе коммутатора не произошло. При этом такт, в.котором произошла ошибка в работе коммутатора задерживается на время, необходимое для проведения предыдущих тактов.

10 Тактам коммутации соответствуют коммутируемые точки. Применение коммутатора вызывает значительную неравномерность моментов подключения контролируемых точек и снижение быстро15 .действия. Поэтому эффективность его работы при необходимости равномерного распределения моментов подключения контролируемых точек - низкая.

Цель изобретения повышение быст20родействия работы крммутатора.

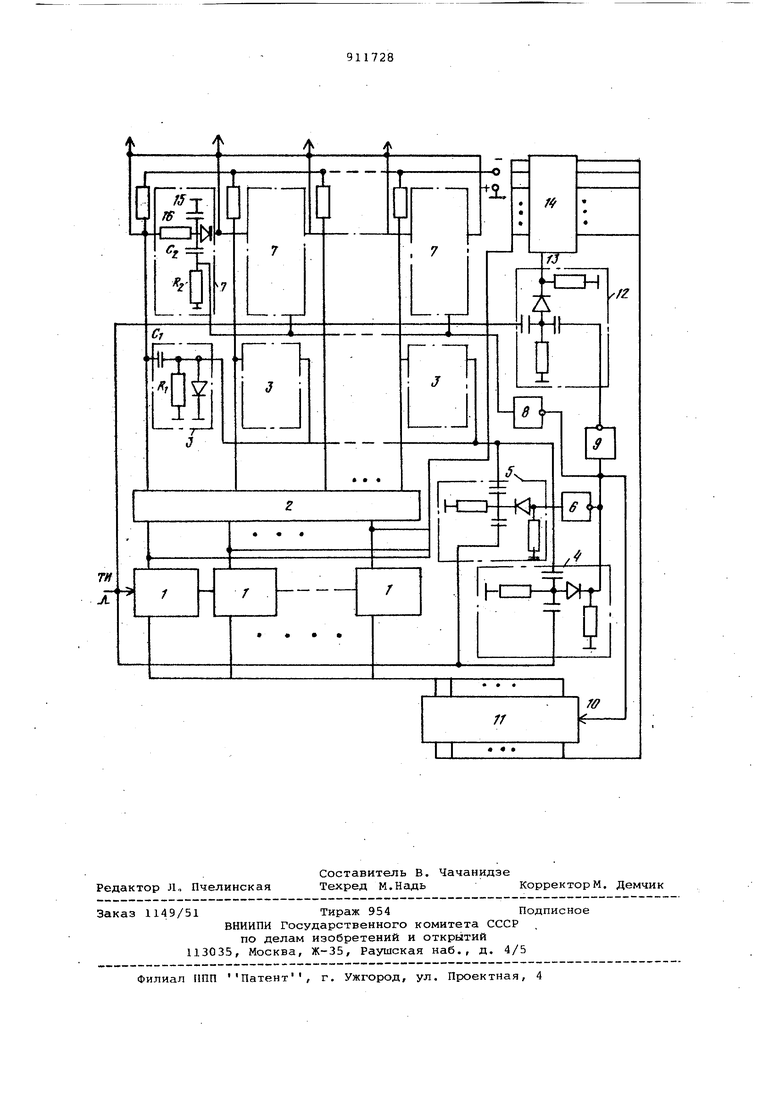

Поставленная цель достигается тем, что в коммутатор, содержащий триггеры и дешифратор, каждый выход которого соединен через дифференцирующую цепь со схемой айтисовпадания выбора положительного импульса и через схему антисовпадения выбора отрицательного импульса - со входом первого инвертора, вторые входы 0 схем антисовпадения выбора отрицательного и положительного импульсов подключены ко входу первого триггера, кроме этого, соседние выходы д€2шифратора попарно подключены через схемы антисовпадения выбора отрицательного импульса ко входу второго инвертора, введены дополнительная схема антисовпадения выбора положительного импульса/ вентильная t:xeMa, регистр, установочные входы которого соединены с соответствующими вьгходами триггеров, а синхронный вход подключен к выходу дополнительной схемы антисовпадения выбора положительного импульса, один вход которой соединен со входом первого триггера, другой - с выходом дополнительного инвертора, выходы регистра соединены со входами вентильной схемы, выходы которой подключены к соответствующим установочным входам триггеров, а ее синхронный вход соединен с выходами первого и второго инверторов, выходом схемы антисовпадения выбора положительного импульс 1 и входом дополнительного инвертора , На чертеже дана блок-схема предл гаемого коммутатора. Плечи триггеров 1, соединенных по счетной .схеме, подключены к дешифра тору 2 с К 2 выходами коммутирую щих потенциалов. Каждый выход дешиф ратора 2 через дифференцирующие цепи 3 подключен ко входам Охемы 4 ан тисовпадения выбора положительного импульса и схемы 5 совпадения выбора отрицательного импульса, вторые входы которых подключены ко входу первого триггера 1. Выход схемы 5 а тисовпадения подключен ко входу инвертора 6. I Каждый из соседних выходов комму тирующих шин попарно подключен к схемам 7 антисовпадения, выходы кот рых соединены со входом инвертора 8 Выходы инверторов 6 и 8 и выход схемы 4 антисовпадения подключены к входу дополнительного инвертора 9 и синхронному входу 10 вентильной схе мы 11 Выход дополнительной схемы 1 антисовпадения выбора положительного импульса, один вход которой подключен к выходу инвертора 9, другой ко входу первого триггера 1, соедин с синхронным входом 13 регистра 14. Установочные входы регистра 14 подключены к соответствующим выходам триггеров 1. Выходы регистра 14 соединены со входами вентильной схе мы 11, выходы которой подключены к соответствующим установочным входам триггеров 1, Постоянные времени цепей емкости 15 и резистора 16 схем 7, подключен ные к выходам дешифратора 2 с меньшим порядковым номером, больше в 10 раз постоянных времеяи цепей заряда емкости и регистра, подключеннЕзГх к соседним выходам дешифратора 2 с большими на единицу порядковыми номерами . Коммутатор работает следующим образом. Перед поступлением очередного тактового импульса в триггерах 1 и регистре 14 находится один и тот же код. В случае безошибочнойработы при поступлении тактового импульса на вход первого триггера 1 на соответствующем выходе дешифратора 2 появляется отрицательный коммутирующий потенциал. Продифференцированный схемой 3 передний фронт коммутирующего потенциала поступает на схемы 4 и 5 антисовпадения. В схемах 4 и 5 антисовпадения отрицательный импульс от дифференцирования переднего фронта коммутирующего потенциала компенсируется положительным тактовым импульсом (ТИ) и на синхронном входе 10 вентильной схемы 12 антисовпаденйя импульс не появляется, при этом на синхронный вход 13 регистра 14 через дополнительную схему антисовпадения 12 поступает ТИ и в регистр 14 записывается новый код из образованного триггерами счетчика. В схеме 7 антисовпадения медленно заряжается емкость 15 до максимального значения коммутирующего потенциала и на выходе дифференцирующей цепи 15,16 схемы 7 импульс не появляется. I В случае несрабатывания коммутатора от очередного ТИ, на выходе схемы 3 не появляется отрицательный импульс от дифференцирования переднего фронта коммутирующего потенциала и положительный ТИ,- пройдя через схему 4 антисовпадения и инвертор 9, поступает на один из входов схемы 12 антисовпадения и компенсирует положительный ТИ, поступающий на второй из входов схемы 12 антисовпадения. При этом на синхронный вход 13 регистра 14 импульс не поступает и в нем код не изменяется. Одновременно ТИ через схему 4 поступает на синхронный вход 10 вентильной схемы 11. При этом код из регистра 14, равный предыдущему коду счетчика, образованного триггерами 1, записывается в последний и в результате повторяется такт, в котором пррисходит сбой в работе коммутатора. В случае произвольного срабатывания коммутатора на выходе схемы 3 появляется отрицательный импульс от дифференцирования переднего фронта, коммутирующего потенциала, который через схему 5 антисовпадения и инвертор 6 поступает непосредственно на синхронный вход 10 вентильной схемы 11 и через инвертор 9 на один из входов схемы 12 антисовпадения, которая не пропускает его на синхронный вход 13 регистра 14 из-за со ответствующего включения диода. При этом код в регистре 14 не изменяетс Одновременно поступивший на синхрон ный вход 10 вентильной схемы 11 импульс открывает ее, код из регистра 11, равный предыдущему коду- счет чика образованного триггерами Г, записывается в последний и .в резуль тате повторяется такт, в котором происходит сбой в работе коммутатор В случае появления коммутирующего потенциала от очередного ТИ на любом выходе, кроме следующего, емкость 15 в схеме 7, включенной между выходом дешифратора 2у на котором по является коммутирующий потенциал, и предыдущим выходом с нулевым потенци алом, быстро заряжаетсячерез неболь шое прямое сопротивление диода. В результате дифференцирования крутого переднего фронта скачка зарядного потенциала емкости 15 на выходе дифференцирующей цепи 15,16 схемы 7 появляется отрицательный импульс, который через инвертор 8 поступает на вход инвертора 9 и синхронный вход 10 вентильной схеКол 11.- Дальнейшая работа коммутатора аналогична описанному выше случаю несрабатывания последнего от очередного ТИ. Таким образом, в случае сбоя видов, а именно: несрабатывания от очередного ТИ, самопроизвольное срабатывание или нарушение очередности срабатывания, предлагаемый коммутатор начинает работу не с начала цикла, а с того такта коммутации, при котором произошел сбой. При этом обеспечивается равномерное.подключение коммутируемых точек, соответ- ; ствующих тактам коммутации, что значительно увеличивает эффективность работы коммутатора. Формула изобретения Коммутатор, содержащий триггеры и дешифратор, каждый выход которого соединен черел дифференцирующую цепь со схемой антисовпадения выбора положительного импульса и через схему антисовпадения выбора отрицательного импульса - со входом первого инвертора, вторые входы схем антисовпадения выбора отрицательного и положительного импульсов подключены ко входу первого триггера, кроме этого, соседние выходы дешифратора попарно подключены через схемы антисовпащения выбора отрицательного импульса ко входу BTOpOj.0 инвертора, отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительная схема антисовпадения выбора положительного импульса, вентильная схема, регистр, установочные входы которого соединены с соответствующими выходами триггеров, а синхронный вход подключен к выходу дополнительной схе1чы антисовпадения выбора положительного импульса, один вход которой соединен со входом первого триггера, другой - с выходом дополнительного инвертора, выходы регистра соединены со входами вентильной схемы, выходы которой подключены к соответствующим установочным входам триггеров, а ее синхронный вход соединен с выходами первого и второго инверторов, выходом схемы антисовпадения выбора положительного импульса и входом дополнительного инвертора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 489115, кл. Н 03 К 17/00, 27.03.73. 2.Авторское свидетельство СССР . 329531, кл. Н 03 К 17/00,24.12.68 (прототип). .

Авторы

Даты

1982-03-07—Публикация

1980-06-02—Подача