Изобретение относится к тренажерам операторов систем управления и может быть использовано в качестве устройства управления тренажером операторов систем управления.

Цель изобретения - расширение дидактических возможностей устройства с повьппением эффективности управления тренажером,

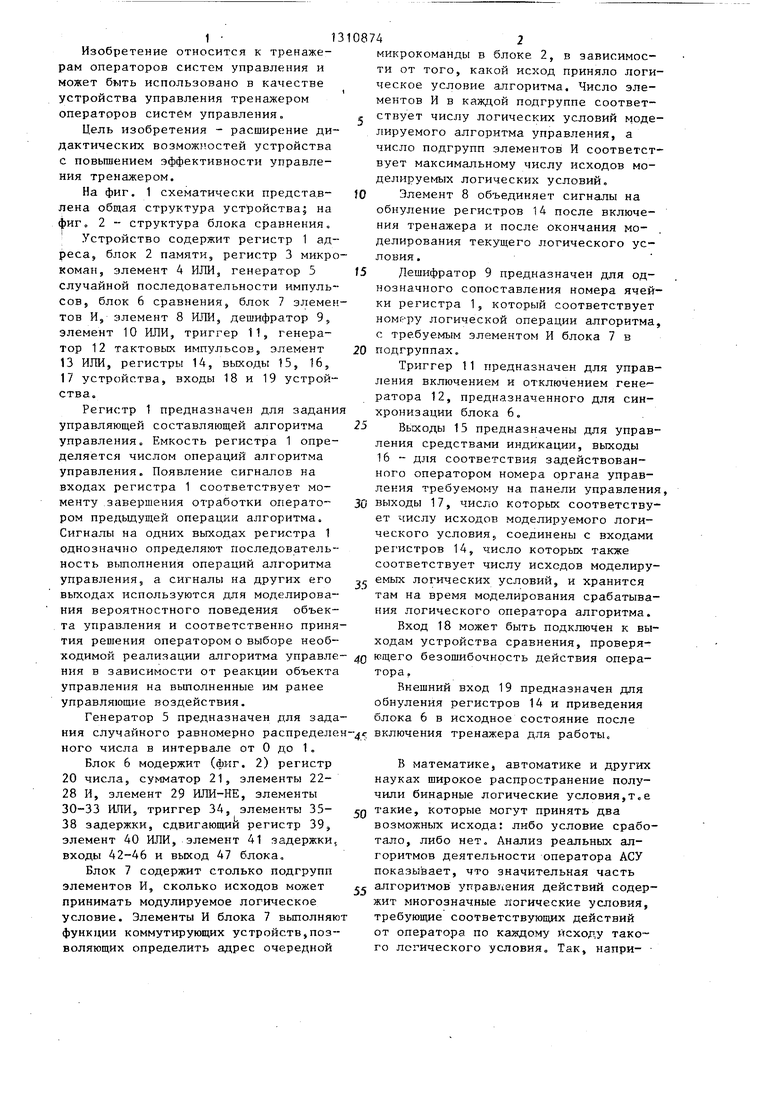

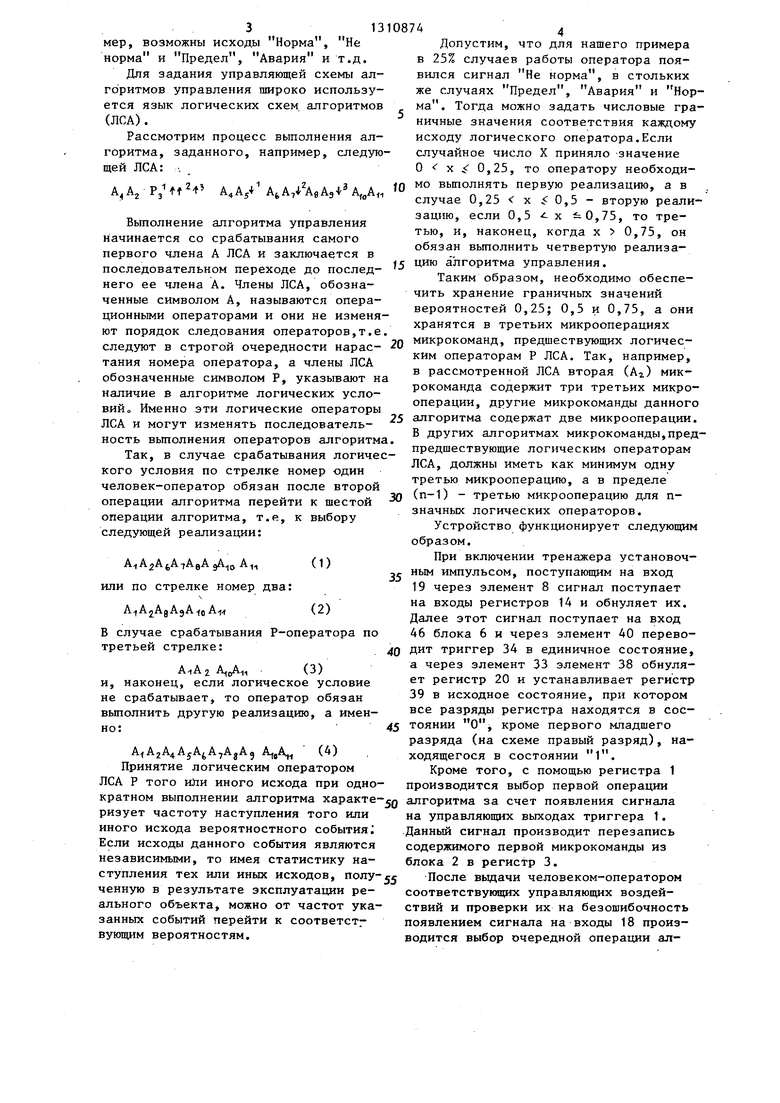

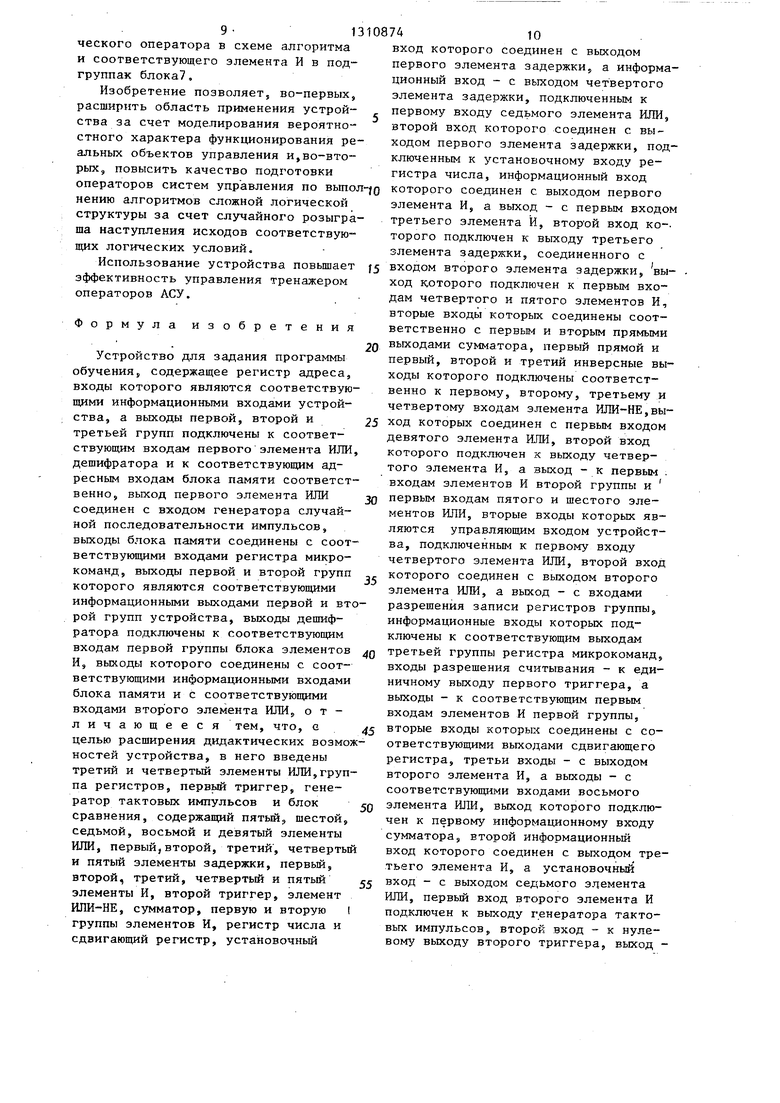

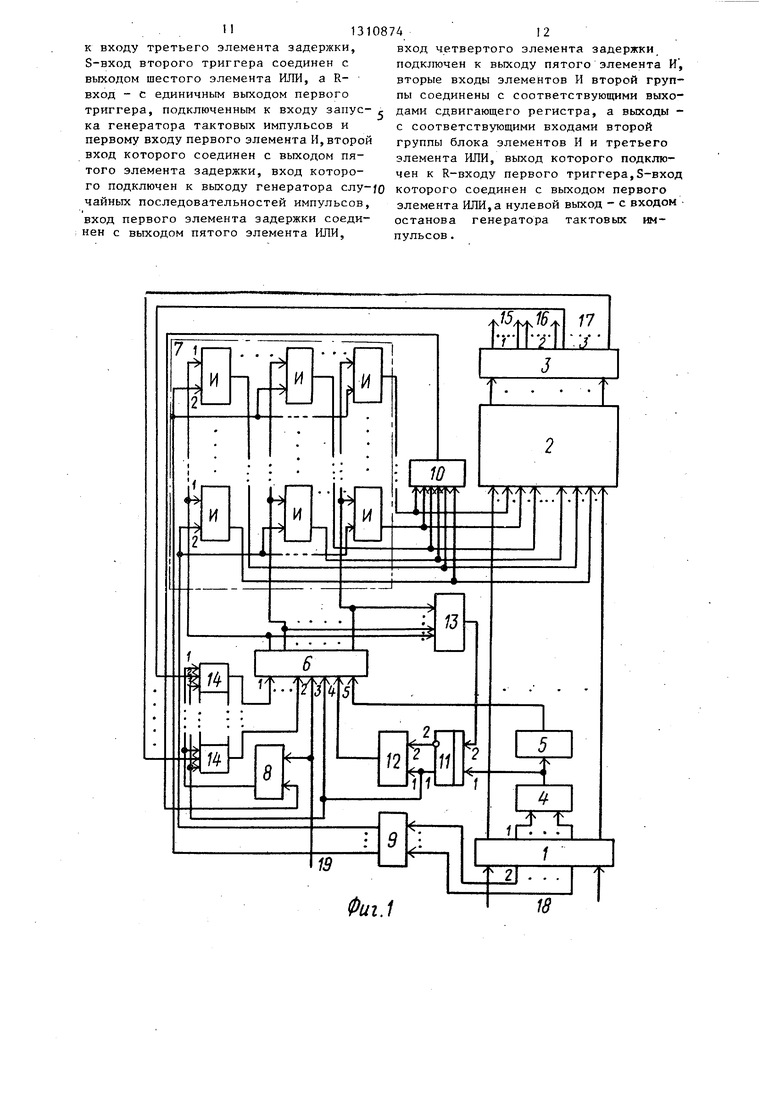

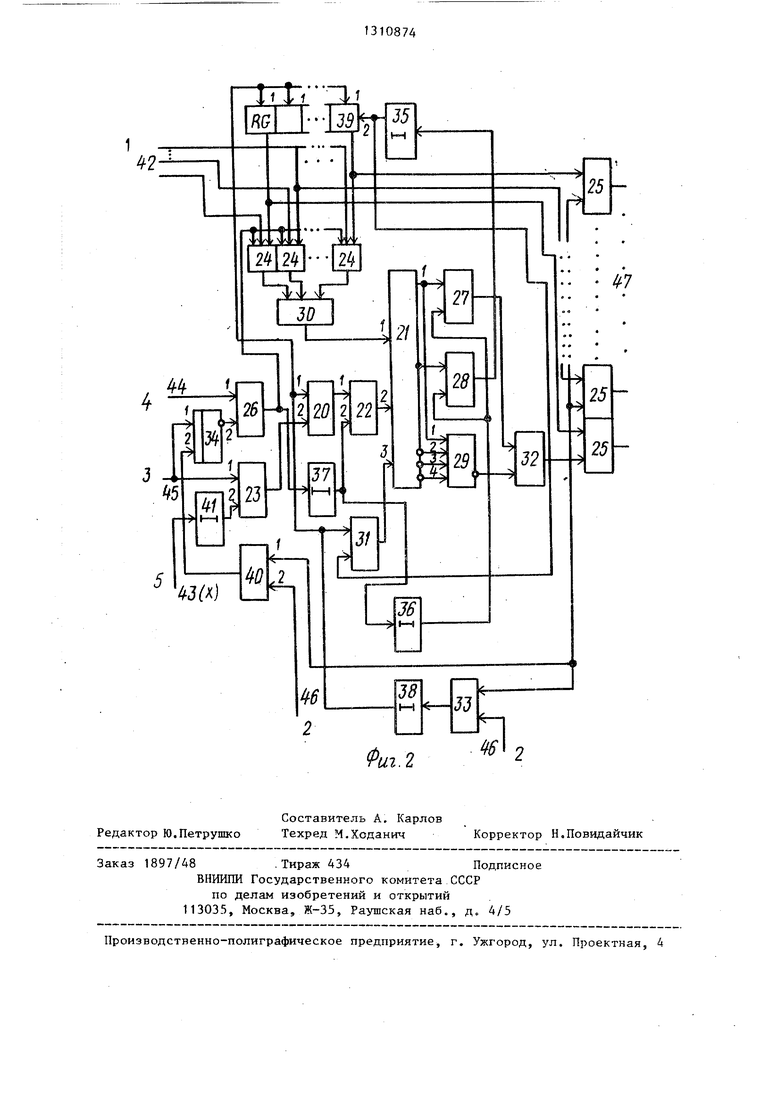

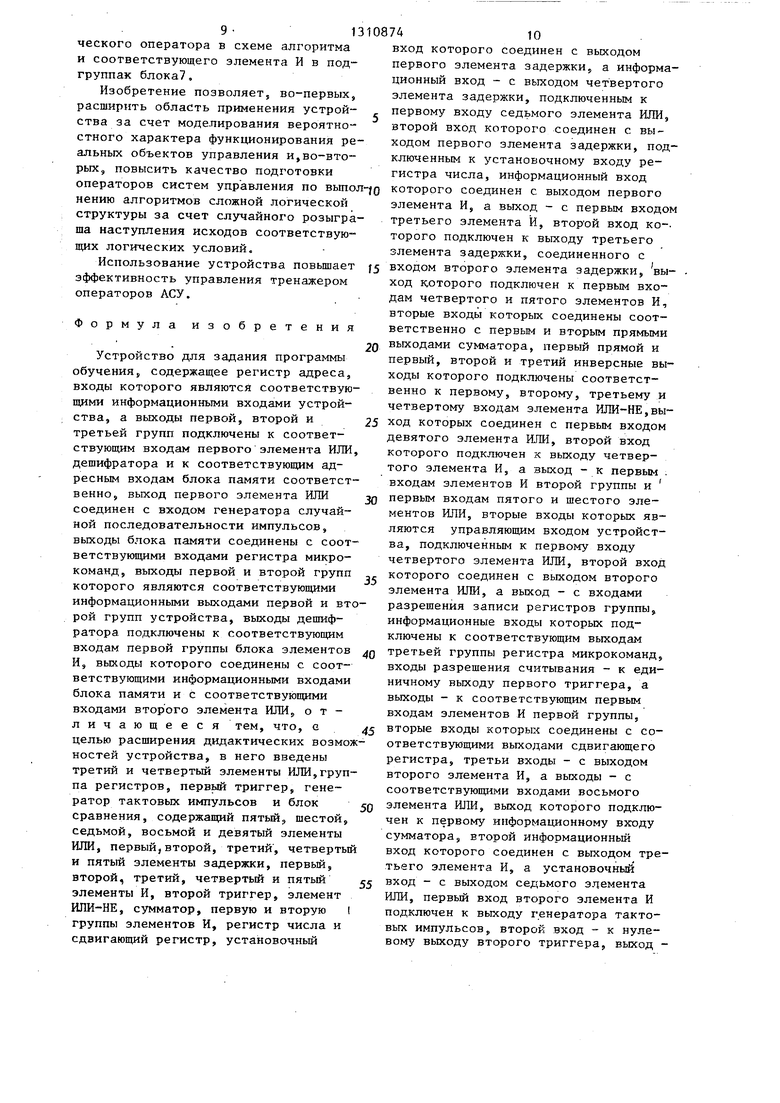

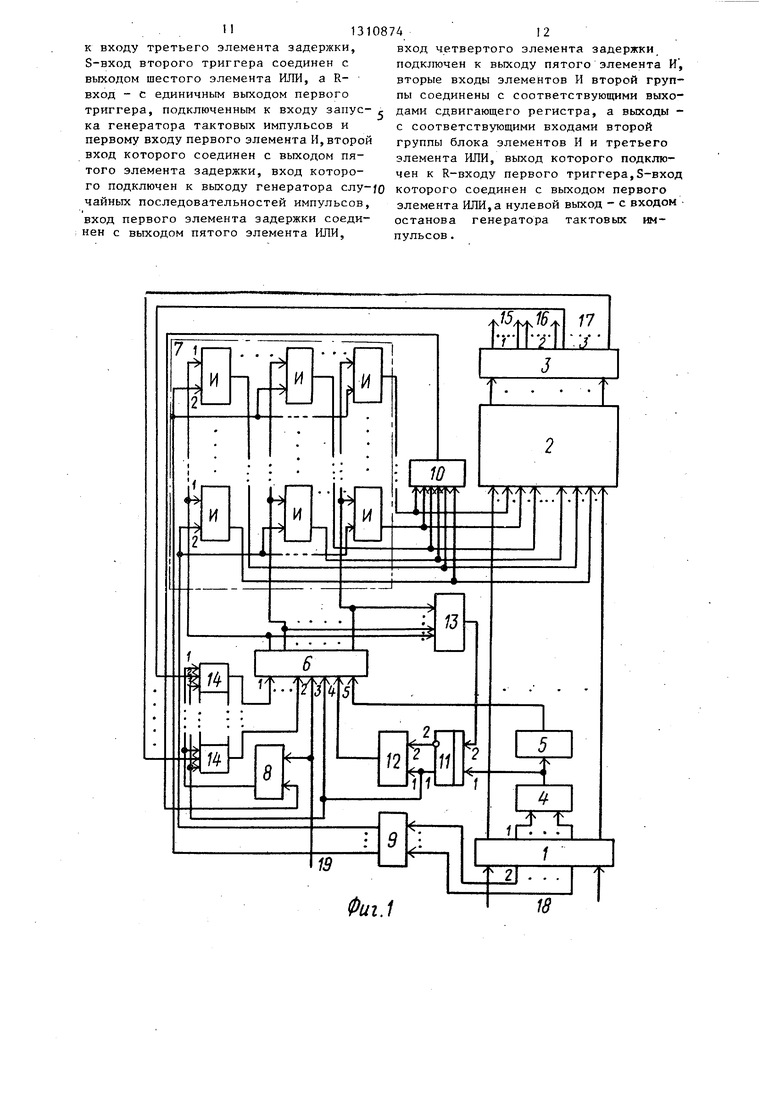

На фиг. 1 схематически представлена общая структура устройства; на фиг, 2 - структура блока сравнения.

Устройство содержит регистр 1 адреса, блок 2 памяти, регистр 3 микро коман, элемент 4 ИЛИ, генератор 5 случайной последовательности импульсов, блок 6 сравнения, блок 7 элементов И, элемент 8 ИЛИ, дешифратор 9, элемент 10 ИЛИ, триггер 11, генератор 12 тактовых импульсов, элемент 13 ИЛИ, регистры 14, выходы 15, 16, 17 устройства, входы 18 и 19 устройства.

Регистр 1 предназначен для задани управляющей составляющей алгоритма управления. Емкость регистра 1 определяется числом операций алгоритма управления. Появление сигналов на входах регистра 1 соответствует моменту .завершения отработки оператором предьщущей операции алгоритма. Сигналы на одних выходах регистра 1 однозначно определяют последовательность выполнения операций алгоритма управления, а сигналы на других его выходах используются для моделирования вероятностного поведения объекта управления и соответственно принятия репшния оператором о выборе необходимой реализации алгоритма управления в зависимости от реакции объекта управления на вьтолненные им ранее управляющие воздействия.

Внешний вход 19 предназначен обнуления регистров 14 и привед блока 6 в исходное состояние по

Генератор 5 предназначен для задания случайного равномерно распределен- : включения тренажера для работы. ного числа в интервале от О до 1.

Блок 6 модержит (фиг. 2) регистр 20 числа, сумматор 21, элементы 22- 28 И, элемент 29 ИЛИ-НЕ, элементы 30-33 ИЛИ, триггер 34, элементы 35- 38 задержки, сдвигающий регистр 39, элемент 40 ИЛИ, элемент 41 задержки, входы 42-46 и выход 47 блока,

Блок 7 содержит столько подгрупп элементов И, сколько исходов может принимать модулируемое логическое условие. Элементы И блока 7 вьшолняю функции коммутирующих устройств5позволяющих определить адрес очередной

микрокоманды в блоке 2, в зависимости от того, какой исход приняло логическое условие алгоритма. Число элементов И в каждой подгруппе соответствует числу логических условий моделируемого алгоритма управления, а число подгрупп элементов И соответствует максимальному числу исходов мо- делируег ых логических условий,

Элемент 8 объединяет сигналы на обнуление регистров 14 после включения тренажера и после окончания моделирования текущего логического условия,

Дешифратор 9 предназначен для однозначного сопоставления номера ячейки регистра 1, который соответствует номеру логической операции алгоритма, с требуемым элементом И блока 7 в

подгруппах.

Триггер 11 предназначен для управления включением и отключением генератора 12, предназначенного для синхронизации блока 6,

Вьосоды 15 предназначены для управления средствами индикации, выходы 16 - для соответствия задействованного оператором номера органа управления требуемому на панели управления,

выходы 17, число которых соответствует числу исходов моделируемого логического условия,, соединены с входами регистров 14, число которых также соответствует числу исходов моделируемых логических условий, и хранится там на время моделирования срабатывания логического оператора алгоритма.

Вход 18 может быть подключен к выходам устройства сравнения, проверяющего безошибочность действия оператора.

Внешний вход 19 предназначен для обнуления регистров 14 и приведения блока 6 в исходное состояние после

включения тренажера для работы.

В математике, автоматике и других науках широкое распространение получили бинарные логические условия,т,е

такие, которые могут принять два

возможных исхода: либо условие сработало, либо нет. Анализ реальных алгоритмов деятельности оператора АСУ показывает, что значительная часть

алгоритмов управления действий содержит многозначные логические условия, требующие соответствующих действий от оператора по каждому исходу такого логического условия. Так, напри-

313

мер, возможны исходы Норма, Не норма и Предел, Авария и т.д.

Для задания управляющей схемы алгоритмов управления широко используется язык логических схем алгоритмов (ЛСА).

Рассмотрим процесс выполнения алгоритма, заданного, например, следующей ЛСА: .

А,А, А,А,,А/АвАэ А,„А, ° вьшолнять первую реализацию, а в ., 23 45 foi-i случае 0,25 х 0,5 - вторую реализацию, если 0,5 - X -0,75, то третью, и, наконец, когда х 0,75, он обязан выполнить четвертую реализа- )5 цию алгоритма управления.

Таким образом, необходимо обеспечить хранение граничных значений

вероятностей 0,25; 0,5 и 0,75, а они хранятся в третьих микрооперациях

Выполнение алгоритма управления начинается со срабатывания самого первого члена А ЛСА и заключается в последовательном переходе до последнего ее члена А. Члены ЛСА, обозначенные символом А, называются операционными операторами и они не изменяют порядок следования операторов,т.е.

9п микрокоманд, предшествующих логичес- следуют в строгой очередности нарас- „ „

тания номера оператора, а члены ЛСА обозначенные символом Р, указывают на наличие в алгоритме логических условий Именно эти логические операторы ЛСА и могут изменять последовательность выполнения операторов алгоритма. Так, в случае срабатывания логического условия по стрелке номер один

КИМ операторам Р ЛСА. Так, например, в рассмотренной ЛСА вторая (А) микрокоманда содержит три третьих микрооперации, другие микрокоманды данного

25 алгоритма содержат две микрооперации В других алгоритмах микрокоманды,пред предшествующие логическим операторам ЛСА, должны иметь как минимум одну третью микрооперацию, а в пределе

человек-оператор обязан после второй операции алгоритма перейти к шестой операции алгоритма, т.е, к выбору следующей реализации:

AiAjA A AeAjA o А, (1)

или по стрелке номер два:

,

A AjiAgAgA e (2)

В случае срабатывания Р-оператора по третьей стрелке:

(3)

и, наконец, если логическое условие не срабатывает, то оператор обязан выполнить другую реализацию, а именно:

45 тоянии 0 кроме первого младшего разряда (на схеме правый разряд), н ходящегося в состоянии 1.

Кроме того, с помощью регистра 1 производится выбор первой операции

Принятие логическим оператором ЛСА Р того или иного исхода при однократном выполнении алгоритма характе- Q алгоритма за счет появления сигнала ризует частоту наступления того или на управляющих выходах триггера 1.

иного исхода вероятностного события Если исходы данного события являются независимыми, то имея статистику наступления тех или иных исходов, полу-55 ченную в результате эксплуатации реального объекта, можно от частот указанных событий перейти к соответствующим вероятностям.

Допустим, что для нашего примера в 25% случаев работы оператора появился сигнал Не норма, в стольких же случаях Предел, Авария и Норма . Тогда можно задать числовые граничные значения соответствия каждому исходу логического оператора,Если случайное число X приняло значение О X i 0,25, то оператору необходизацию, если 0,5 - X -0,75, то третью, и, наконец, когда х 0,75, он обязан выполнить четвертую реализа- цию алгоритма управления.

Таким образом, необходимо обеспечить хранение граничных значений

вероятностей 0,25; 0,5 и 0,75, а они хранятся в третьих микрооперациях

микрокоманд, предшествующих логичес- „ „

КИМ операторам Р ЛСА. Так, например, в рассмотренной ЛСА вторая (А) микрокоманда содержит три третьих микрооперации, другие микрокоманды данного

алгоритма содержат две микрооперации. В других алгоритмах микрокоманды,пред- предшествующие логическим операторам ЛСА, должны иметь как минимум одну третью микрооперацию, а в пределе

(п-1) - третью микрооперацию для п- значных логических операторов.

Устройство функционирует следующим образом.

При включении тренажера установочным импульсом, поступающим на вход 19 через элемент 8 сигнал поступает на входы регистров 14 и обнуляет их. Далее этот сигнал поступает на вход 46 блока 6 и через элемент 40 переводит триггер 34 в единичное состояние, а через элемент 33 элемент 38 обнуляет регистр 20 и устанавливает регистр 39 в исходное состояние, при котором все разряды регистра находятся в состоянии 0 кроме первого младшего разряда (на схеме правый разряд), находящегося в состоянии 1.

Кроме того, с помощью регистра 1 роизводится выбор первой операции

лгоритма за счет появления сигнала а управляющих выходах триггера 1.

Данный сигнал производит перезапись содержимого первой микрокоманды из блока 2 в регистр 3.

После выдачи человеком-оператором соответствующих управляющих воздействий и проверки их на безошибочность появлением сигнала на входы 18 производится выбор очередной операции ал5 1310874

горитма. Если очередная операция ал- ятностей х, горитма задана оператором А ЛСА, то сигналы будут появляться на управляющих выходах регистра 1 и цикл работы устройства повторится в описанном , порядке.

В случае, если отрабатывается оператор А ЛСА, предшествующий логическому оператору Р ЛСА, то дополнительно появится сигнал на выходах регист- fo pa 3 (в примере Aj ЛСА), поскольку данная микрокоманда содержит не толь- 1ко первую и вторую микрооперации, Но и столько третьих микроопераций, сколько значительное логическое уело- J5 вие разыгрывается, минус единица (в данном примере три третьих микроопе- рации).

Этим сигналом граничные значения .вероятностей принятия логическим one- 20 подгруппа элементов 24 (правая), ратором Р того или иного исхода пере- поскольку на эту подгруппу с тригге- записываются в регистры 14 (в рассмат- ра младшего разряда регистра 39 по- риваемом примере в три регистра из п ступает высокий потенциал. Значение имеющихся). ,первой границы х переписывается из

При отработке логического условия 25 регистра 14 через элемент 24, зле- Р ЛСА в качестве очередной операции мент 30 в сумматор 21. Тактовый им- алгоритма сигнал появляется на инфор- пульс поступает также по цепи на вход мационных выходах регистра 1, которые 44, элемент 26, элемент 37 на вход подключены к тем номерам ячеек реги- элемента 22, который производит пере- стра 1, которые соответствуют поряд- ЗО запись содержимого регистра 20 в сум- ковому номеру оператора Р в ЛСА (в матор 21 случайного числа х в обрат- примере - к ячейке 3), Через элемент ном коде. В зависимости от соотноше- 4 сигнал поступает на запуск генератора 5 (х) и на вход триггера 11,. сигнал с выхода которого запускает генератор 12, импульсы с которого поступают на вход 44 блока 6 н на входы регистров 14 для считывания информации с их выходов в блок 6.

,,x,...Xj, и соответствие его одной из указанных границ приведет к появлению сигналов на выходах 47, выходах элементов 25 одного из сигналов:

(х х)

(х X x,j)

(х X Xj)

(х„., X Xf,). .

В каждом цикле сравнения очередного случайного числа х с граничными значениями на вход 44 подается N тактовых импульсов (ТИ):ТИ 1, ТИ 2,..,; ,.., ТИ N, Тактовый импульс поступает через элемент 26 на одни входы элементов 24, на другие входы которых поступают сигналы с выходов реги- .стров 14. При этом открывается пер21 может находиться в одном из трех зг возможных состояний: отрицательный результат, когда х, х; отрицательный ноль, когда х X и положительный результат, когда х 7 х Состояние сумматора 21 анализируется элемен- Кроме того, сигнал с выхода триггера 0 .ми 27, 28, 29 и 32, 11 поступает на вход 45 блока 6.Если х 7 х, то в сумматоре 21 буСущность работы блока 6 заключает- дет положительный результат, откро- ся в последовательном сравнении слу- ется элемент 27 в такт поступит на чайного числа х, выработанного гене- элемент 32 и далее на элементы 25.

45 Однако из этих элементов открывается лишь первый (верхний) элемент групратором 5, с граничными значениями

(х,:

2 °

.,х) вероятностей срабатыпы.

так как на этот элемент поступавания того или иного исхода логического условия. Запись очередного чис- ет разрешающий потенциал с триггера ла X в регистр 20 и сравнение с гра- младшего (правого) разряда регистра ницами допусков производится от мень- Q 39, В результате, сигнал будет на шего значения к большему, т.е. выходе а (х х) „ Импульс с вькода элемента 27 поступает через элемент 32 и элемент 40 на вход триггера 34 и переведет его в единичное 55 состояние. При этом элемент 26 закроется и дальнейшее поступление тактов в блок 6 прекращается до начала новох :х2..., х„, и сравнение производится за п тактов генератора 12.

При подаче управляющего импульса на вход 45 очередное число х через элемент 41 поступает на вход элемента 23, ас его выхода - перезаписывается в регистр 20.. Сравнение значения числа X с граничными значениями верого цикла сравнения. Кроме того, с выхода элемента 27 сигнал через эле-

подгруппа элементов 24 (правая), поскольку на эту подгруппу с тригге- ра младшего разряда регистра 39 по- ступает высокий потенциал. Значение первой границы х переписывается из

,,x,...Xj, и соответствие его одной из указанных границ приведет к появлению сигналов на выходах 47, выходах элементов 25 одного из сигналов:

(х х)

(х X x,j)

(х X Xj)

(х„., X Xf,). .

В каждом цикле сравнения очередного случайного числа х с граничными значениями на вход 44 подается N тактовых импульсов (ТИ):ТИ 1, ТИ 2,..,; ,.., ТИ N, Тактовый импульс поступает через элемент 26 на одни входы элементов 24, на другие входы которых поступают сигналы с выходов реги- .стров 14. При этом открывается перпы.

так как на этот элемент поступает разрешающий потенциал с триггера младшего (правого) разряда регистра 39, В результате, сигнал будет на выходе а (х х) „ Импульс с вького цикла сравнения. Кроме того, с выхода элемента 27 сигнал через эле-71310874

мент 32, элемент 33, элемент 38,элемент 31 очищает сумматор 21. Далее сигнал с выхода элемента 38 поступает на вход регистра 20 и очищает его, и поступая также с выхода элемента 38 на входы регистра 39, приводит его в исходное состояние.

В случае, если х

ре 21 будет Отрицательный ноль,когда все триггеры сумматора находятся Q в единичном состоянии. Такое состояние суматора 21 выявляется элементом 29, входы которого подключены к нулевым выходам триггеров сумматора 21.

При наличии в сумматоре 21 Отрицательного нуля на выходе элемента 29 появится сигнал, который подается на элемент 32. и далее на входы элементов 25. Однако, при подаче тактов будет открыт лишь первый (верхний) элемент 25, что обеспечивается разрешающим потенциалом, поступающим с младшего (правого) разряда регистра 39. В результате, сигнал опять появит8

санным цепям сдвигают единицу в регистре 39 и очищают сумматор 21, подготавливая устройство к третьему такту сравнения.

Процесс сравнения случайного числа X с граничными значениями вероятнос- Xf, может продолжаться

теи х

1 суммато- до f-гo такта. В N-OM такте вьфабатывается сигнал а,

(х„. X

.),

если х.. X г х„. В этом случае будет . открыт N-й элемент.25, а остальные элементы блока 6 будут приведены в исходное состояние.

Пси появлении в одном из тактов 5 сравнения сигнала на выходе 47 он поступит на соответствующую подгруппу

20

элементов И блока 7, на первые их входы, а выбор конкретного элемента И в подгруппе будет обеспечен поступлением сигнала на его второй вход с выхода дешифратора 9, что позволяет однозначно сопоставить номер элемента И в подгруппе блока 7 номеру логического оператора Р в ЛСА при любом их количестве в алгоритм деятельности.

ся на выходе соответствующем а (х х).

Кроме того, по описанным цепям полученный сигнал приведет в исход-, ное состояние регистр 20, сумматор 21, регистр 39 и триггер 34.

Если же X х, то в сумматоре 21 будет отрицательный результат. При поступлении тактов открывается элемент 28, иМпульс с его выхода сдвигает на один разряд единицу в регистре 39 через элемент 35 и вход регистра 39 и сигналом с выхода элемента 35 по цепи через элемент 31 на вход сумматора 21 обнуляет его. В результате этого устройство будет подготовлено к второму такту сравнения.

При подаче второго такта осуществляется сравнение числа х с х. При этом работа устройства аналогична работе при поступлении первого такта, однако во втором такте в регистре 39 единица будет записана во втором (справа) триггера, поэтому при поступлении второго такта в сумматор 21 из

регистров 14 будет вьщано число Xj.

-7

На выходе 47 во втором такте вырабатывается сигнал aj (х х Xj), так как в элементах 25 во втором такте сравнения открыт второй (сверху) элемент И.

Если X Xj, то во втором такте импульсы с выхода элемента 28 по опи

8

санным цепям сдвигают единицу в регистре 39 и очищают сумматор 21, подготавливая устройство к третьему такту сравнения.

Процесс сравнения случайного числа X с граничными значениями вероятнос- Xf, может продолжаться

теи х

до f-гo такта. В N-OM такте вьфабаты

вается сигнал а,

(х„. X

.),

если х.. X г х„. В этом случае будет . открыт N-й элемент.25, а остальные элементы блока 6 будут приведены в исходное состояние.

Пси появлении в одном из тактов сравнения сигнала на выходе 47 он поступит на соответствующую подгруппу

0

5

5

элементов И блока 7, на первые их входы, а выбор конкретного элемента И в подгруппе будет обеспечен поступлением сигнала на его второй вход с выхода дешифратора 9, что позволяет однозначно сопоставить номер элемента И в подгруппе блока 7 номеру логического оператора Р в ЛСА при любом их количестве в алгоритм деятельности.

Сигнал с выхода задействованного элемента И блока 7 поступает на элемент 10 и через него обнуляет по пер- 0 вым входам содержание регистров 14, а также поступает на информационные входы блока 2 и выбирает в качестве очередной необходимую (в примере А/,

А, или Ац) микрооперацию для 5 представления оператору результата срабатывания логического условия и для принятия им соответствующего решения на вьщачу управляющего воздействия.

Кроме того, сигналы с выхода блока 6 поступают через элемент 13 на вход триггера 31, а сигнал с его выхода отключает генератор 12, возвращая устройство в исходное состояние до наступления очередного логического условия в алгоритме управления.

Алгоритмы управления могут содержать логические условия любой степени значности, последняя определит число 0 третьих микроопераций в микрокоманде регистра 3, разрядность регистра 39, число регистров 14 в группе, число подгрупп элементов И в блоке 7 и число элементов 24 и 25. Число логических операторов в алгоритме управления определяет число элементов И в подгруппах блока 7 и разрядность дешифратора 9, с помощью которого производится сопоставление номера логического оператора в схеме алгоритма и соответствующего элемента И в под- группак блока,

Изобретение позволяет, во-первых, расширить область применения устройства за счет моделирования вероятностного характера функционирования реальных объектов управления и,во-вторых, повысить качество подготовки

вход которого соединен с выходом первого элемента задержки, а информационный вход - с выходом четвертого элемента задержки, подключенным к первому входу седьмого элемента ИЛИ,

второй вход которого соединен с выходом первого элемента задержки, подключенным к установочному входу регистра числа, информационный вход операторов систем управления по вьтол-fQ которого соединен с выходом первого нению алгоритмов сложной логической элемента И, а выход - с первым входом структуры за счет случайного розыгра- третьего элемента И, второй вход ко-.

ша наступления исходов соответствующих логических условий.

Использование устройства повьшает f5 входом второго элемента задержки, выэффективность управления тренажером операторов АСУ.

Формула изобретения

Устройство для задания программы обучения, содержащее регистр адреса, входы которого являются соответствую щими информационными входами устройства, а выходы первой, второй и третьей групп подключены к соответствующим входам первого элемента ИЛИ, дешифратора и к соответствующим адресным входам блока памяти соответственно, выход первого элемента ИЛИ

ход которого подключен к первым входам четвертого и пятого элементов И, вторые входы которых соединены соответственно с первым и вторым прямыми

20 выходами сумматора, первый прямой и первый, второй и третий инверсные выходы которого подключены соответственно к первому, второму, третьему и четвертому входам элемента ИЛИ-НЕ,вы25 ход которых соединен с первым входом девятого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, а выход - к первым . входам элементов И второй группы и

30 первым входам пятого и шестого элементов ИЛИ, вторые входы которых являются управляющим входом устройства, подключенным к первому входу четвертого элемента ИЛИ, второй вход

30 первым входам пятого и шестого элементов ИЛИ, вторые входы которых яв ляются управляющим входом устройст ва, подключенным к первому входу четвертого элемента ИЛИ, второй вход

соединен с входом генератора случайной последовательности импульсов, выходы блока памяти соединены с соответствующими входами регистра микрокоманд, выходы первой и второй групп которого соединен с выходом второго которого являются соответствующими элемента ИЛИ, а выход - с входами информационными выходами первой и вто- разрешения записи регистров группы, рой групп устройства, выходы дешифратора подключены к соответствуюш 1М входам первой группы блока элементов Q И, выходы которого соединены с соответствующими информационными входами

информационные входы которых подключены к соответствующим выходам

третьей группы регистра микрокоманд входы разрешения считывания - к единичному выходу первого триггера, а выходы - к соответствующим первым входам элементов И первой группы, вторые входы которых соединены с соответствующими выходами сдвигающего регистра, третьи входы - с выходом второго элемента И, а выходы - с соответствуюш 1ми входами восьмого элемента ИЛИ, выход которого подключен к первому информационному входу сумматора, второй информационный вход которого соединен с выходом тре тьего элемента И, а установочный вход - с выходом седьмого элемента ИЛИ, первый вход второго элемента И подключен к вькоду генератора тактовых импульсов, второй вход - к нулевому вькоду второго триггера, выход

блока памяти и с соответствующими входами второго элемента ИЛИ, отличающееся тем, что, G

целью расширения дидактических возможностей устройства, в него введены третий и четвертый элементы ИЛИ,группа регистров, первый триггер, генератор тактовых импульсов и блок Q сравнения, содержащий пятый, шестой, седьмой, восьмой и девятый элементы ИЛИ, первый, второй, третий , четвертый и пятый элементы задержки, первый, второй, третий, четвертый и пятый элементы И, второй триггер, элемент ИЛИ-НЕ, сумматор, первую и вторую I группы элементов И, регистр числа и сдвигающий регистр, установочный

вход которого соединен с выходом первого элемента задержки, а информационный вход - с выходом четвертого элемента задержки, подключенным к первому входу седьмого элемента ИЛИ,

второй вход которого соединен с выходом первого элемента задержки, подключенным к установочному входу регистра числа, информационный вход которого соединен с выходом первого элемента И, а выход - с первым входом третьего элемента И, второй вход ко-.

торого подключен к выходу третьего элемента задержки, соединенного с

входом второго элемента задержки, в

ход которого подключен к первым входам четвертого и пятого элементов И, вторые входы которых соединены соответственно с первым и вторым прямыми

выходами сумматора, первый прямой и первый, второй и третий инверсные выходы которого подключены соответственно к первому, второму, третьему и четвертому входам элемента ИЛИ-НЕ,выход которых соединен с первым входом девятого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, а выход - к первым . входам элементов И второй группы и

первым входам пятого и шестого элементов ИЛИ, вторые входы которых являются управляющим входом устройства, подключенным к первому входу четвертого элемента ИЛИ, второй вход

которого соединен с выходом второго элемента ИЛИ, а выход - с входами разрешения записи регистров группы,

которого соединен с выходом второг элемента ИЛИ, а выход - с входами разрешения записи регистров группы

информационные входы которых подключены к соответствующим выходам

которого соединен с выходом второго элемента ИЛИ, а выход - с входами разрешения записи регистров группы, Q

5

Q

третьей группы регистра микрокоманд, входы разрешения считывания - к единичному выходу первого триггера, а выходы - к соответствующим первым входам элементов И первой группы, вторые входы которых соединены с соответствующими выходами сдвигающего регистра, третьи входы - с выходом второго элемента И, а выходы - с соответствуюш 1ми входами восьмого элемента ИЛИ, выход которого подключен к первому информационному входу сумматора, второй информационный вход которого соединен с выходом третьего элемента И, а установочный вход - с выходом седьмого элемента ИЛИ, первый вход второго элемента И подключен к вькоду генератора тактовых импульсов, второй вход - к нулевому вькоду второго триггера, выход ч1310874

к входу третьего элемента задержки, S-нход второго триггера соединен с выходом шестого элемента ИЛИ, а R- вход - с единичным выходом первого

в п в п

триггера, подключенным к входу запус- , дами сдвигающего регистра, а выходы - ка генератора тактовых импульсов и первому входу первого элемента И, второй вход которого соединен с выходом пятого элемента задержки, вход которого подключен к выходу генератора которого соединен с выходом первого чайных последовательностей импульсов, элемента ИЛИ,а нулевой выход - с входом вход первого элемента задержки соеди- останова генератора тактовых им- нен с выходом пятого элемента ИЛИ, пульсов.

с соответствующими входами второй группы блока элементов И и третьего элемента ИЛИ, выход которого подключен к R-входу первого триггера,S-вход

иг.1

12

вход четвертого элемента задержки подключен к выходу пятого элемента И , вторые входы элементов И второй группы соединены с соответствующими выходами сдвигающего регистра, а выходы - которого соединен с выходом первого элемента ИЛИ,а нулевой выход - с входом останова генератора тактовых им- ульсов.

с соответствующими входами второй группы блока элементов И и третьего элемента ИЛИ, выход которого подключен к R-входу первого триггера,S-вход

18

ЕЬ. ГЗи

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления тренажером операторов систем управления | 1984 |

|

SU1182566A2 |

| Устройство управления тренажером операторов систем управления | 1986 |

|

SU1363289A1 |

| Устройство управления тренажером операторов | 1989 |

|

SU1714645A1 |

| Устройство для управления тренажером операторов систем управления | 1983 |

|

SU1094046A1 |

| Устройство задания программы обучения | 1989 |

|

SU1681320A1 |

| Устройство для задания программы обучения | 1985 |

|

SU1320830A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для обучения операторов | 1988 |

|

SU1509972A1 |

Изобретение относится к тренажерам операторов систем управления и может быть использовано в качестве устройства управления тренажером операторов систем управления. Цель изобретения - расширение дидактических возможностей устройства с повышение эффективности управления тренажером за счет моделирования вероятностного характера функционирования реальных объектов управления. Цель достигается тем, что в известное устройство, содержащее регистр адреса, блок памяти, регистр микрокоманд, первый и второй элементы ИЛИ, генератор случайной последовательности импульсов, дешифратор и блок элементов И, введены третий и четвертый элементы ИЛИ, группа регистров, первый триггер, генератор тактовых импульсов и блок сравнения, содержащий пятый, шестой, седьмой, восьмой и девятый элементы ИЛИ, пять элементов эффекта, пять элементов И, второй триггер, элемент ИЛИ-НЕ, сумматор, две группы элементов И, регистр числа и сдвигающий регистр. Изобретение повышает качество подготовки операторов по выполнению алгоритмов сложной логической структуры за счет случайного ро- зыгрьш1а наступления исходов соответствующих логических условий. 2 ил. i С/) 00

Редактор Ю.Петрушко

Составитель А, Карлов

Техред М.Ходанич Корректор Н.Повидайчик

Заказ 1897/48 .Тираж 434Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная 4

| Устройство для управления тренажером операторов систем управления | 1983 |

|

SU1094046A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для управления тренажером операторов систем управления | 1984 |

|

SU1182566A2 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-31—Подача