(5) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕВЕРСИВНЫМ т-ФАЗНЫМ ШАГОВЫМ ЭЛЕКТРОДВИГАТЕЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многорежимного управления @ -фазным шаговым двигателем | 1987 |

|

SU1417161A1 |

| Реверсивный распределитель импульсов для управления @ -фазным шаговым электродвигателем | 1988 |

|

SU1541755A1 |

| Устройство для многорежимного управления @ -фазным шаговым двигателем | 1987 |

|

SU1511845A1 |

| Устройство для многорежимного управления @ -фазным шаговым двигателем | 1987 |

|

SU1610591A1 |

| Устройство для управления шаговым двигателем с четным числом фаз | 1989 |

|

SU1674342A1 |

| ЧЕТЫРЕХТАКТНЫЙ РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2010 |

|

RU2475933C2 |

| Устройство для управления шаговым двигателем | 1990 |

|

SU1741099A1 |

| Устройство для программного управления @ -фазным шаговым двигателем | 1990 |

|

SU1718187A1 |

| Распределитель импульсов для управления шаговым двигателем | 1986 |

|

SU1427545A1 |

| Распределитель импульсов для управления трехфазным шаговым двигателем | 1990 |

|

SU1705998A1 |

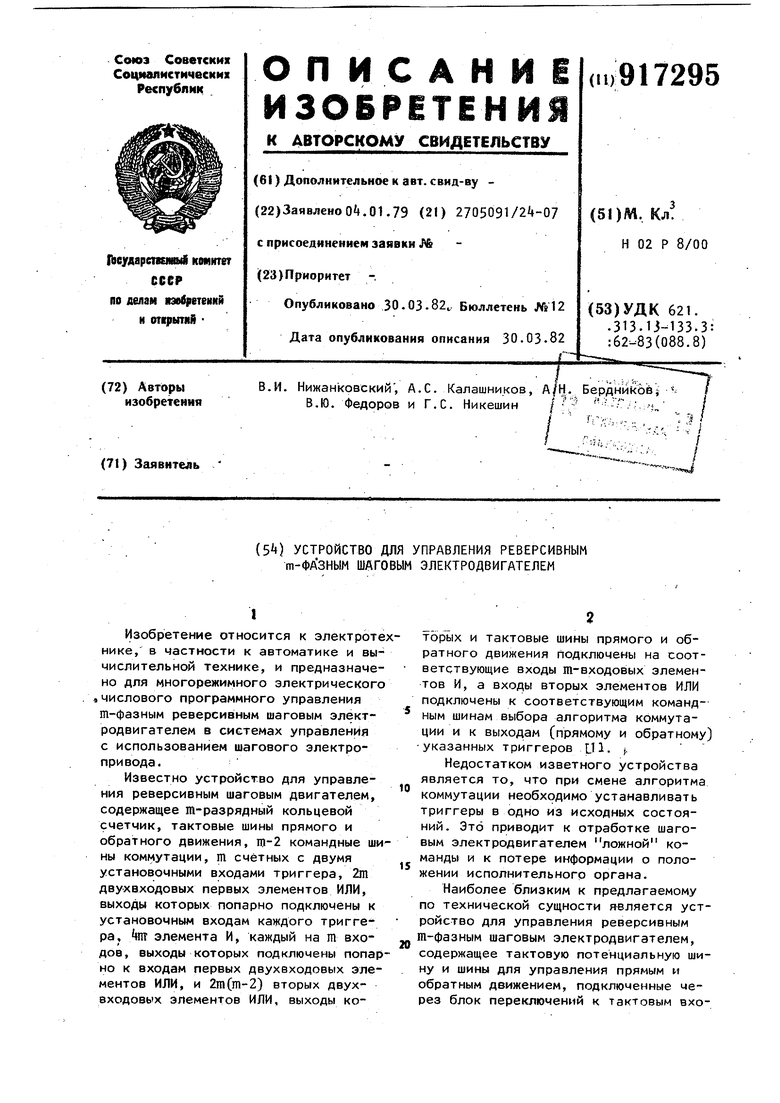

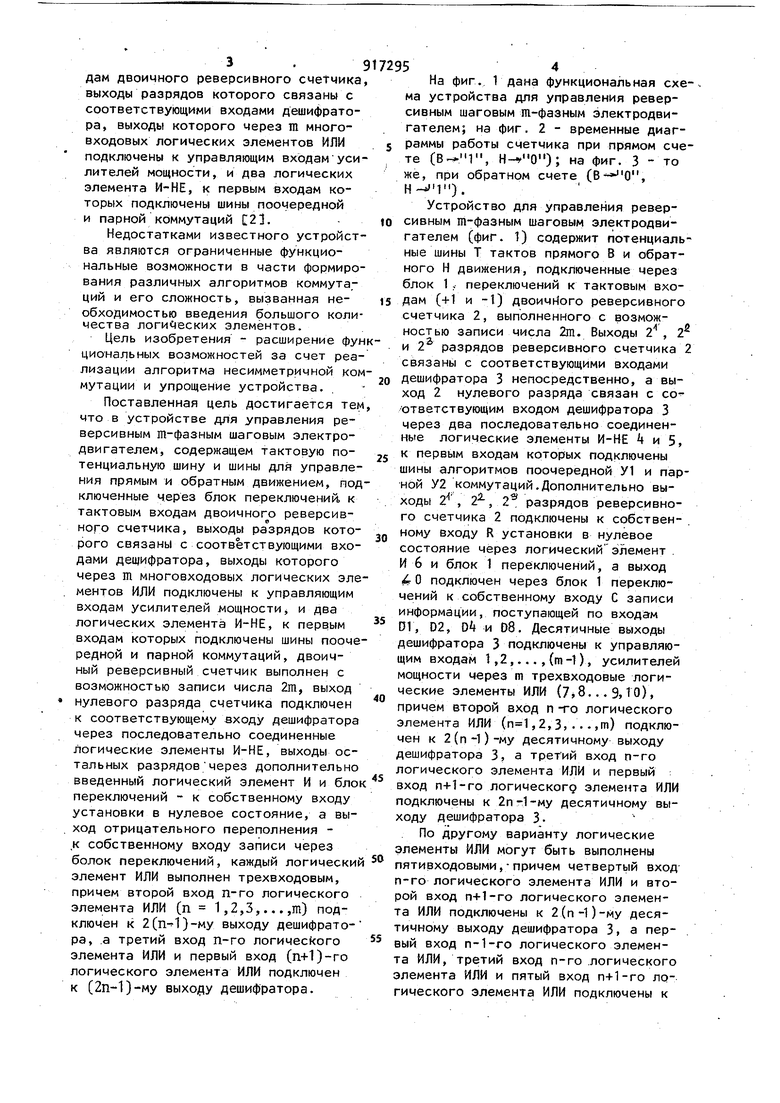

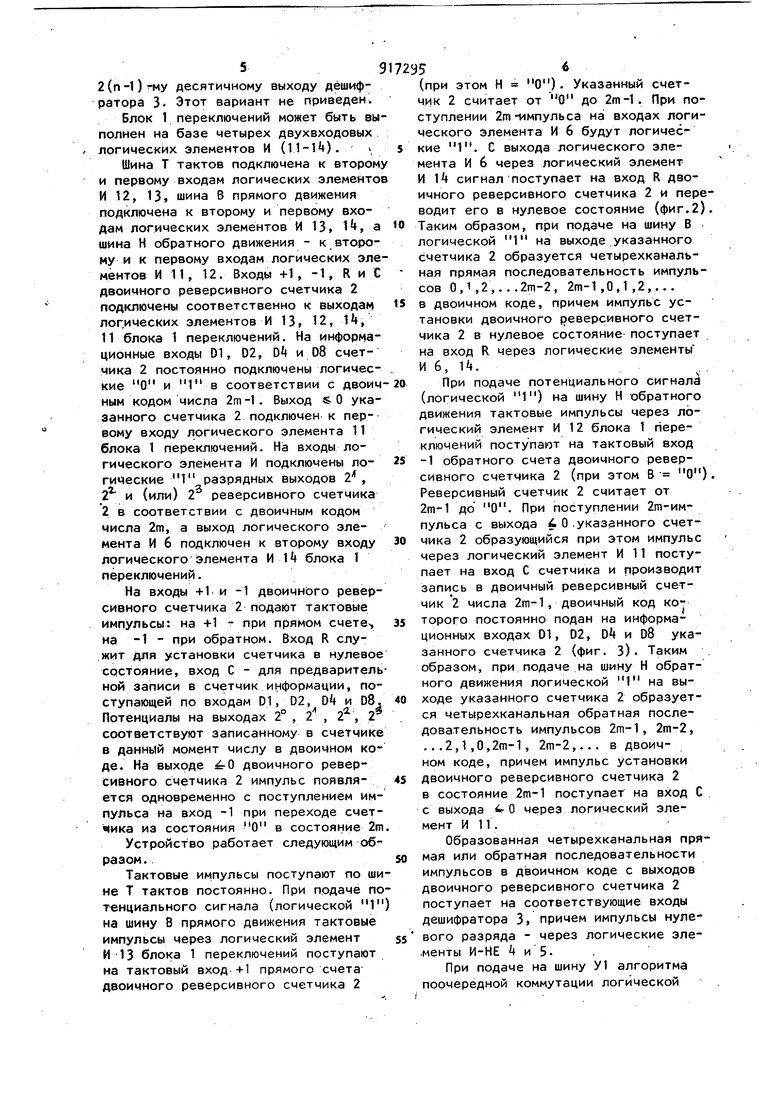

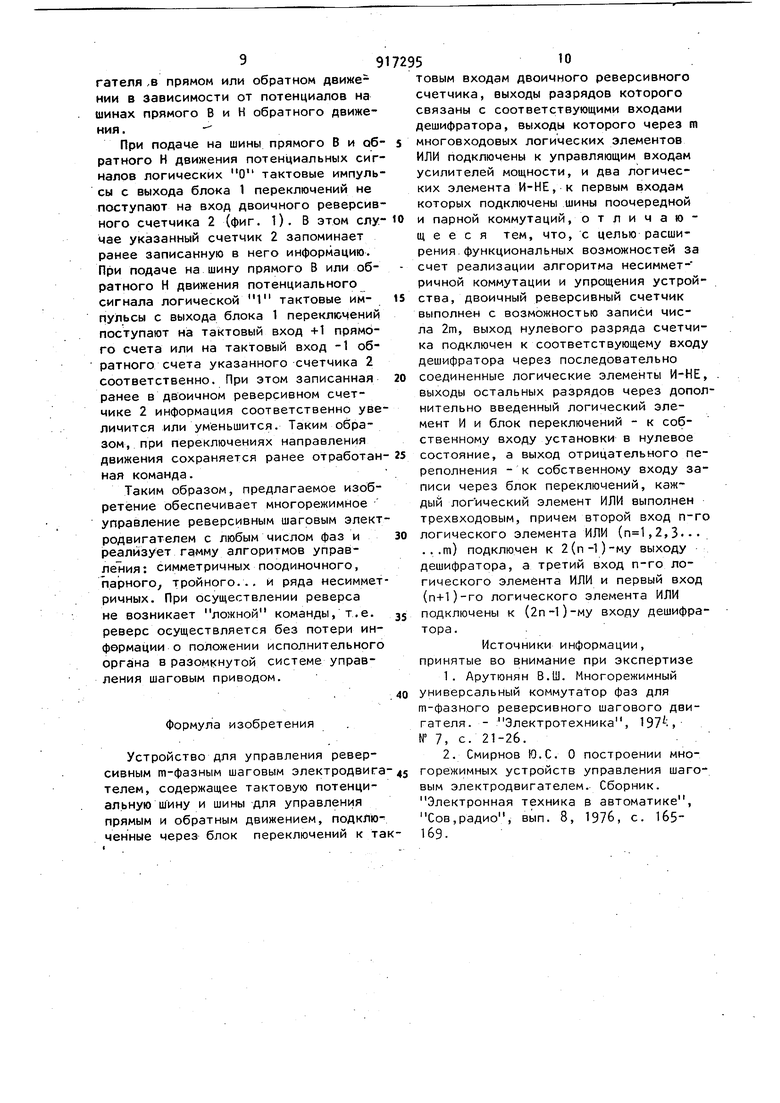

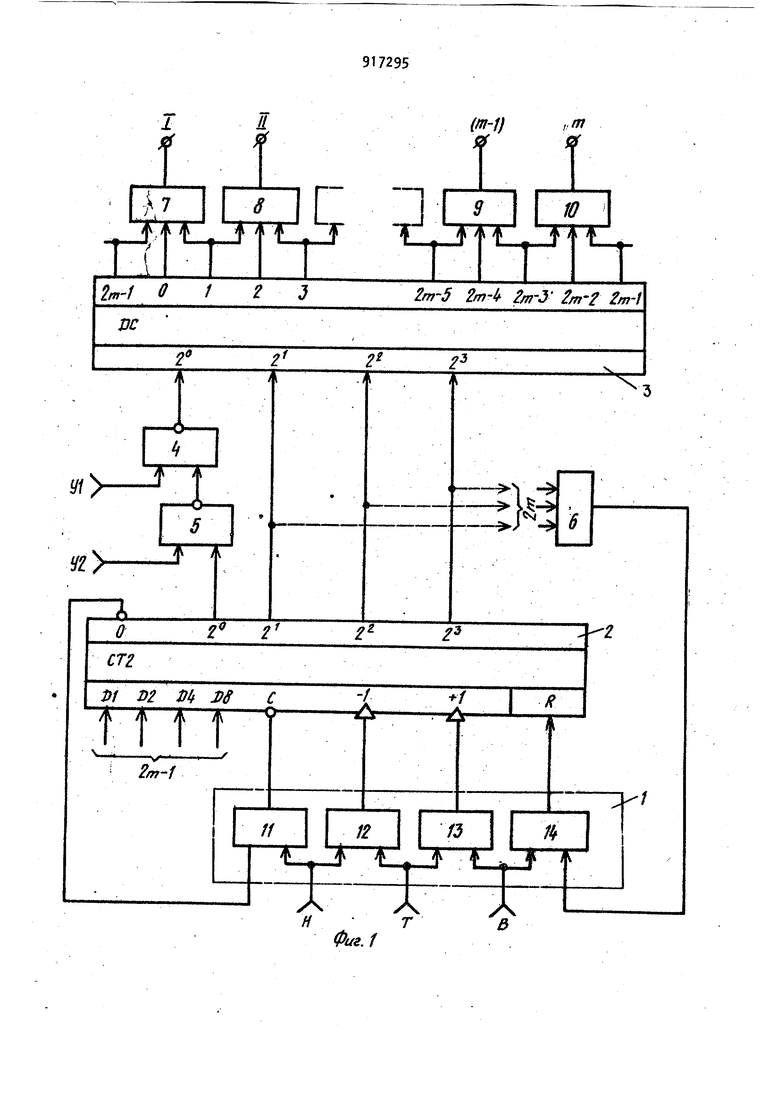

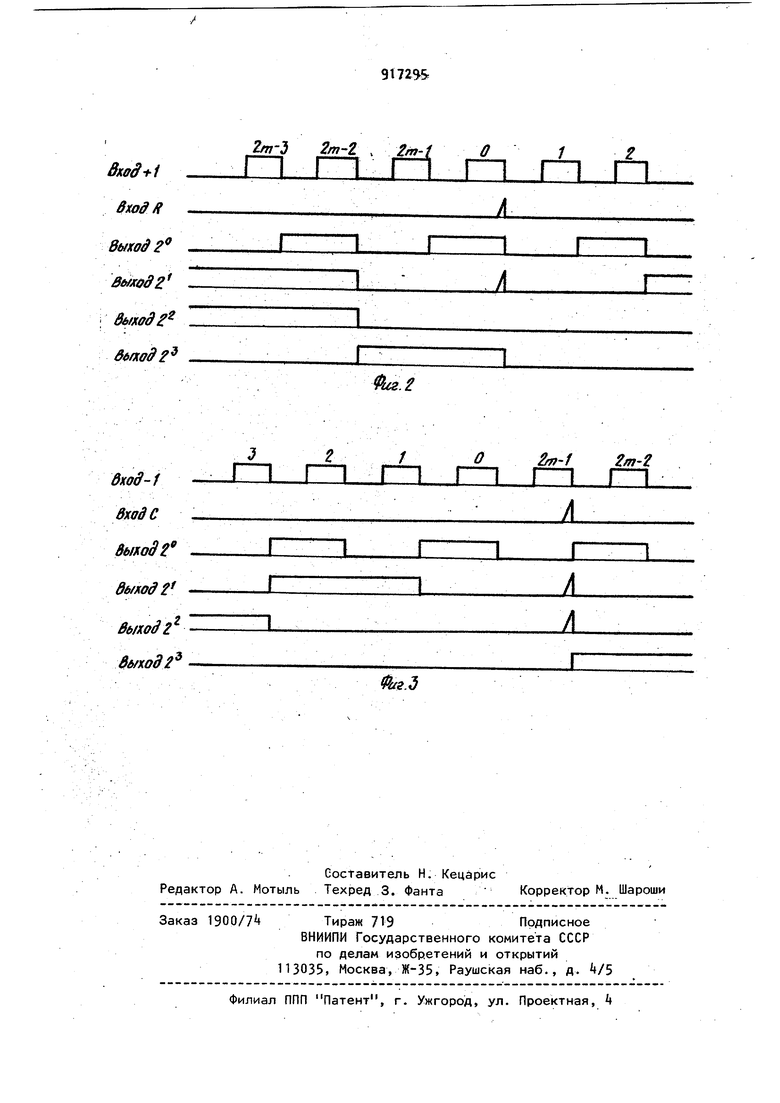

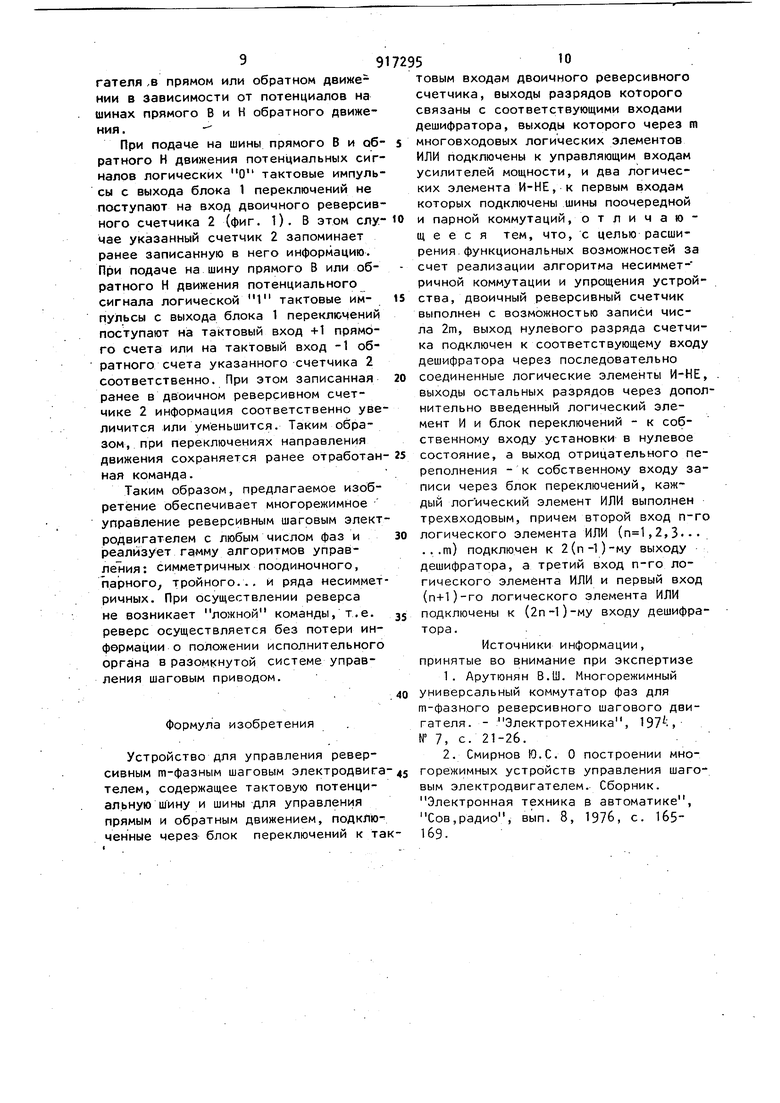

Изобретение относится к электроте нике, в частности к автоматике и вычислительной технике, и предназначено для многорежимного электрического числового программного управления т-фазным реверсивным шаговым электродвигателем в системах управления с использованием шагового электропривода. Известно устройство для управления реверсивным шаговым двигателем, содержащее т-разрядный кольцевой счетчик, тактовые шины прямого и обратного движения, nj-2 командные ши ны коммутации, m счётных с двумя установочными входами триггера, 2т двухвходовых первых элементов ИЛИ, выходы которых попарно подключены к установочным входам каждого триггера, km элемента И, каждый на m входов, выходы которых подключены попар но к входам первых двухвходовых элементов ИЛИ, и 2т(т-2) вторых двухвходовых элементов ИЛИ, выходы которых и тактовые шины прямого и обратного движения подключены на соответствующие входы т-входовых элементов И, а входы вторых элементов ИЛИ подключены к соответствующим командным шинам выбора алгоритма коммутации и к выходам (прямому и обратному) указанных триггеров 111.;. Недостатком изветного устройства является то, что при смене алгоритма коммутации необходимо устанавливать триггеры в одно из исходных состояний. Это приводит к отработке шаговым электродвигателем ложной команды и к потере информации о положении исполнительного органа. Наиболее близким к предлагаемому по технической сущности является устройство для управления реверсивным т-фазным шаговым электродвигателем, содержащее тактовую потенциальную шину и шины для управления прямым и обратным движением, подключенные через блок переключений к тактовым вхо3 . дам двоичного реверсивного счетчика выходы разрядов которого связаны с соответствующими входами дешифратора, выходы которого через го многовходовых логических элементов ИЛИ подключены к управляющим входам уси лителей мощности, и два логических элемента И-НЕ, к первым входам которых подключены шины поочередной и парной коммутаций С21. Недостатками известного устройст ва являются ограниченные функциональные возможности в части формиро вания различных алгоритмов коммутаций и его сложность, вызванная необходимостью введения большого коли чества логических элементов. Цель изобретения - расширение фун циональных возможностей за счет реализации алгоритма несимметричной ком мутации и упрощение устройства. Поставленная цель достигается тем что в устройстве для управления реверсивным т-фазным шаговым электродвигателем, содержащем тактовую потенциальную шину и шины для управления прямым и обратным движением, под ключенные через блок переключений к тактовым входам двоичного реверсивного счетчика, выходы разрядов которого связаны с соответствующими входами дешифратора, выходы которого через m многовходовых логических эле ментов ИЛИ подключены к управляющим входам усилителей мощности, и два логических элемента И-НЕ, к первым входам которых подключены шины пооче редной и парной коммутаций, двоичный реверсивный счетчик выполнен с возможностью записи числа 2т, выход нулевого разряда счетчика подключен к соответствующему входу дешифратора через последовательно соединенные логические элементы И-НЕ, выходы остальных разрядовчерез дополнительно введенный логический элемент И и бло переключений - к собственному входу установки в нулевое состояние, а выход отрицательного переполнения к собственному входу записи через болок переключений, каждый логически элемент ИЛИ выполнен трехвходовым, причем второй вход п-го логического элемента ИЛИ (п 1,2,3,...,т) подключен к 2(п-1)-му выходу дешифратора, .а третий вход п-го лoгичeckoгo элемента ИЛИ и первый вход (п+1)-го логического элемента ИЛИ подключен к (2п-1)-му выходу дешифратора. 5 На фиг. 1 дана функциональная схе-. ма устройства для управления реверсивным шаговым т-фазным электродвигателем; на фиг. 2 - временные диаграммы работы счетчика при прямом счете (В-.1, Н-ч--О); на фиг. 3 - то же, при обратном счете (, ). Устройство для управления реверсивным т-фазным шаговым электродвигателем (фиг. 1) содержит потенциальные шины Т тактов прямого В и обратного Н движения, подключенные через блок 1V переключений к тактовым входам (+1 и -1) двоичИого реверсивного счетчика 2, выполненного с возможностью записи числа 2т. Выходы 2 , 2 и 2 разрядов реверсивного счетчика 2 связаны с соответствующими входами дешифратора 3 непосредственно, а выход 2 нулевого разряда связан с со -ответствующим входом дешифратора 3 через два последовательно соединенные логические элементы И-НЕ 4 и 5, к первым входам которых подключены шины алгоритмов поочередной У1 и парной У2 коммутаций.Дополнительно выходы 2 , 2, 2 разрядов реверсивного счетчика 2 подключены к собствен- . ному входу R установки в нулевое состояние через логический элемент . И 6 и блок 1 переключений, а выход L О подключен через блок 1 переключений к собственному входу С записи информации, поступающей по входам D1, D2, о и D8. Десятичные выходы дешифратора 3 подключены к управляющим входам 1,2,.,., (т -1), усилителей мощности через m трехвходовые логические элементы ИЛИ (...9,10), причем второй вход п -го логического элемента ИЛИ (,2,3,,т) подключен к 2(п-1)-му десятичному выходу дешифратора 3, а третий вход п-го логического элемента ИЛИ и первый : вход П+1-ГО логического элемента ИЛИ подключены к 2пт1-му десятичному выходу дешифратора 3По другому варианту логические элементы ИЛИ могут быть выполнены пятивходовыми,-причем четвертый вход П-ГО логического элемента ИЛИ и второй вход П+1-ГО логического элемента ИЛИ подключены к 2(п-1)-му десятичному выходу дешифратора 3, а первый вход П-1-ГО логического элемента ИЛИ, третий вход п-го .логического элемента ИЛИ и пятый вход п+1-го логического элемента ИЛИ подключены к 2 (n -1) десятичному выходу дешифратора 3. Зтот вариант не приведен. Блок 1 переключений может быть вы полнен на базе четырех двухвходовых логических элементов И (ll-l). . Шина Т тактов подключена к втором и первому входам логических элементо И 12, 13, шина В прямого движения подключена к второму и первому входам логических элементов И 13, ft, а шина Н обратного движения - к второ му и к первому входам логических эле ментов И 11, 12. Входы +1, -1, R и С двоичного реверсивного счетчика 2 подключены соответственно к выходам логических элементов И 13, 12, 14, 11 блока 1 переключений. На информационные входы 01, D2, Dk и 08 счетчика 2 постоянно подключены логические О и 1 в соответствии с двоич ным кодом числа 2т-1. Выход «-О указанного счетчика 2 подключен к первому входу логического элемента 11 блока 1 переключений. На входы логического элемента И подключены логические 1 разрядных выходов 2 , 2 и (или) 2 реверсивного счетчика 2 в соответствии с двоичным кодом числа 2т, а выход логического элемента И 6 подключен к второму входу логического Элемента И I блока 1 переключений. На входы +1 и -1 двоичного реверсивного счетчика 2 подают taKTOBMe импульсы: на +1 - при прямом счете, на -1 - при обратном. Вход R служит для установки счетчика в нулевое состояние, вход С - для предваритель ной записи в счетчик и|;1формации, поступающей по входам 01, D2, О и 08. Потенциалы на выходах 2 соответствуют записанному в счетчике в данный момент числу в двоичном коде. На выходе 0 двоичного реверсивного счетчика 2 импульс появляется одновременно с поступлением импульса на вход -1 при переходе счетчика из состояния О в состояние 2т Устройство работает следующим образом. Тактовые импульсы поступают по ши не Т тактов постоянно. При подаче по тенциального сигнала (логической 1 на шину В прямого движения тактовые импульсы через логический элемент И-13 блока 1 переключений поступают на тактовый вход.+1 прямого счета двоичного реверсивного счетчика 2 5 (при этом Н О). Указанный счетчик 2 считает от О до 2т-1. При поступлении 2т-импульса на входах логического элемента И 6 будут логичес кие 1. С выхода логического элемента И 6 через логический элемент И Н сигнал лоступает на вход R двоичного реверсивного счетчика 2 и переводит его в нулевое состояние (фиг.2). Таким образом, при подаче на шину В логической 1 на выходе указанного счетчика 2 образуется четырехканальная прямая последовательность импульсов 0,1,2,...2т-2, 2т-1,0,1,2,... в двоичном коде, причем импульс установки двоичного реверсивного счетчика 2 в нулевое состояние поступает на вход R через логические элементы И 6, 1 4. При подаче потенциального сигнал (логической 1) на шину Н обратного движения тактовые импульсы через логический элемент И 12 блока 1 переключений поступают на тактовый вход -1 обратного счета двоичного реверсивного счетчика 2 (при этом В О). Реверсивный счетчик 2 считает от 2т-1 до О. При поступлении 2т-импульса с выхода О .указанного счетчика 2 образующийся при этом импульс через логический элемент И 11 поступает на вход С счетчика и производит запись в двоичный реверсивный счетчик 2 числа 2т-1, двоичный код ко торого постоянно подан на информационных входах 01, 02, 0 и 08 указанного счетчика 2 (фиг. 3). Таким образом, при подаче на шину Н обратного движения логической 1 на выходе указанного счетчика 2 образуется четырехканальная обратная последовательность импульсов 2т-1, 2т-2, .. .2,1,0,2т-1, 2т-2,... в двоичном коде, причем импульс установки двоичного реверсивного счетчика 2 в состояние 2т-1 поступает на вход С с выхода Q через логический элемент И 11. Образованная четырехканальная прямая или обратная последовательности импульсов в двоичном коде с выходов двоичного реверсивного счетчика 2 поступает на соответствующие входы дешифратора 3, причем импульсы нулевого разряда - через логические эле.менты И-НЕ 4 и 5. При подаче на шину У1 алгоритма поочередной коммутации логической 1, a на шину У2 алгоритма парной коммутации логического О с выхода лoгичeckoгo элемента И-НЕ на нуле вой разрядный вход 2 дешифратора 3 постоянно подан логический О. В этом случае на.входы дешифратора 3 поступает чётырехканальная прямая ил обратная последовательности четных импульсов двоичного кода, а с выходов дешифратора 3 на входы трехвходо вых логических элементов ИЛИ 7-10 по ступает последовательность импульсов, соответствующая четным числам 0,2,4,...2т7, 2т-2,0,2, - прямая, или 2m-2,2m-4,,..4,2,0, 2т-2, 2т-,... - обратная, в зависимости от потенциалов на шинах прямого В и обратного Н движения. При поступлении на входы трехвходовых логических, элементов ИЛИ 7-10 последовательности импульсов, соответствующей четным числам, на их. вы ходах формируется временная т-канальная последовательность импульсов, соответствующая-алгоритму т-тактной симметричной поочередной коммутации обмоток управления шагового электродвигателя: (1)-(2)-(З)-... -(т -1) -(т) -(1)-...- прямого дви жения, или (1)-(т)--(т-1)-... (З)-(2) -(1)-,.. -обратного движения в засисимости от потенциалов на шинах прямого В и обратного Н движении. При подаче на шину У1 алгоритма поччередной коммутации логического О с логического выхода элемента И-НЕ k на нулевой разрядный вход 2 дешифратора 3 постоянно подан сигнал логической 1. В этом случае на вхо ды дешифратора 3 поступает четырехканальная прямая или обратная последова.тельность нечетных импульсов дво ичного кода,а с выходов дешифратора 3 на входы трехвходовых логических элементов ИЛИ 7-10 поступает последовательность импульсов, соответствующая нечетным числам1,3,... 2m-3j 2m-l, 1,3,.-. - прямая, или 2т-1, 2m-3j... 3,1,2m-1, 2m-3,... обратная,в зависимости от потенциа. лов на шинах прямого В и обратного Н движений. При поступлении на входы трехвходовых логических элементов ИЛИ 7-10 последовательности импульсов, соответствуйщей нечетным числам, на их выходах формируется временная m канальная последовательность импуль5соответствующая алгоритму т-тактной симметричной парной коммутации обмоток управления шагового электродвигателя (12)-(23)-- (т-1-,(п)(т-1) -(12) -. .. - прямого движения, или (12) -(1) -(m,m-2) -. .. -(32) -(21) ... - обратного движения в зависимости от потенциалов на шинах прямого В и обратного Н движения. При подаче на шины У1 и У2 алгоритмов поочередной и парной коммутаций логических 1 с выхода логического элемента И 4 на нулевой разрядный вход 2 ° дешифратора 3 поступают тактовые импульсы с выхода 2 двоичного реверсивного счетчика 2. В этом случае на входы дешифратора 3 поступает чётырехканальная прямая или обратная последовательность импульсов двоичного кода (четных и нечетных), а с выхода дешифратора 3 на входы трехвходовых логических элементов ИЛИ 7-10 поступает последовательность импульсов, соответствующая числам натурального ряда 0,1, 2,3,... 2т-2, 2т-1 , 0,1,2,3 прямая, или 2т-1, 2т-2,...,3,2,1,0, 2т-1 , 2т-2,. .. - обратная, в зависимости от потенциалов на шинах прямого В и обратного Н движения. При поступлении на входы трехвходовых логических элементов ИЛИ 7-10 последовательности импульсов, соответствующей числам натурального ряда, на их выходах формируется временная т-канальная последовательность импульсов, соответствующая алгоритму 2т-тактной несимметричной коммутации обмоток управления шагового электродвигателя (1) -(12)-(2) -(23) -(3) -... .. . (т -1) -(т-1 ,т) -(т) -(ш -1) -(1) -.. . прямого движения, или (1) -(1т) -(ф) -(m,m-l) -(т-1) -...-(3)-(32) -(2) -(21) -(1) -... - обратного движения в зависимости от потенциалов на шинах прямого В и обратного Н движения. При выполнении логических элеменов ИЛИ пятивходовыми на их выходах оответственно формируются временые т-канальные- последовательности, мпульсов, соответствующие алгоритам т-тактной симметричной парной комутации (12)-(23)-(3)-...; т-тактой симметричной тройной коммутации (123) -(23) -( -... и 2т-тактной есимметричной коммутации (12)-(123)-(23) -(23) -(3) -... обмоток управения т-фазного шагового электродвигателя ,в прямом или обратном движении в зависимости от потенциалов на шинах прямого В и Н обратного движения . При подаче на шины прямого В и об ратного Н движения потенциальных сиг налов логических О тактовые импуль сы с выхода блока 1 переключений не поступают на вход двоичного реверсив ного счетчика 2 (фиг. 1). В этом слу чае указанный счетчик 2 запоминает ранее записанную в него информацию. При подаче на шину прямого В или обратного Н движения потенциального сигнала логической 1 тактовые импульсы с выхода блока 1 переключений поступают на тактовый вход +1 прямого счета или на тактовый вход -1 обратного счета указанного счетчика 2 соответственно. При этом записанная ранее в двоичном реверсивном счетчике 2 информация соответственно уве личится или уменьшится. Таким образом, при переключениях направления движения сохраняется ранее отработан ная команда. Таким образом, предлагаемое изобретение обеспечивает многорежимное управление реверсивным шаговым элект родвигателем с любым числом фаз и реализует гамму алгоритмов управпения: симметричных поодиночного, парного тройного... и ряда несиммет ричных. При осуществлении реверса не возникает ложной команды, т.е. реверс осуществляется без потери информации о положении исполнительного органа в разомкнутой системе управления шаговым приводом. Формула изобретения Устройство для управления реверсивным т-фазным шаговым электродвига телем, содержащее тактовую потенциальную шину и шины для управления прямым и обратным движением, подключенные через блок переключений к та товым входам двоичного реверсивного счетчика, выходы разрядов которого связаны с соответствующими входами дешифратора, выходы которого через m многовходовых логических элементов ИЛИ подключены к управляющим входам усилителей мощности, и два логических элемента И-НЕ, к первым входам которых подключены шины поочередной и парной коммутаций, о т л и ч а ю щ е е с я тем, что, с целью расширения, функциональных возможностей за счет реализации алгоритма несимметричной коммутации и упрощения устройства, двоичный реверсивный счетчик выполнен с возможностью записи числа 2т, выход нулевого разряда счетчика подключен к соответствующему входу дешифратора через последовательно соединенные логические элементы И-НЕ, выходы остальных разрядов через дополнительно введенный логический элемент И и блок переключений - к собственному входу установки в нулевое состояние, а выход отрицательного переполнения - к собственному входу записи через блок переключений, каждый логический элемент ИЛИ выполнен трехвходовым, причем второй вход п-го логического элемента ИЛИ (,2,3... ...т) подключен к 2(п-1)-му выходу дешифратора, а третий вход п-го логического элемента ИЛИ и первый вход (п+1)-го логического элемента ИЛИ подключены к (2п-1)-му входу дешифратора. Источники информации, принятые во внимание при экспертизе 1.Арутюнян В.Ш. Многорежимный универсальный коммутатор фаз для т-фазного реверсивного шагового двигателя. - Электротехника, , If 7, с. 21-26.. 2.Смирнов Ю.С. О построении многорежимных устройств управления шаговым электродвигателем. Сборник, Электронная техника в автоматике, Сов,радио, вып. 8, 1976, с. 1б5 1б9.

I

Г J

H Т

фиг. 1

(fn-f),m

LJ

В

Авторы

Даты

1982-03-30—Публикация

1979-01-04—Подача