(54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема последовательного кода | 1980 |

|

SU907569A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 1992 |

|

RU2037264C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1606991A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1983 |

|

SU1105884A1 |

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

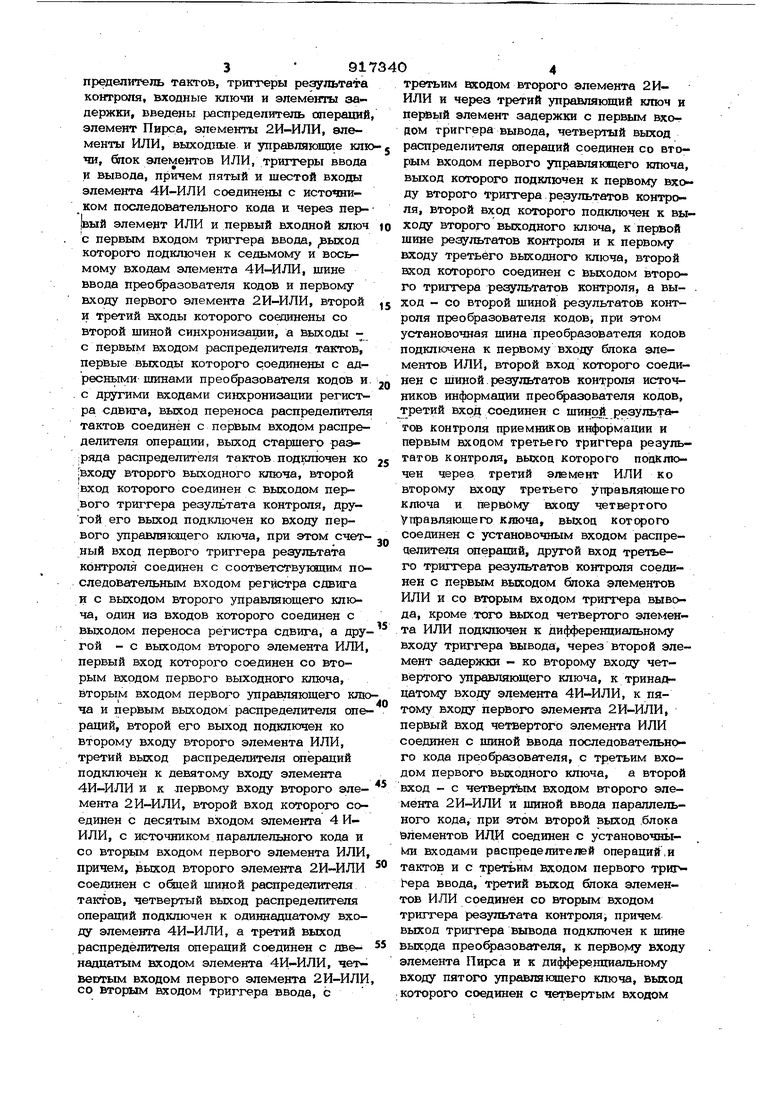

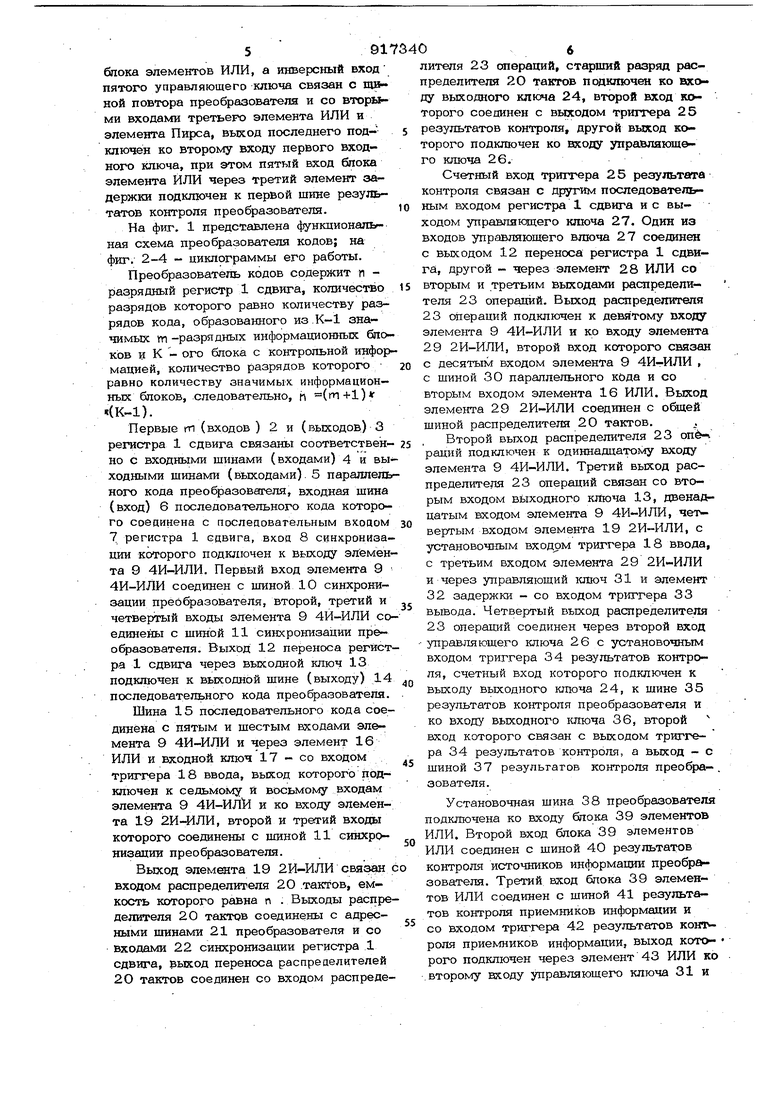

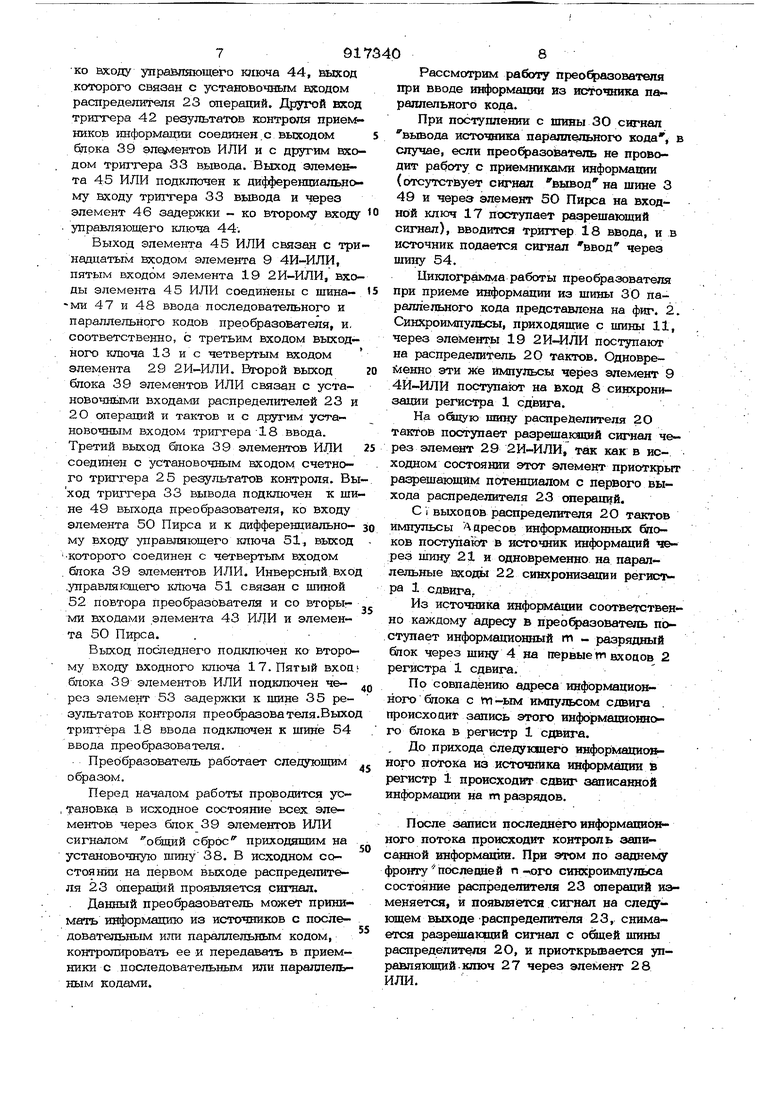

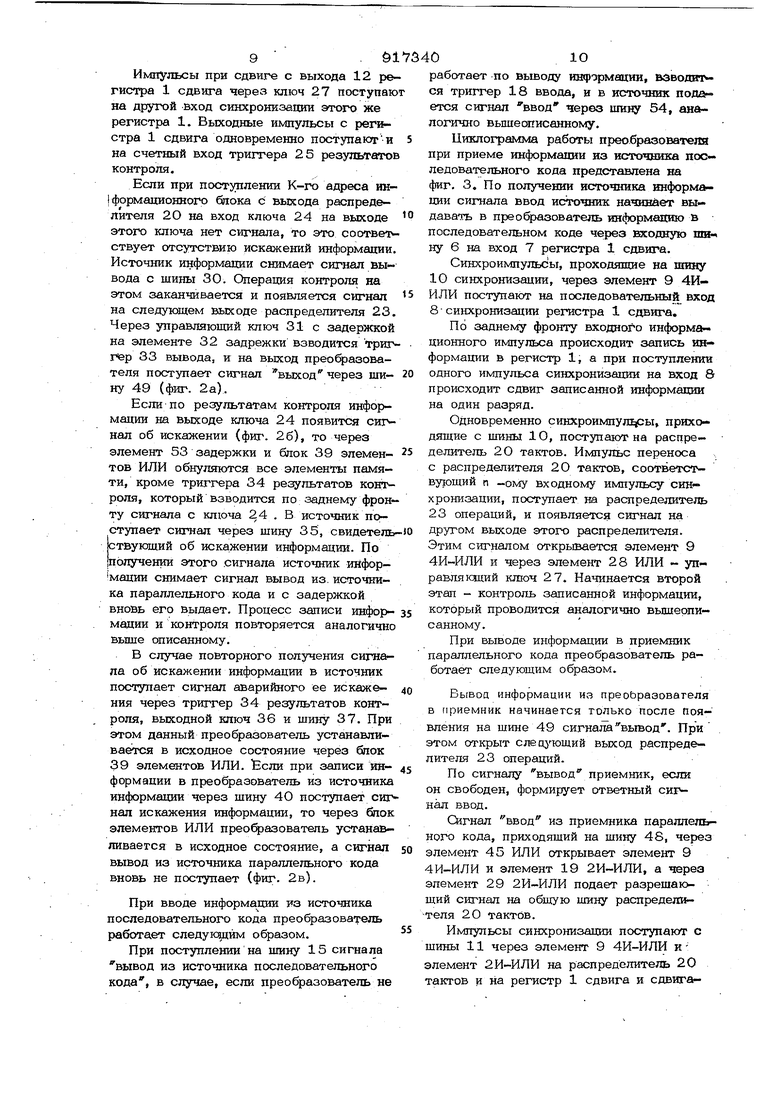

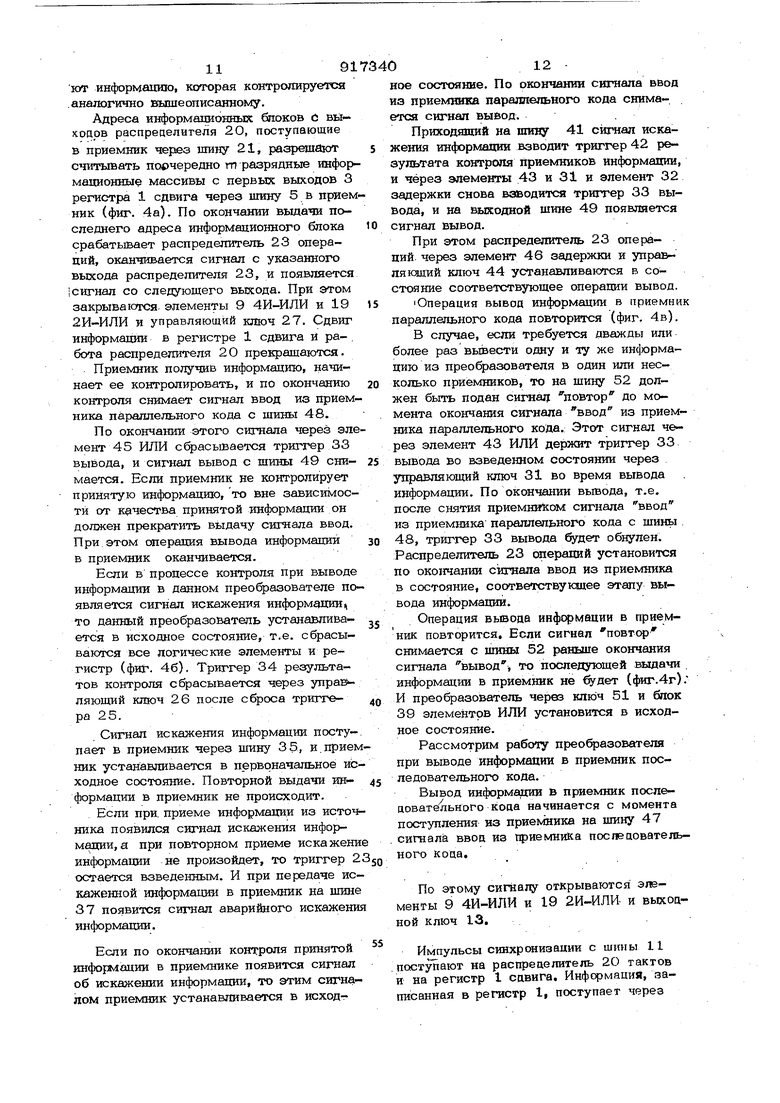

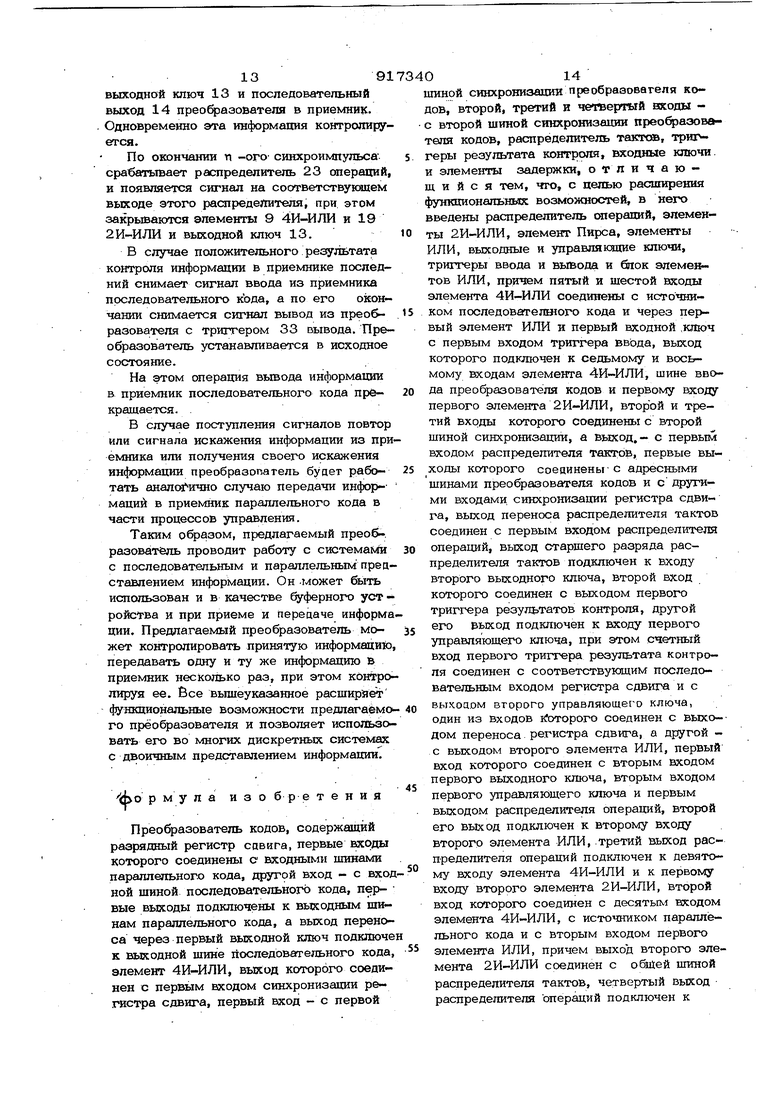

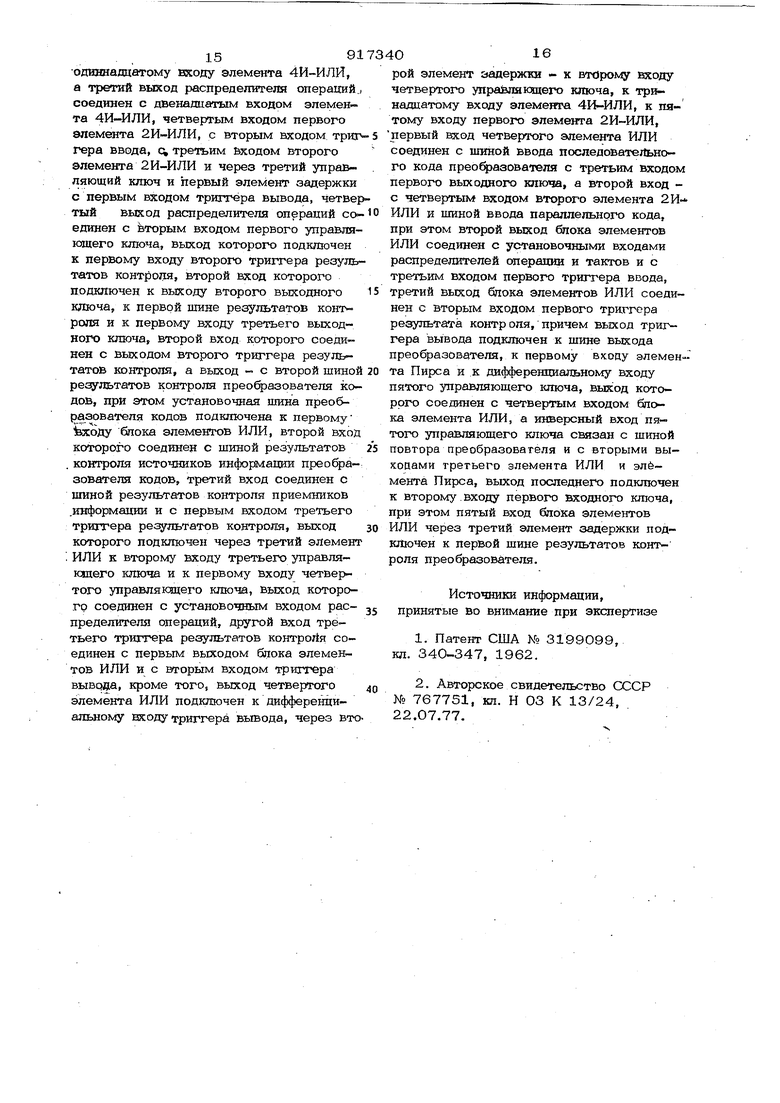

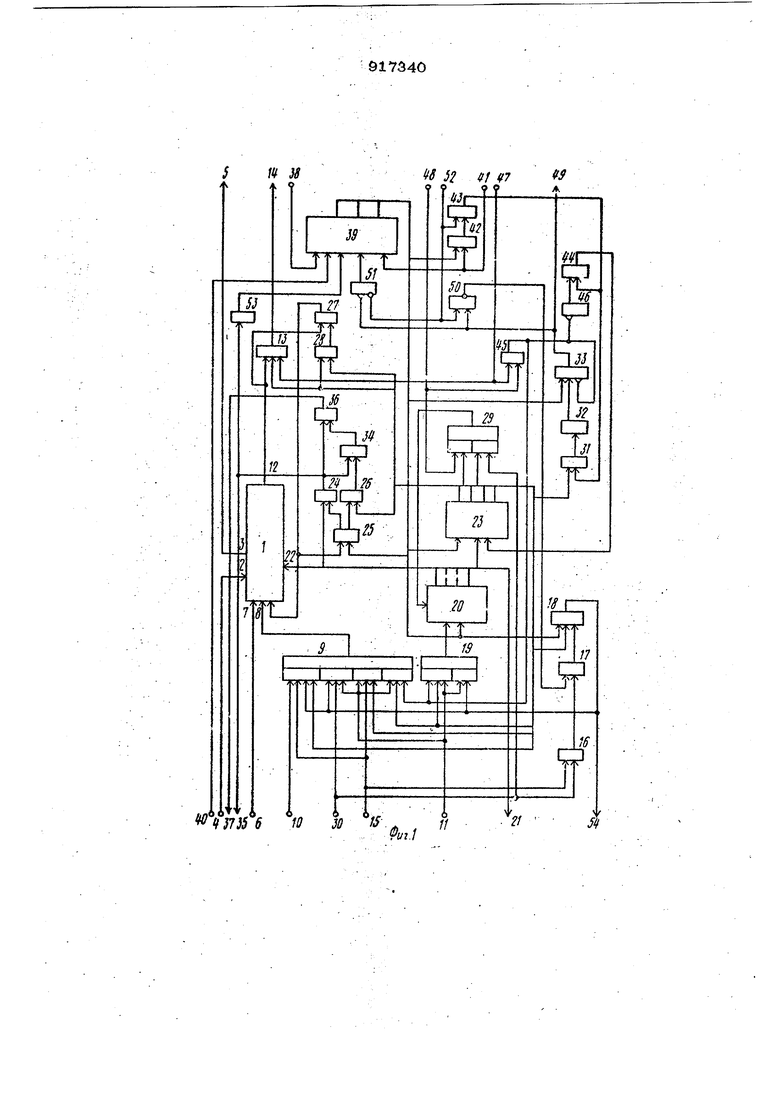

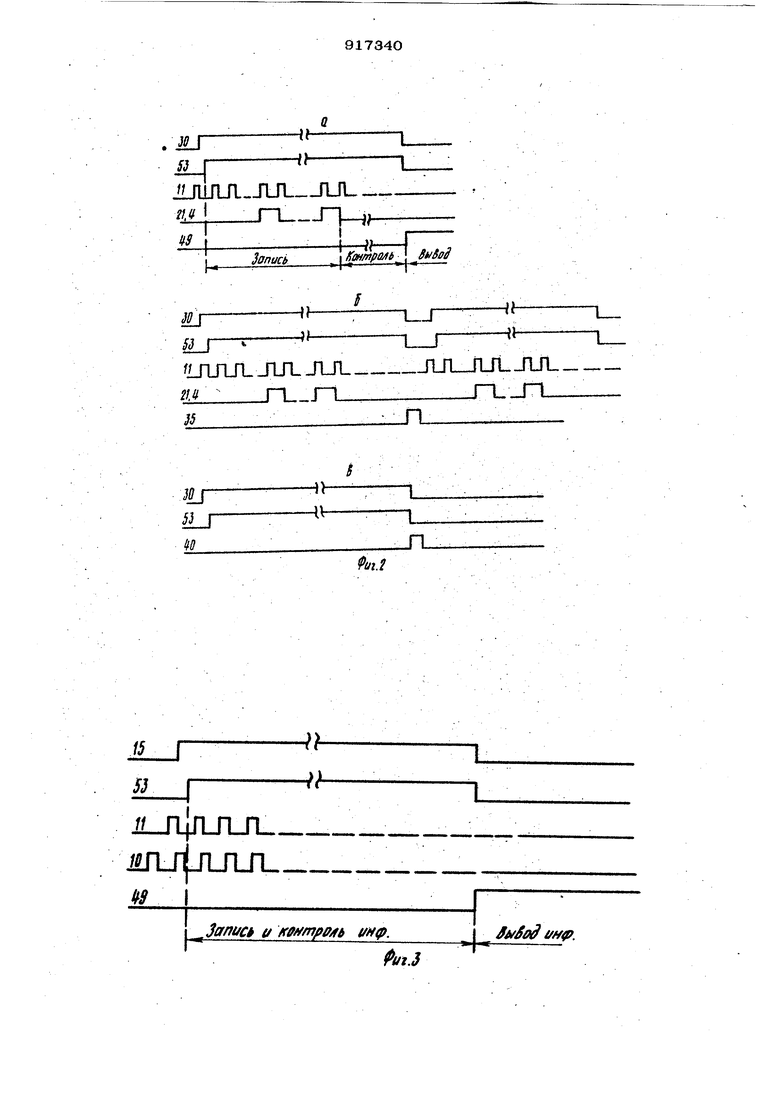

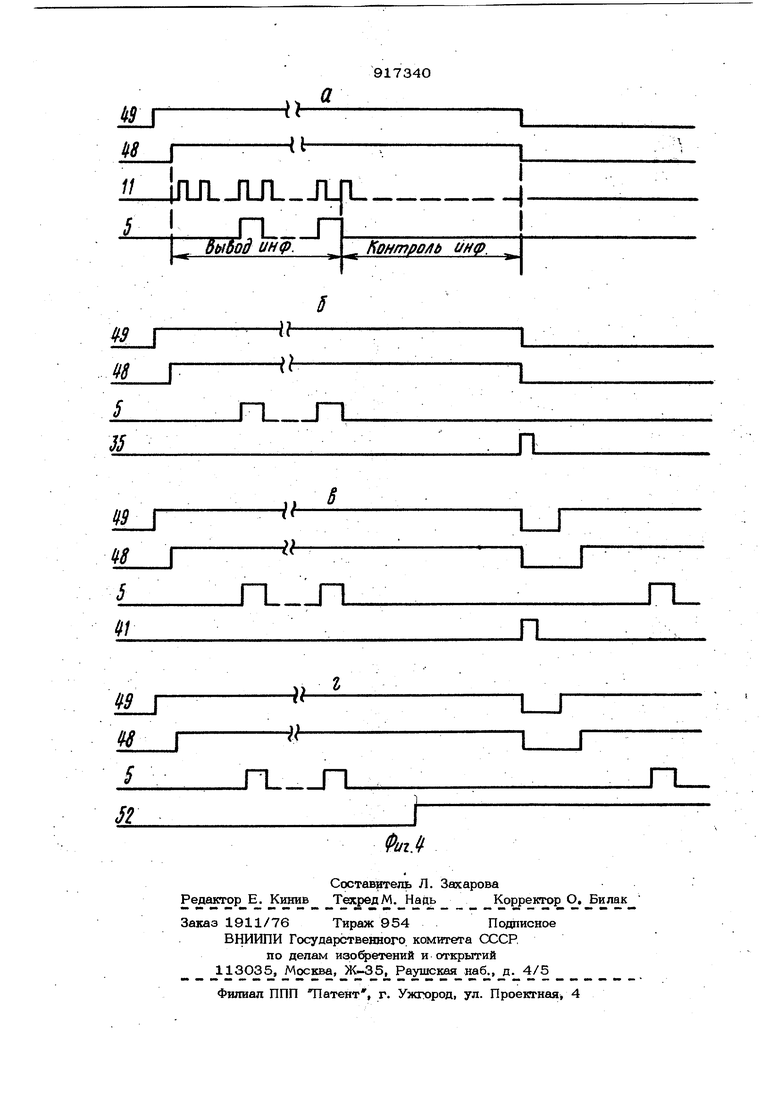

Изофетение oTfносится к и лпульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Известно yiCTpoScTBo преобразования двоичного п - разрядного кода, содержа гцее счетчик, дешифратор, входные и :В1 ходные ключи, регистр памяти и логические элементы Г13. Недостаток этого устройства - огра ниченные функционалхэные возможности. Наиболее близким к предлагаемому является преобразователь параллельнохх кода в последовательный, содержащий раэ рядный регистр сдаига, соответствующие входы и Ейыходы которого соединены с ВХОШШ1МИ и выходными шинами параллельного кода, выходной ключ, элемент 4И ИЛИ, первый, второй, третий и четвертый входы -которого соединены с соответ угвуюшими шинами синхронизации йрео азова теля, распределитель тактов, триггерял результата ; контроля, входные ключи и элементы задержки 21. Недостатком этого устройства являет ся невозможность обеспечения преофазования последовательного кода в параллельный и многократный выдачи информации, что ограничивает его область применения. Цепь изобретения - расширение функциональных возможностей преобразователя кодов . Указанная цель достигается тем, что в преобразователь, содержащий разрядный регистр сдвига, первые входы которого соединены с входными шинами параллельного кода, другой вход - с входной шиной последовательного кода, первые выходы подключены к вьрсодным шинам параллельного кода, а выход перецоса через первый выходной ключ подключен к выходной шине последовательного кода, элемент 4И-ИЛИ, выход которого соединен с первым входом синхронизации регистра сдвт1га, первый вход - с пербой шиной синхронизашга преобразователя кодов, второй, третий .четвертый входы - со второй шиной синхронизации преобразователя кодов, распределитель тактов, триггеры результата контроля, входные ключи и элементы задержки, введены распределитель операций элемент Пирса, элементы 2И-ИЛИ, элементы ИЛИ, выходные и управляющие клк чи, блок элементов ИЛИ, триггеры ввода и вывода, причем пятый и шестой входы элемента 4И-ИЛИ соединены с источником последовательного кода и через пер|вый элемент ИЛИ и первый входной ключ с первым входом триггера ввода, ыход которого подключен к седьмому и восьмому входам элемента 4И-ИЛИ, шине ввода преобразователя кодов и первому входу первого элемента 2И-ИЛИ, второй и третий входы которого соединены со второй шиной синхронизации, а выходы с первым входом распределителя тактов, первые вькоды которого соединены с адресньгми шинами преобразователя кодов и с другими входами синхронизации регистра сдвига, выход переноса распределителя тактов соединён с первым входом распределителя операции, выход старшего раэ:ряда распределителя тактов подключен ко :входу второго ВЫХОДНОГО ключа, второй вход которого соединен с выходом первого триггера результата контроля, другой его выход подключен ко входу первого управляклцего ключа, при этом счетный вход первого триггера результата контроля соединен с соответствукацим последовательным входом регистра сдвига и с выходом второго управляюшего ключа, один из входов которого соединен с выходом переноса регистра сдвига, а другой - с выходом второго элемента ИЛИ, первый вход которого соединен со вторым входом первого выходного ключа, вторым входом первого управпяюшегчз клю ча и первым выходом распределителя операций, второй его выход подключён ко второму входу второго элемента ИЛИ, третий выход распределителя операций подключен к девятому входу элемента 4И-ИЛИ и к .первому входу второго элемента 2И-ИЛИ, второй вход которого соединен с десятым входом элемента 4 ИИЛИ, с источником параллельного кода и со вторым входом первого элемента ИЛИ причем, выход второго элемента 2И-ИЛИ соединен с общей шиной распределителя тактов, четвертый выход распределителя операций подключен к одиннадцатому входу элемента 4И-ИЛИ, а третий выход распределителя операций соединен с двенадцатым входом элемента 4И-ИЛИ, чет- веотым входом первого элемента 2И-ИЛИ со вторым входом триггера ввода, с третьим входом второго элемента 2ИИЛИ и через третий управляющий ключ и церазый элемент задержки с первым вхо-г дом триггера вывода, четвертый выход распределителя операций соединен со вторым входом первого управляющего ключа, выход которого подключен к первому входу второго триггера результатов контро ля, второй вход которого подключен к выходу второго выходного ключа, к первой шине результатов контроля и к первому входу третьего выходного ключа, второй вход которого соединен с выходом второго триггера результатов контроля, а выход - со второй шиной результатов контроля преобразователя кодов, при этом установочная шина преобразователя кодов подключена к первому входу блока элементов ИЛИ, второй вход которого соединен с шиной результатов контроля источников информации преобразователя кодов, ретий вход соединен с шинрй результатов контроля приемников информации и первым входом третьего триггера результатов контроля, выход которого поцклк чен через третий элемент ИЛИ ко второму входу третьего управляюшего ключа и первому вхооу четвертого Управляюшего ключа, выхоц которого соединен с установочным входом распределителя операций, другой вход третьего триггера результатов контроля соединен с первым вькодом блока элементов ИЛИ и со вторым входом триггера вывода, кроме того выход четвертого элемента ИЛИ подключен к дифференциальному входу триггера вывода, через второй элемент задержки - ко второму входу четвёртого управляющего ключа, к тринадцатому входу элемента 4И-ИЛИ, к пятому входу первого элемента 2И-ИЛИ, первый вход четвертого элемента ИЛИ соединен с шиной ввода последовательного кода преобразователя, с третьим входом первого выходного ключа, а второй вход - с четвертй п д входом второго элемента 2И-ИЛИ и шиной ввода параллельного кода, при этом второй выход .блока элементов ИЛИ соединен с установочныКда входами распределителей операций.и тактов и с третьим входом первого тригЬера ввода, третий выход блока элементов ИЛИ соединен со вторьп г входом триггера результата контроля, причем выход триггера вывода подключен к шине выхода преофазователя, к первому входу элемента Пирса и к дифференциальному входу пятого управляклцего ключа, выход которого соединен с четвертым входом блока элементов ИЛИ, а инверсный вход пятого управляющего ключа связан с повтора преобразователя и со вторыми входами третьего элемента ИЛИ и элемента Пирса, выход последнего подключен ко второму входу первого входкого ключа, при этом пятый вход блока элемента ИЛИ через третий элемент задержки подключен к первой шине результатов контроля преобразователя. На фиг. 1 представлена функциональная схема преобразователя кодов; на фиг, 2-4 - циклограммы его работы. Преобразователь кодов содержит п разрядный регистр 1 сдвига, количество разрядов которого равно количеству разрядов кода, образованного из.К-1 значимых m-разрядных информационных бло ков и К - ого блока с контрольной инфор мацией, количество разрядов которого равно количеству значимых информационных блоков, следовательно, h (m+l) (К-1). Первые m (входов ) 2 и (ВЬЕСОДОВ) 3 регистра 1 сдвига связаны соответствен- но с входными шинами (входами) 4 и вы ходными шинами (выходами). 5 параллель ного кода преобразователя, входная шина (вход) в последовательного кода которого соединена с последовательным входом 7 регистра 1 сдвига, вход 8 синхронизации которого подключен к выходу элемен та 9 4И-ИЛИ. Первый вход элемента 9 4И-ИЛИ соединен с шиной 10 синхронизации преобразователя, второй, третий и четвертый входы элемента 9 4Й-ИЛИ со единеНы с шиной 11 синхронизации преобразователя. Выход; 12 переноса регист ра 1 сдвига через выходной ключ 13 подключен к выходной шине (выходу) 14 последовательного кода преобразователя. Шина 15 последовательного кода соединена с пятым и шестым входами элемента 9 4И-ИЛИ и через элемент 16 ИЛИ и входной ключ 17 - со входом триггера 18 ввода, выход которого подключен к седьмому и восьмому входам элемента 9 4И-ИЛ1И и ко входу элемента 19 2И-ИЛИ, второй и третий входы которого соединены с шиной 11 синхронизации преобразователя. Выход элемента 19 2И-ИЛИ связан с входом распределителя 20 .тактов, емкость которого равна п . Выходы распределителя 20 тактов соединены с адресными шинами 21 преобразователя и со входами 22 синхронизации регистра 1 сдвига, выход переноса распределителей 2О тактов соединен со входом распределителя 23 операций, старший разряд распределителя 2О тактов подключен ко вж. ду выходного ключа 24, второй вход и торого соединен с выходом триггера 25 результатов контроля, другой выход которого подключен ко входу управляющего ключа 26. Счетный вход триггера 25 результата контроля связан с другим последовательным входом регистра 1 сдвига и с выходом управлякщего ключа 27, Один из входов управляющего влюча 27 соединен с выходом 12 переноса регистра 1 сдвига, другой - через элемент 28 ИЛИ со вторым и третьим выходами распределителя 23 операций. Выход распределителя 23 операций подключен к девятому входу элемента 9 4И-ИЛИ н ко входу элемента 29 2И-ИЛИ, второй вход которого связан с десятым входом элемента 9 4И-ИЛИ , с шиной 30 параллельного кода и со вторым входом элемента 16 ИЛИ. Выход элемента 29 2И-ИЛИ соединен с общей шиной распределителя 20 тактов. Второй выход распределителя 23 one-v раций подключен к одиннадцатому входу элемента 9 4И-ИЛИ. Третий выход распределителя 23 операций связан со вторым входом выходного ключа 13, двенадцатым входом элемента 9 , четвертым входом элемента 19 2И-ИЛИ, с установочным входом триггера 18 ввода, с третьим входом элемента 29 2И-ИЛИ и через управляюший гапоч 31 и элемент 32 задержки - со входом триггера 33 вывода. Четвертый выход распределителя 23 операций соединен через второй вход управляющего ключа 26с установочным входом триггера 34 результатов контроля, счетный вход которого подключен к выходу выходного ключа 24, к шине 35 результатов контроля преобразователя и ко входу выходного 1слюча 36, второй вход которого связан с выходом триггера 34 результатов контроля, а выход - с шиной 37 результатов контроля преобра-. зователя. Установочная шина 38 преобразователя подключена ко входу блока 39 элементов ИЛИ. Второй вход блока 39 элементов ИЛИ соединен с шиной 40 результатов контроля источников информашш преобразователя. Третий вход блока 39 элементов ИЛИ соединен с шиной 41 результатов контроля приемников информации и со входом триггера 42 результатов конт роля приекшиков информации, выход рого подключен через элемент 43 ИЛИ ко второму входу управляюшего ключа 31 и ко входу улравп пощего кнюча 44, выход которого связан с установочным Е1ходом распределителя 23 операций. Дрзпгой вход триггера 42 результатов контроля приел никоБ информации соединен,с выходом бирка 39 элементов ИЛИ и с другим вхо дом триггера 33 вывода. Выход элемента 45 ИЛИ подключен к дифференциалшому входу триггера 33 вывода и через элемент 46 задержки - ко второму входу управляющего ключа 44-. Выход элемента 45 ИЛИ связан с три надцатым входом элемента 9 4И-ИЛИ, пятым входом элемента 19 2И-ИЛИ, вхо ды элемента 45 ИЛИ соединены с шина ми 47 и 48 ввода последовательного и параллельного кодов преобразователя, и, соответственно, с третьим входом выходного ключа 13 и с четвертым входом элемента 29 2И-ИЛИ. Е горой выход блока 39 элементов ИЛИ связан с установочными входами распределителей 23 и 2 О операций И тактов и с другим установочным входом триггера18 ввода. Третий выход йюка 3 9 элементов ИЛИ соединен с установочным входом счетного триггера 25 результатов контроля. Вы ход триггера 33 вывода подключен к ши не 49 выхода преобразователя, ко входу элемента 5О Пирса и к дифференциальному входу управляющего ключа 51, выход которого соединен с четвертым входом . блока 39 элементов ИЛИ. Инверсный вхб .управляющего кЛюча 51 связан с ыганой 52 повтора преобразователя и со вторыми входами элемента 43 ИДИ и элемента 50 Пирса. . Выход последнего подключен ко второму входу входного ключа 17. Пятый вхоц блока 39 элементов ИЛИ подключен чероз элемент 53 задержки к шине 3 5 результатов контроля преобразователя.Выхо триггера 18 ввода подключен к шине 54 ввода преобразователя. Преобразователь работает следующим образом. Перед началом работы проводится ус, тановка в исходное состояние всех элементов через блок 39 элементов ИЛИ сигналом общий сброс приходшним на установочную шину 38. В исходном состоянии на первом выходе распределителя 23 операций проявляется сигнал. . Данный преобразователь может принимать информацию из источников с последовательным или параллельным кодом, контролировать ее и передавать в приемники с последовательным или параллельным кодами. Рассмотрим работу преофазователя при вводе информации из источника параллельного кода. При поступлении с шины 30 сигнал вьюода источника параллельного кода, в смтучае, если преофазователь не проводит работу с приемниками информашга (отсутствует сигнал вывод на шине 3 49 и через элемент 50 Пирса иа входной ключ 17 поступает разрешающий сигнал), вводится триггер 18 ввода, и в источник подается сигнал ввод через шину 54. Циклограмма работы преобразователя при приеме информации из шины 30 параллельного кода представлена на фиг. 2. Синхроимпульсы, приходящие с шины 11, через элементы 19 2И-ИЛИ поступают на распределитель 2О тактов. ОдновреAteHHo эти же импульсы через элемент 9 4Й-ИЛИ поступают на вход 8 синхронизации регистра 1 сдвига. На общую шину распределителя 2О тактов поступает разрешакяиий сигнал через элемент 29 2И-ИЛИ, так как в исходном состоянии этот элемент приоткрыт разрешающим потенциалом с первого выхода распределителя 23 операций. С У выходов распределителя 2О тактов импульсы Адресов информационных бяоков поступают в источник информации через шину 21 и одновременно на параллельные входы 22 синхронизации регистра 1 сдвига. Из источника информации соответственно каждому адресу в преофазователь поступает информационный m - разрядный блок через шину 4 на первые гп входов 2 регистра 1 сдвига. По совпадению адреса информационного блока с т-ым импульсом сдвига . происходит запись этого информационного блока в регистр 1 сдвига. , До прихода следующего информационного потока из источника информации в регистр 1 происходит сдвиг записанной информации на m разрядов. : После записи последнего информационного потока происходит контроль запианной информации. При этом по заднему фрошу последней п-юго синхроимпульса состояние распределителя 23 операций изменяется, и появля ется сигнал на следующем выходе распределителя 23, снимается разрешакящй сигнал с ойцей шины распределителя 2 О, и приоткрьюается управляющий ключ 27 через элемент 28 ИЛИ, Импульсы при сдвиге с выхода 12 регистра 1 сдвига через ключ 27 поступаю на другой вход синхронизации этого же регистра 1. Выходные импульсы с регистра 1 сдвига одновременно поступаюти на счетный вход триггера 25 результатов контроля. Если при поступлении К-го адреса инI формационного биока с выхода распределителя 2О на вход ключа 24 на выходе этого ключа нет сигнала, то это cooTBeivствует отсутствию искажений информации. Источник информации снимает сигнал вывода с шины 30. Операция контроля на этом заканчивается и появляется сигнал на следующем выходе распределителя 23. Через управляющий ключ 31 с задержкой на элементе 32 задрежки взводится тригг ер 33 вывода, и на выход преофазователя поступает сигнал выход через ши- ну 49 (фиг. 2а). Если по результатам контроля информации на выходе ключа 24 появится сигнал об искажении (фиг. 26), то через элемент S3 задержки и блок 39 элементов ИЛИ обнуляются все элементы памяти, кроме триггера 34 результатов ков гроля, который взводится по заднему фронту сигнала с ключа 24 . В источник поступает сигнал через шину 35, свидетепь Ьтвующий об искажении информации. По получении этого сигнала источник информации снимает сигнал вывод из. источника параллельного кода и с задержкой вновь его выдает. Процесс записи информации и контроля повторяется аналогично выше описанному. В случае повторного получения сигнагла об искажении информации в источник поступает сигнал аварийного ее искажения через триггер 34 результатов контроля, выходной ключ 36 и шину 37. При этом данный преобразователь устанавливается в исходное состояние через блок 39 элементов ИЛИ. ;Если при записи информации в преобразователь из источника информации через шину 40 поступает сиг нал искажения информации, то через блок элементов ИЛИ преофазователь устанавливается в исходное состояние, а сигнал вывод из источника параллельного кода вновь не поступает (фиг. 2в). При вводе информации из источника последовательного кода преобразователь работает следующим образом. При поступлении на шину 15 сигнала вывод из источника последовательного кода, в случае, если преобразователь не работает по выводу инфзрмашш, взволит ся триггер 18 ввода, и в источник подается сигнал ввод через шину 54, аналогично вьпцеописанному. Циклограмма работы преобразователя при приеме информации из источника последовательного кода представлена на фиг. 3. По получении источника информации сигаала ввод источник начинает выдавать в преофазователь информадгоо в последовательном коде через входную пш- ну 6 на вход 7 регистра 1 сдвига. Синхроимпульсы, проход5шше на нпшу 10 синхронизации, через элемент 9 4И- ИЛИ поступают на последовательны вход 8синхронизации регистра 1 сдвига. По заднему фронту входного информационного импульса происходит запись информации в регистр 1, а при поступлении одного импульса синхронизации на вход 8 происходит сдвиг записанной информации на один разряд. Одновременно синхроимпул1#:ы, приходящие с шины 10, поступают на распределитель 2 О тактов. Импульс переноса с распределителя 20 тактов, соответствующий п -ому входному импульсу синхронизации, поступает на распределитель 23 операций, и появляется сигнал на другом выходе этого распределителя. Этим сигналом открывается элемент 9 4И-ИЛИ и через элемент 28 ИЛИ - управляющий ключ 27. Начинается второй этап - контроль записанной информации, который проводится аналогично вышеописанному. При выводе информации в приемник параллельного кода преобразователь работает следующим образом. Вывод информации из преоЬразовагеля в приемник начинается только после Появления на шине 49 сигнала вьтод. При этом открыт слео ющий выход распределителя 23 операций. По сигналу вывод приемник, если он свободен, формирует ответный сигнал ввод. Сигнал ввод из приемника параллельного кода, приходящий на шину 48, через элемент 45 ИЛИ открывает элемент 9 4И-ИЛИ и элемент 19 2И-ИЛИ, а через элемент 29 2И-ИЛИ подает разрешающий сигнал на общую шину распределителя 2О тактов. Импульсы синхронизации поступают с шины 11 через элемент 9 4И-ИЛИ и элемент 2И-ИЛИ на распределитель 20 тактов и на регистр 1 сдвига и сдвигают информашао, которая контролируется аналогично вышеописанному. Адреса информатионных блоков с вы- JcoHpB распределителя 20, поступающие в приемник через шину 21, разрешают считывать поочередно m разрядные инфорз мационные массивы с первых выходов 3 регистра 1 сдвига через шину 5 в прием ник (фиг. 4а). По окончании вьюачи последнего адреса информационного блока срабатывает распределитель 23 операций, оканчивается сигнал с указанного выхода распределителя 23, и появляется {сигнал со следующего выхода. При этом закрываются элементы 9 4И-ИЛИ и 19 2И-ИЛИ и управляющий ключ 27. Сдвиг информации в регистре 1 сдвига И ра- . бота распределителя 2 О прекращаются. Приемник получив информацию, начинает ее контролировать, и по окончанию контроля снимает сигнал ввод из прием ника параллельного кода с щины 48. По окончании этого сигнала через эле мент 45 ИЛИ сбрасывается триггер 33 вывода, и сигнал вывод с шины 49 снимается. Если приемник не контролирует принятую информацию, то вне зависимости от качества принятой информации он должен прекратить выдачу сигнала ввод. При этом операция вывода информации в приемник оканчивается. Если в процессе контроля при выводе информации в данном преобразователе по является сигнал искажения информации, то данный преобразователь устанавливается в исходное состояние, т.е. сбрасываются все логические элементы и регистр (физр. 46). Триггер 34 результатов контроля сбрасывается через управ ляющий ключ 26 после сброса триггера 25. Сигнал искажения информации поступает в приемник через шину 35, и.прием ник устанавливается в первоначальное ис ходное состояние. Повторной выдачи информацтта в приемник не происходит. Если при. приеме информации из ника появился сигнал искажения информации, а при повторном приеме искажени информации не произойдет, то триггер 2 остается взведенным. И при передаче искаженной информации в приемник на шине 37 появится сигнал аварийного искажени информации. Если по окончании контроля принятой информации в приемнике появится сигнал об искажении информации, то атим сигналом приемник устанавливается в исходнов состояние. По окончании сигаала ввод из приемника параллельного кода снимается сигнал вывод., Приходящий на шину 41 сигнал искажения информации взводит триггер 42 результата контроля приемников информации, и через элементы 43 и 31 и элемент 32 задержки снова ваводится триггер 33 вывода, и на выходной шине 49 появляется сигнал вывод. При этом распределитель 23 операций через элемент 46 задержки и управля наций ключ 44 устанавливаются в состояние соответствующее операции вывод. Операция вывод информации в приемник параллельного кода повторится (фиг. 4в). В случае, если требуется дважды или более раз вьшести одну и ту же инс1юрмацию из преобразователя в один или несколько приемников, то на шину 52 должен бьпъ подан cviraaif. повтор до момента окончания сигнала ввод из приемника параллельного коДа. Этот сигнал через элемент 43 ИЛИ держит триггер 33 вывода во взведенном состоянии через управляющий ключ 31 во время вывода информации. По окончании вывода, т.е. после снятия приемником сигнала ввод из приемника параллельного кода с шинь. 48, триггер 33 вывода будет обнулен. Распределитель 23 операций установится по окончании сигнала ввод из приемника в состояние, соответствующее этапу вывода информации. Операция вывода информации в приемник повторится. Если сигнал повтор снимается с шины 52 раньше окончания сигнала вывод то последующей выдачи . информации в приемник не €удет (фиг.4г). И преобразователь через ключ 51 и блок 39 элементов ИЛИ установится в исходное состояние. Рассмотрим работу преобразователя при выводе информации в приемник последовательного кода. Вывод информа.шш в npHeivfflHK последовательного кода начинается с момента поступления из приемника на шину 47 сигнала ввод из приемника последовательного кода. По этому сигна; открываются элеменгы 9 4И-ИЛИ и 19 2И-ИЛИ. и выходной Ключ 13. Импульсы синхронизации с шины 11 поступают на распределитель 20 тактов и на регистр I сдвига. Информация, записанная в регистр 1, поступает через выходной ключ 13 и последовательный выход 14 преофазователя в приемник. Одновременно эта информация контролиру ется. По окончании п -ого синхроимпульса срабатьгеает распределитель 23 операций и появляется сигнал на соответствующем выходе этого распределителя, при этом закрьшаются элементы 9 4И-ИЛИ и 19 2И-ИЛИ и выходной ключ 13. В случае положительного регультата контроля информации в приемнике последний снимает сигнал ввода из приемника последовательного к;ода, а по его окончании снимается сигнал вывод из преобразователя с триггером 33 вывода. Пре образователь устанавливается в исходное состояние. На этом операция вьюода информации в приемник последовательного кода пр6 кращается. . В случае поступления сигналов повтор или сигнала искажения информации из при емника или получения своего искажения информации преобразопагель будет работать анало ично случаю передачи инфор-маций в приемник параллельного кода в части процессов управления. Таким офазом, предлагаемый преоб. разоватбль проводит работу с системаШ с последовательным и параллельным пред ставлением информации. Он -может быть использован и в качестве буферного уст poitoTBa и при приеме и передаче информа ции. Предлагаемый преобразователь может контролировать принятую информацию передавать одну и ту же информацию в приемник несколько раз, при этом контро лируя ее. Все вышеуказанное расшкрйет функциональные возможности предлагаемо го преобразователя и позволяет испойьзовать его во многих дискретных системах с двоичным представлением информации. фо рмула изобретения Преобразователь кодов, содержащий разрядный регистр сдвига, первые входы которого соединены с входными шинами параллетшного кода, другой вход - с вход ной шиной последовательного кода, первые выходы подключены к выходным шинам параллельного кода, а выход переноса через первый выходной ключ подключе к выходной шине последовательного кода элемент 4И-ИЛИ, выход которого соединен с первым входом синхронизации ре гистра сдвига, первый вход - с первой шиной синхронизации преобрааовагеля кодов, второй, третий и четверппьгй входы с второй шиной синхронизации преобразователя кодов, распределитель тактоаа, три геры результата контроля, В содные ключи. и элементы задержки, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены распределитель операций, элементы 2И-ИЛИ, элемент Пирса, элементы ИЛИ, выходные и управляклдие ключи, триггеры ввода и вьюода и биок элементов ИЛИ, пятый и шестой входы элемента 4И-ИЛИ соединены с источником последователшого кода и через первый элемент ИЛИ и первый входной .ключ с первым входом триггера ввода, выход которого подключен к седьмому и восьмому входам элемента 4И-ИЛИ, шине ввода преобразователя кодов и первому входу первого элемента 2И-ИЛИ, второй и третий входы которого соединены с второй шиной синхронизации, а выход,- с первым входом распределителя тактов, первые выходы которого соединены-с адресными шинами преобразователя кодов и с другими входами, синхронизации регистра сдвига, выход переноса распределителя тактов соединен с первым входом распределт-ггеля операций, выход старшего разряда распределителя тактов подключен к входу второго выходного ключа, второй вход которого соединен с выходом первого триггера результатов контроля, другой его выход подключен к входу первого управляющего ключа, при этом счетный вход первого триггера результата контроля соединен с соответствующим последовательным входом регистра сдвига и с выкоаом второго управляющего ключа, один из Входов «Которого соединен с выходом переноса регистра сдвига, а другой с выходом второго элемента ИЛИ, первый вход которого соединен с вторым входом первого выходного ключа, вторым входом первого управляющего ключа и первым выходом распределителя операций, второй его выход подключен к второму входу второго элемента ИЛИ, третий выход распределителя операций подключен к девятому входу элемента 4И-ИЛИ и к первому входу второго элемента 2 И-И ЛИ, второй вход которого соединен с десятым входом элемента 4И-ИЛИ, с источником параллельного кода и с вторым входом первого элемента ИЛИ, причем выход второго элемента 2 И-И Л И соединен с общей шиной распределителя тактов, четвертый выход распределителя операций подключен к

одиннадцатому входу элемента 4И-ИЛЙ, а третий выход распределителя операций.j соединен с двенадцатым входом элемента 4И-ИЛИ, четвертым входом первого элемента 2И-ИЛИ, с вторым входом тригг ра ввода, с; третьим Входом второго элемента 2 И-ИЛИ и через третий управляющий ключ и первый элемент задержки с первым входом тригзгёра вывода, четвертый выход распределителя операций соединен с 1вторым входом первого управляющего ключа, выход которого подключен к первому входу второго триггера результатов контроля, второй вход которого подключен к выходу второго выходного ключа, к первой шине результатов кош роля и к первому входу третьего выходного ключа, второй вход которого соеди нен с выходом второго триггера результатов контроля, а выход - с второй шиной результатов контроля преофазователя кодов, при этом установочная шина преобразователя кодов подключена к первому 1Ёа:оду блока элементов ИЛИ, второй вход которого соединен с шиной результатов . контроля источников информации преобразователя кодов, третий вход соединен с шиной результатов контроля приемников .информации и с первым входом третьего триггера результатов контроля, выход которого подключен через третий элемент . ИЛИ к второму входу третьего управляющего ключа и к первому входу четвертого управлякщего ключа, выход которого соединен с установочным входом распределителя операций, другой вход третьего триггера результатов контроля соединен с первым выходом блока элементов ИЛИ и с вторым входом триггера вывода, кроме того, выход четвертого элемента ИЛИ подключен к дифференциальному вкоду-триггера вывода, через второй элемент задержки - к втброму входу четвертого управлякщехчз ключа, к тринадцатому входу элемента 4И-ИЛИ, к пятому входу первого элемента 2И-ИЛИ, первый еход четвертого элемента ИЛИ соединен с шиной ввода последовательного кода преофазователя с третьим входом первого выходного ключа, а второй вход с четвертым входом второго элемента 2И ИЛИ и шиной ввода параллельного кода, при этом второй выход блока элементов ИЛИ соединен с установочными входами распределителей операции и тактов и с третьим входом первого триггера ввода, третий выход блока элеме1ггов ИЛИ соединен с вторым входом первого триггера результата контроля, причем выход триггера вывода подключен к шине выхода преобразователя, к первому вхоцу элемен та Пирса и к дифференциальному входу пятого управляющего ключа, выход которого соединен с четвертым входом блока элемента ИЛИ, а инверсный вход пятого управляюшего ключа связан с шиной повтора преобразователя и с вторыми выходами третьего элемента ИЛИ и элемента Пирса, выход последнего подключен к второму. входу первого входного ключа, при этом пятый вход блока элементов ИЛИ через третий элемент задержки подключен к первой шине результатов контроля преобразователя.

Источники информации, принятые во внимание при экспертизе

f5 Г-

л I т.

у/ п{п п п.

jШJiJ JlJL....

Запис е ffffffmpMb ун.

t/fi.

3S

in

n

n

n

n

Авторы

Даты

1982-03-30—Публикация

1980-02-15—Подача