(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля частоты | 1980 |

|

SU917113A1 |

| Устройство для контроля качества канала связи | 1984 |

|

SU1197099A1 |

| Корреляционный дискриминатор времени транспортного запаздывания | 1983 |

|

SU1107130A1 |

| Устройство контроля частоты вращения | 1985 |

|

SU1303941A1 |

| Устройство для выявления сердечной аритмии | 1980 |

|

SU849581A1 |

| Устройство для контроля качества канала связи | 1980 |

|

SU1035810A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

I

. . Изобретение относится к импульсJ ной технике и может быть использова но в тахометр11ческих приборах для контроля частоты.,

Известно устройство для контроля частоты, содержащее генератор импульсов, счетчик, элементы совпадения, управляющие триггеры, дешифраторы и входной формирователь, связанный своим выходом со входом сброса счетчика, счетный вход которого соединен с выходом генератора импульсов, а выходы - со входами дешифраторов, подключенных своими выходами .к управляющим входам рабочих триггеров управления, выходы которых соединены с одними входами элементов совпадения, вторые входы которых подключены к выходу формирователя, а выходы - к управляющим входам выходных триггеров управления 1.

Недостаток данного устройства .низкая технологичность, отсутствие

унификации его схемы и низкая помехоустойчивость.

Наиболее близким к предлагаемому изобретению является устройство для контроля частоты, включающее формирователь импульсов, выход которого соединен с первыми входами регистра, триггера и первого счетчика, выходы которого подключены ко вторым входам регистра, а также генератор импуль10сов и последовательно соединенные управляемый генератор и второй счетчик, выход которого соединен со вторым входом tpиггepa 2 .

Недостатком этого устройства яв15ляются ограниченные функциональные возможности, так как оно обеспечивает только двухпороговый контроль частоты.

Цель изобретения - расширение

20 функциональных возможностей устройства.

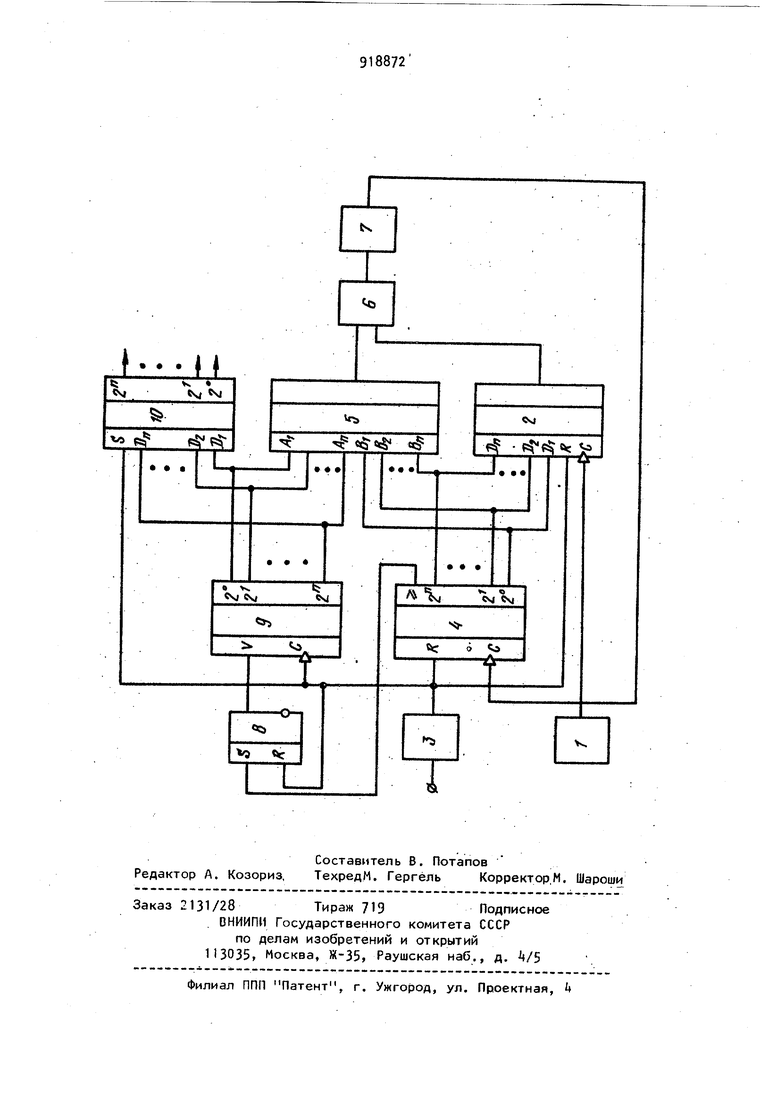

Эта цель достигается тем, что в устройство для контроля частоты. содержащее формирователь импульсов, выход которого соединен с первыми входами регистра, триггера и первог счетчика, выходы которого подключены к вторым входам регистра, а такж генератор импульсов и последователь но соединенные управляемый генератор и второй счетчик, выход которого соединен с вторым входом триггера, введены блок памяти, делитель и эле мент равнозначности, выход которого соединен со входом управляемого .гене ратора, а входы подключены к выходам блока памяти и делителя, первый вход которого соединен с выходом генераjropa импульсов, а второй вход подключен к выходу формирователя импульсо и второму входу второго счетчика , вторы выходы которого соединены с третьими выходами делителя и первыми входами бл ка памяти, вторые входы которого под ключены к выходам первого счетчика, второй вход которого соединен с выходом триггера. На чертеже представлена структурная схема устройства для контроля частоты. Устройство содержит генератор °1 импульсов,делит ль 2, формирователь 3 импульсов, счетчике, блок 5 памяти, элемент 6 равнозначности,управ ляемый генератор 7, триггер 8, счетчик 9 и регистр 10, Разрядность п суммирующего счетчи ка равна разрядности контрольной уставки. Управляемый делитель 2 авто матически выбирают коэффициент деления, в зависимости от управляющего кода, в диапазоне от 2 до 2, Разрядность k реверсивного сметчика 9 выбирается в соответствии с количеством контрольных уставок. Уставки контрольных значений хранятся в блоке 5 памяти и записаны последовательно в возрастающем порядке, причем меньшему адресу уставки соответствует меньшее значение уставки. Частота импульсов управляемого генератора 7 намного больше образцовой частоты генератора 1 импульсов. Работа устройства для контроля часТоть основана на циклическом измерении периода исследуемой частоты и отработке уставок следящим методом, в соответствии с которым результат каждого цикла измерения срав нивается с одним из контрольных знамений уставки, и, если результат измерения больше данного контрольного значения, то для последующего цикла контроля выбирают ближайшее контрольное значение, а в противном случае - ближайшее меньшее значение. Отработка понижения или повышения значения контрольной уставки осуществляется с шагом в период контролируемой частоты. Процесс получения результата измерения периода контролируемой частоты и сравнение его с контрольным значением осуществляется поразрядно, начиная со. старшего разряда. Устройство работает следующим образом. Формирователь 3 формирует короткие ймгульсы с интервалом следования , равным периоду исследуемой частоты. Предположим, что е предыдущем цикле контроля использовалась i-я конт- рольная уставка, а также, что период контролируемой частоты оказался больше этой контрольной уставки. Следовательно, для последующего цикла контроля необходимо выбрать ближайшее большее значение контрольной уставки. Таким образом, в начале следующего контроля импульс с выхода формурователя 3 увеличивает на единицу содержимое счетчика 9, одновременно, переписывая его в регистр 10, сбрасывает в нулевое состояние суммирующий счетчик , управляемый делитель 2 и триггер 8. Увеличенным значением счетчика 9 управляющего первой группой адресных входов блока 5 памяти, из последнего вь(бирается (.г+1)-я контрольная уставка. Нулевым кодом счетчика., управляющего второй группой адресных входо блока 5 памяти и коэффициентом деления управляемого делителя 2, выбирается из блока 5 памяти значение п-го разряда (1+1)-й контрольной уставки, а делителю 2 устанавливается коэффициент деления, равный 2 . Элемент 6 равнозначности осуществляет сравнение п-го разряда с выходным значением сигнала делителя 2, на вход которого поступают импульсы генератора 1 . При появлении сигнала на выходе делителя 2 срабатывает элемент 6 равнозначности и растормаживает управляемый генератор 7 выходным импульсом которого увеличивается на единицу содержимое счетчика f. Новым значением счетчика Ц, поданным на вторую группу адресных входов блока 5 памяти, из него извлекается (п-1)-й разряд контрольной уставки, а также устанавливается управляемому делителю 2 коэффициент деления, равным Z. , и продолжапт осуществляться аналогичный процесс сравнения (п-1)го разряда с выходным значением сигнала управляемого делителя 2. Если значение периода контролируемой частоты больше значения этой контрольной уставки, то сравнение произойдет со всеми разрядами контрольной уставки и появится импульс переполнения счетчика k, который установит триггер 8, управляющий выбором режима счета реверсивного счетчика 9 в единичное состояние. Высоким потенциалом триггер 8 установит реверсивному счетчику 9 режим суммирования. Поэтому импульсом с выхода.формирователя 3, начинающим следующий новый цикл контроля,увеличится на единицу содержимое ревер сивного счетчика 9. Этим значением ИЗ блока 5 памяти извлекается (1+2)контрольная уставка и происходит аналогичный процесс сравнения. Если значение периода контролируемой чистоты меньше контрольной уставки, то сравнение по всем разрядам не произойдет, и, следовательно, импульса переполнения суммирующего счетчика не будет, g триггер 8 останется в нулевом состоянии, обеспечивая реверсивному счетчику 3 импульсов режим вычитания. Поэтому выходным импульсом формирователя 1, начи;иающим новый цикл контроля, содержимое реверсивного счетчика 9 импульсов уменьшится на единицу и выберет из блока 5 памяти контрольную уставку (ближайшую меньшую), с кото926 рой будет производиться описанный процесс сравнения. Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями, так как обеспечивает многопороговый контроль частоты., Формула изобретения Устройство для контроля частоты, содержащее формирователь импульсов, выход которого соединен с первыми входами регистра, триггера и первого счетчика, выходы которого подключены к вторым входам регистра, а также генератор импульсов и последовательно соединенные управляемый генератор и второй счетчик, выхЬд которого соединен с вторым входом триггера, о т л и ч а ю 14 е е с я тем, что, с целью расширения функциональных возможностей, в него введены блок памяти, делитель и элемент равнозначности, выход которого соединен с входом управляемого генератора, а входы подключены к выходам блока памяти и делителя, первый вход которого соединен с выходом генератора импульсов, а второй вход подключен к выходу формирователя-импульсов и второму входу второго счетчика, вторые выходы которого соединены с третьими входами делителя и первыми входами блока памяти,вторые входы которого подключены к выходам первого счетчика, второй вход которого соединен с выходом триггера. Источники информации, принятые во внимание при экспертизе 1.Патент США N 3537001, кл. С 01 R 23/00, 1970. 2.Авторское свидетельство СССР , кл. G О F 10/0, 1976.

I -И

f|

к «ч/ «41

fe Ǥ v sj pSfP CMf

Авторы

Даты

1982-04-07—Публикация

1980-05-05—Подача