(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля частоты | 1980 |

|

SU918872A1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1992 |

|

RU2027245C1 |

| ПРОГРАММНЫЙ ТАЙМЕР | 2001 |

|

RU2215367C2 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для регистрации сейсмической информации | 1990 |

|

SU1811615A3 |

| Система управления технологическими процессами | 1982 |

|

SU1104561A2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

Изобретение относится к импульсной технике и может быть использовано в тахометрических приборах для контроля частоты.

Известно устройство для контроля частоты, содержащее генератор им-, пульсов, счетчик, элементы совпадения, управляющие триггеры, дешифраторы и входной формирователь, связанный своим выходом со входом сброса счетчика импульсов, счетный вход . которого соединен с выходом генератора импульсов, а выходы - со входами дешифраторов, подключенных своими выходакш к управляющим входам рабочих триггеров управления, выходы которых соединены с одними входами элементов совпадения, вторые входы которых подключены к выходу формирователя, а выходы - к управляющим входам выходных триггеров управления lj .

Недостатки данного устройства для контроля частоты - ниэкая технологичность устройства и отсутствие унификации его схекы.

Наиболее близким к предлагаемому является устройство для контроля частоты, включающее формирователь импульсов,,выход которого соединен с первыми входами элемента ИЛИ,

триггера и регистра, вторые входы которого подключены к выходам первого счетчика, а также генератор импульсов и второй счетчик, выход которого соединен со вторыми входс1ми элемента ИЛИ и триггера 2.

Недоста1тками известного устройства являются ограниченные функциональные возможности, так как устрой10ство обеспечивает только двухпороговый контроль частоты.

Цель изобретения - расширение функциональных возможностей устрой.ства.

15

Поставленная цель достигается тем, что в устройство для контроля частоты, содержащее формирователь импульсов, выход которого соединен с первыми входами элемента ИЛИ,триг20гера и регистра, вторые входы которого подключены к выходам первого счетчика, а также генератор импульсов и второй счетчик, выход которого соединен со вторыми входами элемента ИЛИ и триггера, введены блок па- . мяти и делитель, первый н второй входы которого соединены с выходами соответственно генератора импульсов и формирователя импульсов, и выход 30 делителя подключен к первому входу

второго .счетчика, второй и третьи Ьходы которого соединены соответственно с выходом элемента ИЛИ и вы.ходами блока памяти, первые входы которого подключены к выходам первого счетчика, один из входов которого соединен с выходом формирователя импульсов, а другой подключен к выходу триггера, третьему входу делителя и второму входу блока памяти.

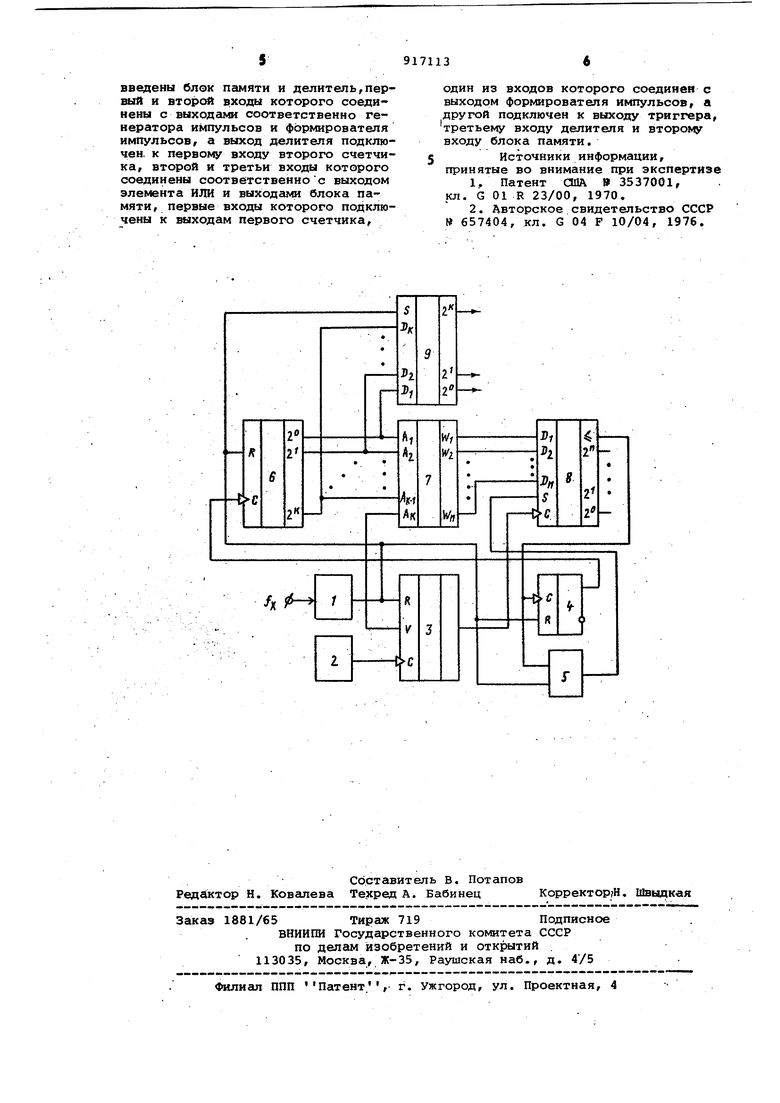

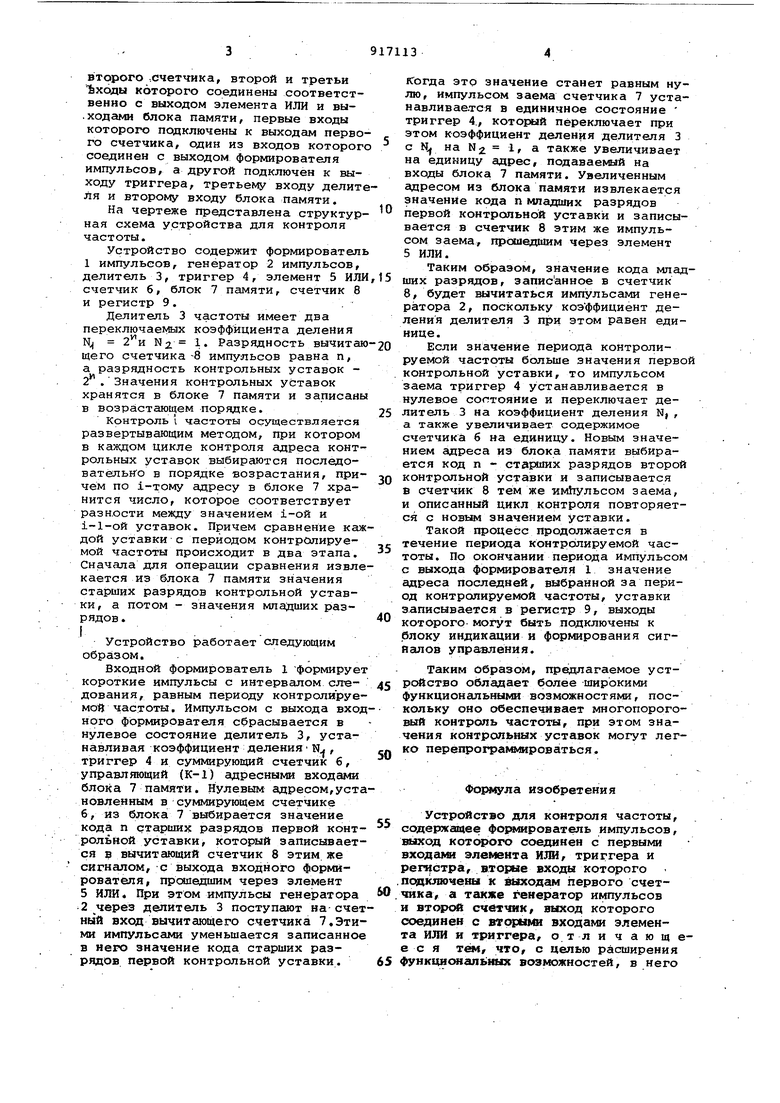

На чертеже представлена структурная схема устройства для контроля частоты.

Устройство содержит формирователь

1импульсов, генератор 2 импульсов, делитель 3, триггер 4, элемент 5 ИЛИ счетчик б, блок 7 памяти, счетчик 8

и регистр 9.

Делитель 3 частоты имеет два переключаемых коэффициента деления N N2 1. Разрядность вычитаю wero счетчика-8 импульсов равна п, а разрядность контрольных уставок 2 . Значения контрольных уставок хранятся в блоке 7 памяти и записаны в возрастающем порядке.

Контроль I частоты осуществляется развертывающим методом, при котором в каждом цикле контроля адреса контрольных уставок выбираются последоватёльно в порядке возрастания, причем по i-тому адресу в блоке 7 хранится число, которое соответствует разности между значением i-ой и i-1-ой уставок. Причем сравнение каждой уставки с периодом контролируемой частоты происходит в два этапа. Сначала для операции сравнения извлекается из блока 7 памяти значения старших разрядов контрольной уставки, а потом - значения младших разрядов.

Устройство работает следующим образом.

Входной формирователь 1 формирует короткие импульсы с интервалом еледования, равным периоду контролируемой частоты. Импульсом с выхода вход ного формирователя сбрасывается в нулевое состояние делитель 3, устанавливая коэффициент деленияN f триггер 4 и суммирующий счетчик 6, управляющий (К-1) адресными входами блока 7 памяти. Нулевым адресом,установленным в суммирующем счетчике б, из блока 7 выбирается значение кода п (зтарших разрядов первой контрольйой уставки, который записывается в вычитающий счетчик 8 этим, же сигналом/ с выхода входного формирователя, прсядедшим через элемент 5 ИЛИ. При этом импульсы генератора

2через делитель 3 поступают на счетный вход вычитающего счетчика 7,Этими импульссц и уменьшается записанное в него значение кода старших разрядов первой контрольной уставки.

Когда это значение станет равным нулю, импульсом заема счетчика 7 устанавливается в единичное состояние триггер 4, который переключает при этом коэффициент деления делителя 3 с Hf на N If а также увеличивает на единицу адрес, подаваемый на входы блока 7 памяти. Увеличенным адресом из блока памяти извлекается значение кода п младших разрядов первой контрольной уставки и записывается в счетчик 8 этим же импульсом заема, прешедшим через элемент 5 ИЛИ.

Таким образом, значение кода младших разрядов, записанное в счетчик 8, будет вычитаться импульсами генератора 2, поскольку коэффициент деления делителя 3 при этом равен единице.

Если значение периода контролируемой частоты больше значения перво контрольной уставки, то импульсом заема триггер 4 устанавливается в нулевое состояние и переключает делитель 3 на коэффициент деления Nj, а также увеличивает содержимое счетчика б на единицу. Новым значением адреса из блока памяти выбирается код п - старних разрядов второй контрольной уставки и записывается в счетчик 8 тем же имЬульсом заема, и описанный цикл контроля повторяется с новым значением уставки.

Такой процесс продолжается в течение периода контролируемой частоты. По окончании периода импульсом с выхода формирователя 1 значение адреса последней, выбранной за период контролируемой частоты, уставки з.аписывается в регистр 9, выходы которого могут быть подключены к блоку индикации и формирования сигяалов управления.

Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями, поскольку оно обеспечивает многопороговый контроль частоты, при этом значения контрольных уставок могут легко перепрограммироваться.

Формула изобретения

Устройство для контроля частоты, содержащее фО ;я14ирователь импульсов, выход соединен с первыми входааля элемента ИЛИ/ триггера и penfcTpa/ вторые входы которого .подключены к выходам первого счетчика/ а также генератор импульсов и второй счетчик/ выход которого соединен с вторыми входами элемента ИЛИ и триггера/ отличающеся T&t, что/ с целью расширения функциональных возможностей, в него

введены блок памяти и делитель,первый и второй в.ходы которого соединены с выходс1ми соответственно генератора импульсов и формирователя импульсов, а выход делителя подключен, к первому входу второго счетчика, второй и третьи входы которого соединены соответственно с выходом элемента ИЛИ и выходагда блока памяти , первые входы которого подключены к выходам первого счетчика.

один из входов которого соединен с выходом формирователя импульсов, а другой подключен к выходу триггера, третьему входу делителя и второму входу блока памяти.

Источники информации, принятые во внимание при экспертизе

1,Патент США 3537001, кл. G 01 R 23/00, 1970.

Авторы

Даты

1982-03-30—Публикация

1980-05-05—Подача