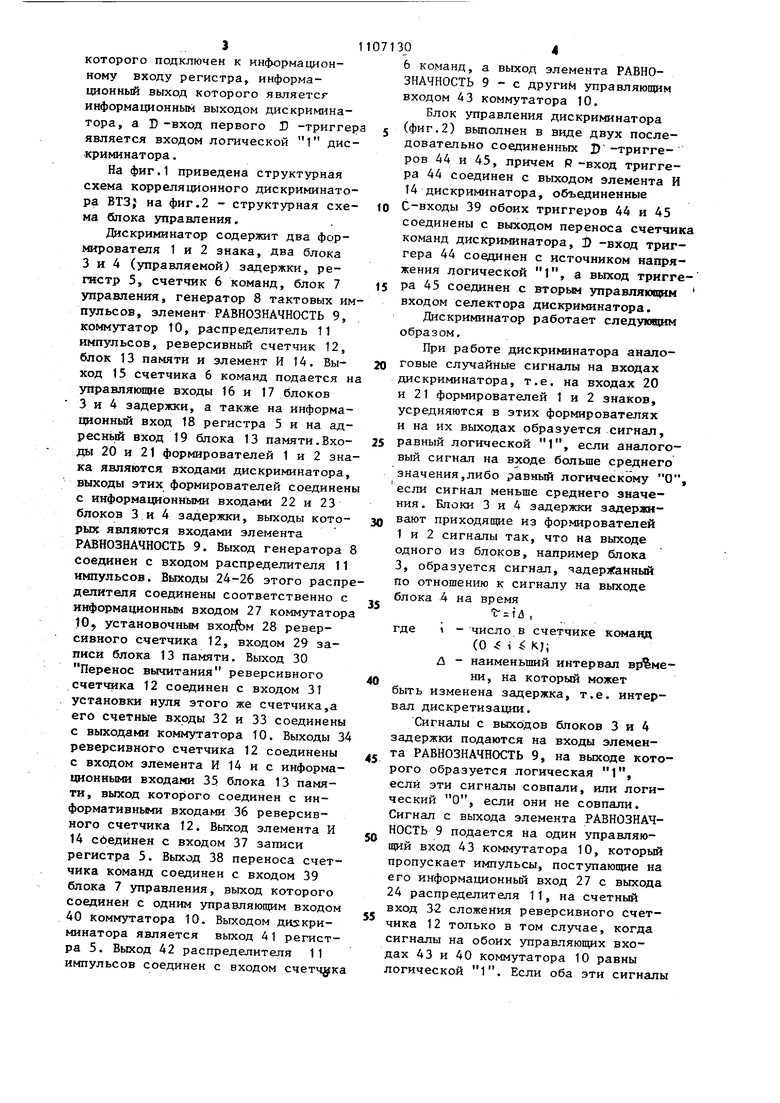

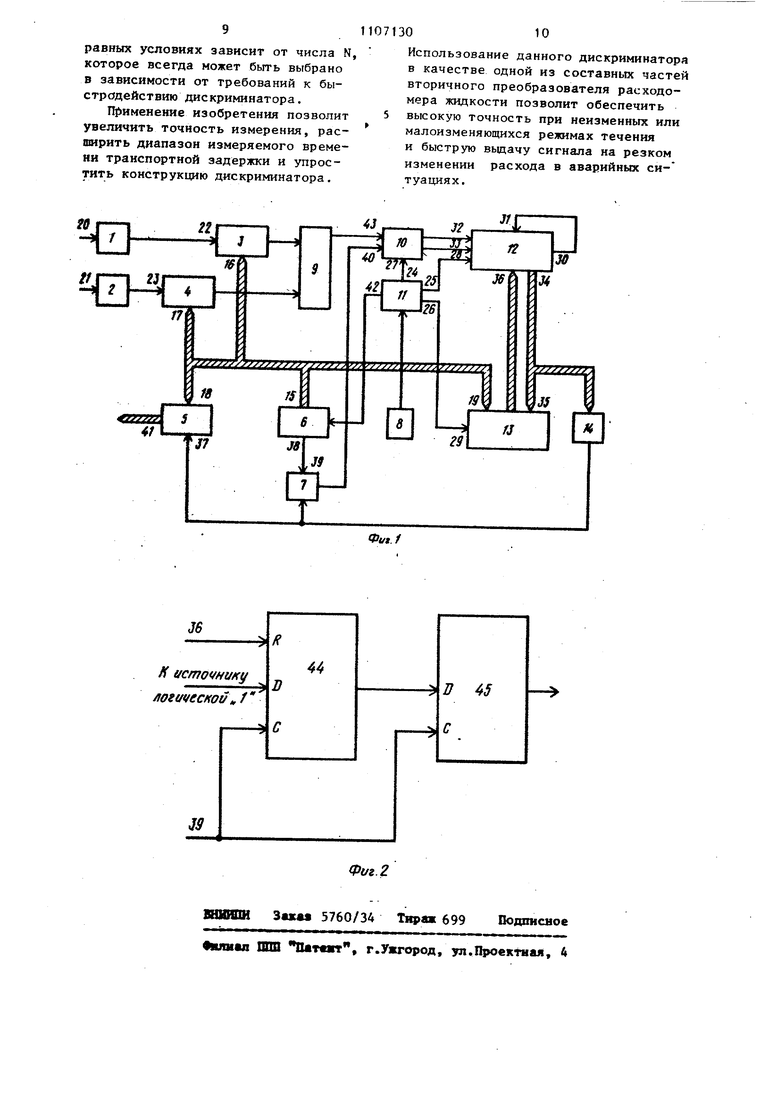

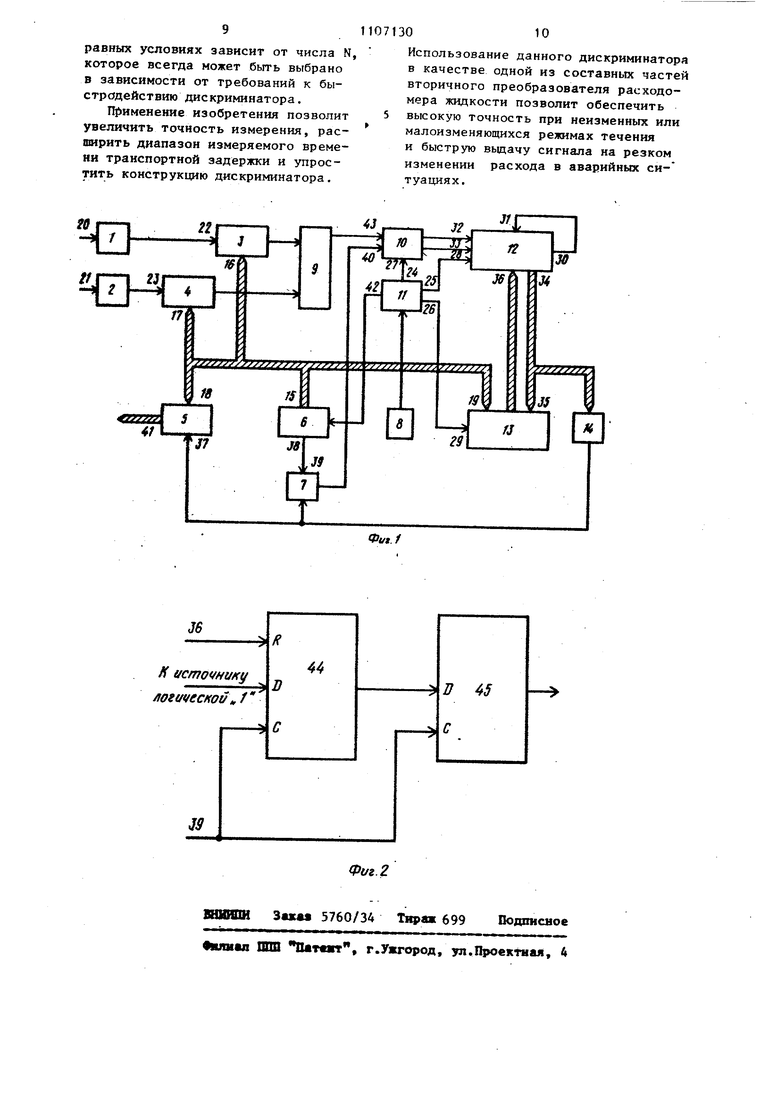

1 Изобретение относится к вычислительной технике и приборостроению и может быть использовано в аппаратуре корреляционного анализа и в приборах для измерения cKopocfVi рас хода различных сред. Известны корреляционные дискриминаторы времени транспортного запаздывания (ВТЗ), осуществляющие поиск ВТЗ путем нахождения абсциссы максимума взаимокорреляционной функции f 1 3. Наиболее близким по технической сущности к предлагаемому является корреляционньй дискриминатор ВТЗ, содержащий элемент РАВНОЗНАЧНОСТЬ, первый и второй входы которого подключены к информационным выходам соответственно первого и второго блоков задержки, информацио ныв входы которых подключены к выходам соответственно первого и второго формирователей знака, входы которых являются соответственно пер вым и вторьв информационными входа « дискриминатора, генератор тактовых импульсов, выход которого подключен к входу распределителя импульсов, первый и второй выходы которого подключены соответственно к входу записи блока памяти и счет ному входу счетчика команд, информационный выход которого подключен к управляюпщм входам первого и вто рого блоков задержки и адресному входу блока памяти . Недостатком известного дискриминатора является малое количество задержек, в которых определяется величина взаимокорреляционной функ ции (ВКФ), что в свою очередь определяет низкую точность измерения ВТЗ. Упомянутый недос таток обусловлен сравнительно низким быстродействием существующих NMKPOпроцессоров. Количество задержек, при которых определяется ВКФ в зтом дискриминаторе при использовании .стандартного восьмиразрядного микр процессора, раАо 256, что недоста точно, например, для измерения ско рости в широком диапазоне ее изменения. Увеличить количество задержек в таком дискриминаторе можно лишь за счет увеличения разрядности микропроцессоров, так как эта разрядность пропорциональна количеств задержек. Однако требуемое увеличе ние (приблизительно иа ) пр 02 ведет к чрезмерному усложнению дискриминатора. Цель изобретения - повышений точности. Поставленная цель достигается тем, что в корреляционный дискриминатор времени транспортного запаздывания, содержащий элемент РАВНОЗНАЧНОСТЬ, первый и второй входы которого подключены к информационным выходам соответственно первого и второго блоков задержки, информационные входы которых подключены к выходам соответственно первого и второго формирователей знака, входы которых являются соответственно первым и вторым информационными входами дискриминатора, генератор тактовых импульсов, выход которого подключен к входу распределителя импульсов, первый и второй выходы которого подключены соответственно к входу записи блока памяти и счетному входу счетчика команд, информационный выход которого подключен к управляющим входам первого и второго блоков задержки и к адресному входу блока памяти, введены коммутатор, реверсивньй счетчик, регистр, первый и второй Т) -триггеры и элемент И, выход которого подключен к входу записи регистра и R -входу первого 1)-триггера, выход которого подключен к D -входу второго Э -триггера, выход которого подключен к входу первого разряда управляющего входа коммутатора, первый и второй выходы которого подключены соответственно к суммируквцему и вычитающему входам реверсивного счетчика, выход переноса вычитания которого подключен к входу установки О реверсивного счетчика, выход -го разряда которого подключен к t-му входу элемента И и входу i-го разряда информационного входа блока памяти, информационный выхсщ которого подключен к информащюнному входу реверсивного счетчика, установочный вход которого подключен к третьему выходу распределителя импульсов, четвертый выход которого подключен к информащюнному входу коммутатора, вход второго разряда управлякяцего входа которого подключен к выходу элемента РАВНОЗНАЧНОСТЬ, С-входы первого и второго D -триггеров подключены к выходу переноса счетчика команд, информационный выход I1 которого подключен к ин(}юрмацнонному входу регистра, информационный выход которого является информационным выходом дискриминатора, а Б -вход первого Т -триггер является входом логической 1 дискриминатора . На фиг,1 приведена структурная схема корреляционного дискриминатора BT3J на фиг,2 - структурная схема блока управления, Дискриминатор содержит два формирователя 1 и 2 знака, два блока 3 и 4 (управляемой) задержки, регистр 5, счетчик 6 команд, блок 7 управления, генератор 8 тактовых им пульсов, элемент РАВНОЗНАЧНОСТЬ 9, коммутатор 10, распределитель 11 импульсов, реверсивный счетчик 12, блок 13 памяти и элемент И 14. Выкод 15 счетчика 6 команд подается н управляквдие входы 16 и 17 блоков 3 и 4 задержки, а также на информационный вход 18 регистра 5 и на адресньй вход 19 блока 13 памяти,Входы 20 и 21 формирователей 1 и 2 зна ка являются входами дискриминатора, выходы этик формирователей соединен с инфopмaциbнны ш входами 22 и 23 блоков 3 и 4 задерзкки, выходы которьк являются входами элемента РАВНОЗНАЧНОСТЬ 9, Выход генератора соединен с входом распределителя 11 импульсов. Выходы 24-26 этого распр делителя соединены соответственно с информационным входом 27 коммутатор 10 J установочньм вхо;(Ьм 28 реверсивного счетчика 12, входом 29 записи блока 13 памяти. Выход 30 Перенос вычитания реверсивного счетчика 12 соединен с входом 31 установки нуля этого же счетчика,а его счетные входы 32 и 33 соединены с выходами коммутатора 10, Выходы 3 реверсивного счетчика 12 соединены с входом элемента И 14 и с информационными входами 35 блока 13 памяти, выход которого соединен с информативными входами 36 реверсивного счетчика 12. Выход элемента И 14 сбединен с входом 37 записи регистра 5. Выход 38 переноса счетчика команд соединен с входом 39 блока 7 управления, выход которого соединен с одним управляющим входом 40 коммутатора 10, Выходом диукриминатора является выход 41 регистра 5, Выход 42 распределителя 11 импульсов соединен с входом счетчик 04 6 команд, а выход элемента РАВНОЗНАЧНОСТЬ 9 - с другим управляющим входом 43 коммутатора 10. Блок управления дискриминатора (фиг.2) вьшолнен в виде двух последовательно соединенных 2)-триггеров 44 и 45, причем R -вход триггера 44 соединен с выходом элемента И 14 дискриминатора, объединенные С-входы 39 обоих триггеров 44 и 45 соединены с выходом переноса счетчика команд дискриминатора, 1) -вход триггера 44 соединен с источником напряжения логической 1, а выход триггера 45 соединен с вторым управлякнцим входом селектора дискриминатора. Дискриминатор работает следующим образом. При работе дискрию1натора аналоговые случайные сигналы на входах дискриминатора, т,е. на входах 20 и 21 формирователей 1 и 2 знаков, усредняются в этих формирователях и на их выходах образуется сигнал, равный логической 1, если аналоговый сигнал на входе больше среднего значения,либо равный логическому О, если сигнал меньше среднего значения. Блоки 3 и 4 задержки задерживают приходящие из формирователей 1 и 2 сигналы так, что на выходе одного из блоков, например блока 3, образуется сигнал, чадеряГанный по отношению к сигналу на выходе блока 4 на время где - число в счетчике ксмавд (О .5 i KJJ д - наименьший интервал ни, на который может быть изменена задержка, т.е. интервал дискретизации. Сигналы с вьлходов блоков 3 и 4 задержки подаются на входы элемента РАВНОЗНАЧНОСТЬ 9, на выходе которого образуется логическая 1, если эти сигналы совпали, или логический О, если они не совпали. Сигнал с выхода элемента РАВНОЗНАЧНОСТЬ 9 подается на один управляющий вход 43 коммутатора 10, который пропускает импульсы, поступающие на его информационный вход 27 с выхода 24 распределителя 11, на счетный вход 32 сложения реверсивного счетчика 12 только в том случае, когда сигналы на обоих управляющих входах 43 и 40 коммутатора 10 равны логической 1. Если оба эти сигналы 5 равны логическому О, то импульсы с выхода 24 распределителя 11 посту пают на счетный вход 33 вычитания реверсивного счетчика 12. Во всех ;других случаях импульсы на статные входы 32 и 33 реверсивного счетчика 12 не проходят. Таким образом, в t такте (когда в счетчике 6 команд за писано число W ) в реверсивном сче чике 12 происходит увеличение его содержимого на единицу,если на управляющем входе 40 коммутатора 10 есть состояние логической 1, а входные сигналы, задержанные по отношению друг к другу на время f:id I совпадают. Если же на управ ляющем входе 40 Коммутатора tO существует состояние логического О, то . реверсивном счетчике 12 происходит уменьшение его содержимого на единицу при условии, что входные сигналы, задержанные по от ношению друг к другу на время не совпадают. Состояние иа управляющем входе 40 коммутатора 1 совпадает с состоянием на выходе блока 7 управления. На вход 39 этого блока, т.е. на объединенные С-входы триггеров 44 и 45 (фиг.2), подается импульс с выхода 38 переноса счетчика 6 команд. Эти импуль сы устанавливают выход триггера 45 т.е. выход блока управления, в то состояние, в котором перед приходо импульса Перенос находился тригг 44. Этим же импульсом триггер 44 устанавливается в состояние логической 1. В свою очередь перед приходом импульса Перенос тригге 44 может находиться в состоянш ло гического О только после прихода на R-вход триггера 44, т.е. на другой вход блока управления,им пульса с элемента И 14. Таким обра зом, состояние логического О на управляющем входе 40 коммутатора 10 образуется лищь после поступлен на вход 39 блока 7 управления импу са с выхода 38 переноса счетчика 6 команд только ««осле поступления импульса с элемента И 14, который образуется, если число на входе в этот элемент равно некоторому числу N. Елок 13 памяти состоит иэ К ячеек, в каядую из которых может быть записано число от нуля до N. Такой блок памяти может быть реали зован, например, в виде ОЗУ,содержащего К слов каждое не менее,чем 06 togj N 5и7 Так как адресные входы 19 блока 13 памяти соединены с выходами 15 счетчика 6 команд, то в i такте возможно лишь обращение к i-и ячейке этого блока. Для простоты можно считать,что в начале работы дискриминатора во всех ячейках накопителя записан ноль. При этом на управляющем входе 40 коммутатора 10 существует состояние логической 1, т.е. дискриминатор работает в режиме Сложение совпадений. В начале такта импульс с выхода 42 распределителя 11 импульсов поступает на вход счетчика 6 команд, в котором устанавливается Код числа t I затем с выхода 25 распределителя 11 поступает импульс на установочный вход 28 реверсивного счетчика 12, при этом содержимое (-и ячейки блока 13 памяти вписывается в реверсивньй счетчик 12. Далее импульс с выхода 24 распределителя 11 в случае совпадения задержанных на сигналов через коммутатор 10 проходит на вход 32 сложения реверсивного счетчика t2. В конце i-го такта импульс с выхода 26 распределителя 11 поступает на вход 29 записи блока 13 памяти и происходит запись нового числа из реверсивного счетчика 12 в ту же i-ю ячейку блока 13 памяти. Таким образом, за каждый цикл перебора всех чисел в счетчике 6 от О до К содержимое каждой i-й ячейки будет увеличиваться на единицу, если исходные сигналы, задержанные по отношению друг к другу на время T ifl, совпадают. Циклы в режиме Сложение совпадений будут следовать друг за другом, пока хотя бы в одной j ячейке не образуется число равное Н, после чего по импульсу с элемента И 14 а следующем Щ1кле блок 7 управления переведет управляющий вход 40 коммутатора 10 в состояние логического О. При этом дискриминатор перейдет в режим Вычитание несовпадений, а в регистр 5 будет вписано число J. В этом режиме содержимое каждой i -и ячейки уменьшится на 1, если исходные сигналы, задержанные по отношению друг к другу на время С 1Д, не совпадают. Указанный ре-, жим будет продолжаться до тех пор, пока числа во всех ячейках не станут меньше N, после чего дискриминатор переГгдет в режим Сложение совпадений и т.д. В течение длительной работы дискриминатора в его блоке 13 памяти могли бы образоваться и отрицательные числа. Однако вместо н-их в соответствующую ячейку блока памяти вписывается число ноль, так как при образовании отрицательного числа на выходе 30 Перенос вычитания ревер сивного счетчика 12 образуется импульс, которьм, попадая на вход 31 этого счетчика, устанавливает его в ноль и этот ноль вписывается в блок памяти. Из описанного принципа работы ди криминатора следует, что скорость увеличения числа в /i-и ячэйке равна частоте совпадений знаков исходных сигналов, один из которых задержан по отношению к другому пз. время скорость уменьшения равна час тоте несовпадений этих сигналов. Но в среднем частота coвпaдeн iй и несовпадений пропорциональна их вероя ности. Известно, что вероятность совпадений тем больше, а вероятност несовпадений тем меньше, чем выше величина знаковой БКФ. Отсюда следует , что максимальным будет число в той ячейке, номер которой j определяет задержку , при которой ВКФ достигает максимума. Максимально возможное число Б накопителе равно N, при достилсенни которого на выходе дискриг и ;атора в регистре образуется код i ячей ки, определяющий ВТЗ, равное . В данном дискриминаторе вьСокое быстродействие достигается за счет использования вместо -дакропроцессора реверсивного счетчика, быстродействие которого на порядок выше. Так, например, в случае использования ТТ-технологии быстродействие счетчиков приближенно равно 10 МГц а эффективное быстродействие микропроцессоров, учитывая, что каждая операция в них выполняется в резуль тате нескольких микрокоманд, iie пре вышает 1 МГц. Учитывая, что быстродействие определяет количество задержек, в которых в реж1{ме реального времени определяется значение ВКФ,предлагаемый дискриминатор позволяет значительно (до нескольких тысяч) повысить количество этих точек, а следовательно,и точность из08мерения. При этом повъппение точности достигается за чет использования меньшего количества и более простых элементов, чем при применении М1 кропроцессора, гак как в последнем случае в состав микропроцессорного ршбора должны входить дополнитапьные элементы, такие как блок микропрограммного управления, различные буферные регистры и т.д. В отдичие от тех известных дискриминаторов, в которых поиск ВТЗ про}:слодг Т путем перебора значений ВКФ при всех задержках, где эта ВКФ определяется, предлагаемый дискриминатор обеспечивает высокую (не xy::se 0,1%) статистическуто Toq i:;Cf. язггеренгЯ при устгановившемсл ВТЗ и при ЭТОГ5 имеет конечную достаго-п-io высокую стчорссть отклика на изменение ВТЗ, г,е, обладает достаточно высоким быстродействием. Деиств 1 тельно, еслгг представмть, что в блок памяти ош1сываемого дисKpuf-EiiTaropa записывались бы все числа меньнте мли равные N, в том числе и отрнцате: Ы)Ые, то в ячейках такого бесконечного блока памяти в Te eHiie всего времени работы дискриминатора с ко1.аента его включения образооалась бы некоторая последовательность чисап больших, чем Еьпяе значение ВКФ при задержке Гг i Л . соответстзующей номеру данной ячейки i Очевидно, что при неизменной ВКФ пос.педовательность 4iice.T 3 реальном блоке памяти отличается от описанной лишь тем, что отрицательных чисел в его ячейках будет вписан ноль. Положительные же числа в районе максимума ВКФ будут совпадать. Следовательно, в том и другом случаях будут совпадать и номера ячеек j , определяющлх ВТЗ, равное , При неизменной ВТЗ время интегрирования предлагаемого дискриминатора может практически равняться времени,, в течение которого ВТЗ оставалось неизменньЯ. Очевидно, что точность дискрим 5на11;ии ВТЗ при этом максимальна. С другой стороны,так как максимально возможное число N в блоке памяти конечно, то конечно при изменении ВКФ и время полного заполнения новой ячейки с номером, соответствующем MaKCHMyNfy изменной ВКФ, Это время, определяющее быстродействие диcкpи D нaтopa, при прочих

равных условиях зависит от числа N, которое всегда может быть выбрано в зависимости от требований к быстродействию дискриминатора.

П1Ьименение изобретения позволит увеличить точность измерения, расширить диапазон измеряемого времени транспортной задержки и упростить конструкцию дискриминатора,

чп

13010

Использование данного дискриминатора в качестве одной из составных частей вторичного преобразователя расходомера жидкости позволит обеспечить 5 высокую точность при неизменных или малоизменяющихся режимах течения

и быструю выдачу сигнала на резком изменении расхода в аварийных си- туациях.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1117627A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1985 |

|

SU1840045A1 |

| Запоминающее устройство | 1984 |

|

SU1182577A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1361577A1 |

КОРРЕЛЯЦИОННЫЙ ДИСКРИМИНАТОР ВРЕМЕНИ ТРАНСПОРТНОГО ЗАПАЗДЫВАНИЯ, содержащий элемент РАВНОЗНАЧНОСТЬ, первый и второй входы которого подключены к информахдюнным выходам соответственно первого и второго блоков задержки, информационные входы которых подключены к выходам соответственно первого и второго формирователей знака, входы которых являются соответственно первым и вторым информационными входами дискриминатора, генератор тактовых импульсов, выход которого подключен к входу распределителя импульсов, первый и второй выходы которого подключены соответственно к входу записи блока памяти и счетному входу счетчика команд, информационный выход которого подключен к управляющим входам первого и второго блоков задержки и к адресному входу блока памяти, о тличающийся тем, что, с целью повышения точности, в него введены коммутатор, реверсивный счетчик, регистр, первый и второй D-триггеры и элемент И, выход которого подключен к входу записи регистра и R -входу первого D -триггера , выход которого подключен к D-ВХОДУ второго Т) -триггера, выход которого подключен к входу первого разряда управляющего входа коммутатора , первый и второй выходы которого подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, выход переноса вычитания которого подключен к входу установки О реверсивного счетчика, выход i-го разряда которого подключен к .1-му входу элемента И и входу i-го разряда информационного входа блока памяти, информационней выход которого подключен к информационному входу реверсивного счетчика, установочный вход которого подключен к третьему выходу распре делителя импульсов, четвертый выход которого подключен к информационному СО входу коммутатора, вход второго разряда управлякяцего входа которого подключен к выходу элемента РАВНОЗНАЧНОСТЬ, С-входы первого и второго D-триггеров подключены к выходу переноса счетчика команд, информационный выход которого подключен к информационному входу регистра, информационный выход которого является информационным выходом дискриминатора , а D -вход первого D-триггера является входом логической 1 дискриминатора.

J6

44

к источнику

D

логической f

и 45

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Жовинский В.Н.,Арховский В.Ф | |||

| Корреляционные устройства | |||

| М., Энергия, 1974 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Massen R., Merkei., Linder K.F | |||

| Non-contact velcjcityneagurment with a new microprocessor based industriaf correbator | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-15—Подача