I

Изобретение относится к запоминающим устройствам и может быть использовано, в частности, в информационно-управляющих системах, ра ботающих в режиме реального масштаба времени.

Известно устройство для защиты памяти, содержог ее граничные регистры и компараторы для сравнения кода исполнительного адреса с кодами адресов, установленными в этих регистрах 1.

Недостатком этого устройства является невысокая надежность.

Наибодее близким техническим решением к предлагаемому является устройство для защиты памяти, содержащее депшфратор адресов зон, блоки сравнения, соответствующие им пары элементо1в И, регистр и дешифратор признака обращения и два элемента ИЛИ, причем выходы дешифратора адресор зон подключены ко входам блоков сравнения, выходы которых сое

динены с первыми входами элементов И, вторые входы элементов И соединены попарно с соответствующими выходами дешифратора признака обращения, вход которого подключен к выходу регистра признака обращения, выходы всех элементов И соединены с соответствующими входами первого и второго элементов ИЛИ 2.

Недостатком этого устройства яв10ляется невысокая надежность, так как оно не позволяет.создавать за- щшцаемые поля памяти различной конфигурации, а также требует избыточного объема памяти для размещения

«S программ. .

Цель изобретения - повышение надежности устройства.

Указанная цель достигается тем, что в устройство для защиты памяти,

20 содержащее дешифратор кодов, страниц, регистр кодов-защиты страниц, элемент ИЛИ и первую грушту элементов И, причем выходы дешифратора кодов страниц подключены соответственно к первым входам элементов И первый группы, вторые входы которых соединены соответственно с выходами регистра кодов защиты страниц, вход дешифратора кодов страниц и выход элемента ИЛИ являются соответственно первым входов и выходом устройства, введены дешифратор кодов абзацев и дешифратор кодов строк, входы которых являются соответственно вторым и третьим входами устройства, регистры кодов защиты абзацев,регистры кодов защиты строк, вторую и третью группы элементов И и группу элементов ИЛИ, причем выходы дешифратора кодов абзацев соединены с первыми входами соответствующих элементов И втор-ой г 1уппы, вторые входы которых подключены к выходам соответствующих элементов И первой . группы, а третьи входы - к ьыходам соответствующих регистров кодов за- щиты абзацев, выходы дешифратора кодов страниц соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых подключены к выходам соответствую щих элементов И второй группы, а тре.тьи входы - к выходам соответствующих регистров кодов защиты стфок, входы элементоб ИЛИ группы соединены соответственно с выходами элементов И третьей группы, а выходы элементов ШШ группы подключены, соответственно ко входам элемента ИЛИ.

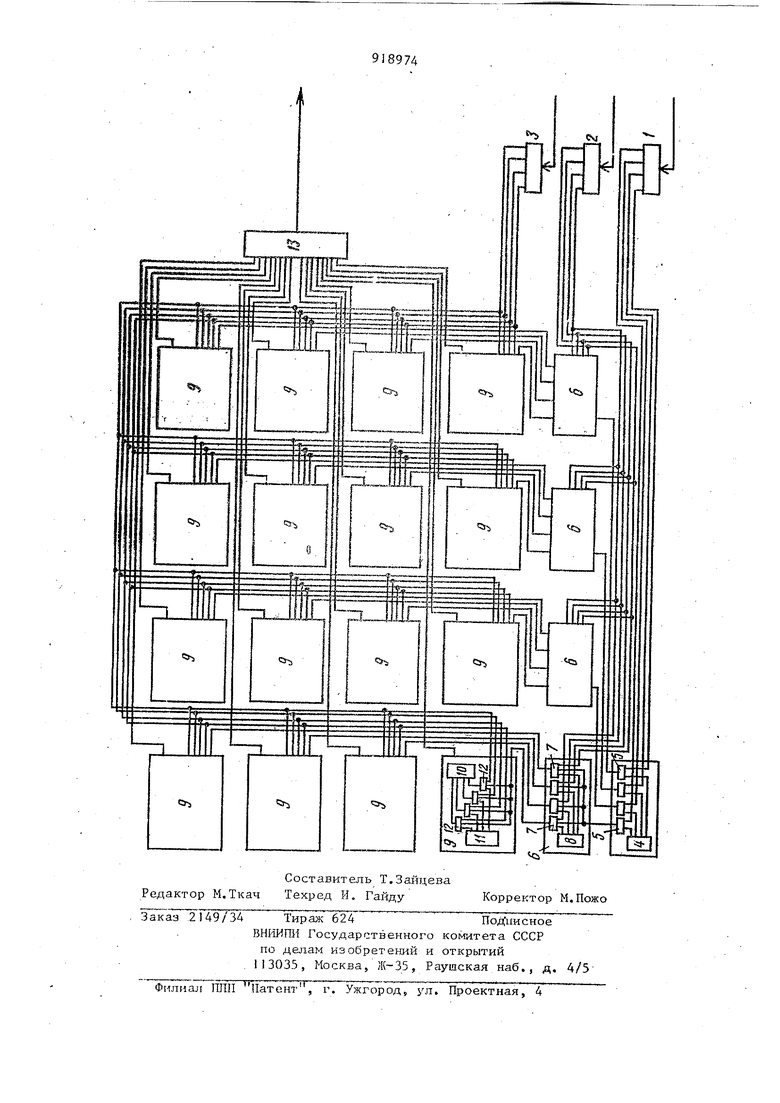

На чертеже изображена структурная схема предлагаемого устройства для защиты памяти объемом, например, в четьфе страницы по четыре абзаца в каждой и по четыре строки в каждом абзаце.

Устройство содержит дешифратор 1 кодов страниц, дешифратор 2,кодов абзацев, дешифратор 3 кодов строк, регистр 4 кодов защиты страниц, элементы И 5 первой группы, логические блоки 6, содержащие элементы И 7 второй группы и регистры 8 кодов защиты абзацев, логические блоки. 9, содержащие элементы ИЛИ 10 группь, регистры 11 кодов защиты строк и элементы И 12 третьей группы, и элемент

ИЛИ 13.

Устройство работает спедукщим образом.

Устройство выполняет аппаратурным путем проверку исполнительных адре-

сов на совпадение их сразрешенными адресами.

Для каждой программы с целью обеспечения доступа только к выделенным 5 ей участкам памяти - страницам, абзацам, строкам - управляющей программой формируются коды защиты этих участков. Перед началом выполнения очередной программы сформированные позиционные коды защиты заносятся в соответствующие регистры,4, 8 и И кодов защиты страниц, абзацев и . За каждым разрядом этих регистров 4, 8 и 11 закрепляются соответствующие страницы, абзацы и строки защищаемой памяти.

В соответствии с общепринятым принхщпом защиты, согласно которому разрешения должны преобладать над запретами, исходным состоянием всех -регистров 4, 8 и является нулевое. Это значит, что нулевому состоянию разряда регистра 4 соответствует разрешение обращаться к соответствую-

5 щей странице , единичному - запрещение. Аналогичные рассуждения относятся к регистрам 8 и 1I.

Исполнительный адрес поступает на входы дешифраторов 1, 2 и 3, причем

Q старшие разряды адреса поступают на .вход дешифратора 1, средние разряды на вход дешифратора 2 и младшие разряды - .на вход дешифратора 3. . Расшифрованный код страницы с выхода дешифратора 1 поступает на первый вход одного из элементов И 5. Ее- ли соответствующий разряд регистра 4, выход которого подключен ко второму входу эт.ого же элемента И 5, находится в нулевом состоянии, то

на выходе этого элемента И 5 появится сигнал, который поступит во вторые входы всех соответствующих элементов И 7. На первый вход одного из этих элементов И 7 поступает рас-

шифрованный код абзаца с выхода дешифратора 2. Если соответствующий разряд регистра 8,который соединен с третьим входом этого элемента И 7, находится в нулевом состоянии, то

на выходе этого элемента И 7 появится сигнал, который поступит на вторые входы всех соответствукшдах элементов И 12. На третий вход одного из этих элементов И 12 поступает

5 расшифрованный код строки с выхода дешифратора 3. Если соответствукщий разрад.регистра 11, которьй соединен с третьим входом этого элемента И 12,

находится в нулевом состоянии то на выходе этого элемента И 12 по явится сигнал, который поступит на один из входов со тветствующего элемента ИЖ 10 а с его выхода - на вход элемента ШШ 13 и затем пройдет на выход устройства как сигнал разрешения на обращение к памяти по данному исполнительному ддресу.

Таким образом, сигнал разрешения сформируется только при совпадении всех .трех расшифрованных дешифраторами 1, 2 и 3 кодов страницы, абзаца и строки с нулевыми состояниями соответствующих разрядов регистре 4, 8 и 11. В противном случае сигнал разрешения будет отсутствовать, что и явится признаком несанкционированного обращения и память по данному адресу.

Технико-экономические преимущества предлагаемого устройства по сравнению с Известным заключаются в повышении надежности устройства и обеспечении сокращения объема защищаемой памяти, необходимого для размещения программ защиты.

3.

Формула изобретения

Устройство для защиты памяти, содержащее дешифратор кодов страниц, регистр кодов защиты страниц элемент ИЛИ и первую группу элементов И, причем выходы дешифратора кодов страниц подключены соответственно к первым входам элементов И первой группы, вторые входы которых соединены соответственно, с выходами регистра кодов защиты страниц, вход; дешифратора кодов страниц и выход элемента ИЛИ являются соответственно первым входом и выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, оно с.одерж1гт дешифратор кодов абзацев и дешифратор кодов строк, входа которых являются соответственно вторым и третьим входами устройства,

регистры кодов зашиты абзацев, регистры кодов защиты строк, вторую и третью группы элементов И и группу элементов ШШ, причем выходы дешифратора кодов абзацев соединены с

первыми входами соответствующих элементов И второй группы вторые входы которых подключены к выходам соответствукщих элементов И первой группы, а третьи входы - к выходам

соответствующ 1х регистров кодов защиты абзацев, выходы дешифратора кодов страниц соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых

подключеШ) к выходам соответствунядих элементов И второй группы, а третьи входы - к выходам соответствующих регистров кодов защиты строк, входы элементов ШШ группы соединены соответственно с вьгеодами элементов И третьей группы, а выходы элементов ШШ .группы подключехД) соот.ветственпо к элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании

№ 1282628, кл, G4 А, опублик. 1972.

2.Авторское свидетельство СССР № 552641, кл. G 11 С 29/00, 1977

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты памяти | 1988 |

|

SU1509910A1 |

| Устройство для вывода информации | 1984 |

|

SU1180876A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для контроля трассировки и воспроизведения информации о прокладке кабельной трассы | 1984 |

|

SU1238106A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1256084A1 |

| Устройство для управления виртуальной памятью | 1986 |

|

SU1327113A2 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

Авторы

Даты

1982-04-07—Публикация

1980-08-21—Подача