триггера и с первыми входами третье го и четвертого элементов И, первьй и второй выходы условий первого блока памяти подключены соответс венно к единичному входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпул сов устройства через третий элемент задержки соединен с первым счетным входом второго регистра адреса, нулевой выход первого триггера подключен к второму входу четвертого элемента И, единичный выход - к вто рому входу третьего элемента И и к управляющему входу выбора приемавьщачи регистров символа, вход управления выдачей регистра выдачи соединен с выходом шестого элемента И, единичный выход второго триггера подключен к первому входу шестого элемента И и к вторым входам первого и пятого элементов И, нулевой выход второго триггера соединен с вторым входом второго элемента И выход второгоэлемента задержки подключен к третьему входу пятого элемента И и через четвертый элемен задержки - к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента Н подключен к второму входу первого элемента ИЛИ, выход которого соединен с установочными входами третьего триггера, первого и второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра вьщачи, входы и выход седьмого элемента Н соединены соответст венно с выходами разрядов второго регистра адреса и с единичньгм входо третьего триггера, единичный выход которого подключен к выходу индикации ошибки устройства, второй выхсд схемы сравнения соединен с управляющим входом приема второго регистра адреса, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения трансляции с макроязыков, в него введены третий регистр адреса, второй блок памяти, переключатель, восьмой и девятый элементы И, второй элемент КШ и четыре элемента задержки, причем ход шестого элемента И через пятый элемент задержки подключен к первому входу восьмого элемента И, инверсный выход первого разряда регистра выдачи подключен к управляющему входу вывода переключателя и к второму входу восьмого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, подключенного выходом к управляющему входу останова генератора прямоугольных импульсов и к единичному входу второго триггера, прямой выход первого разряда регистра вьщачи соединен с первым счетным входом третьего регистра адреса, с первым входом девятого элемента И и через шестой элемент задержки - с входом управления считыванием второго блока памяти, первый информационный выход которого подключен к второму входу второго элемента ИЛИ, информационные.выходы, начиная с второго, второго блока памяти соединены с первой группой информационных входов переключателя, выходы разрядов регистра выдачи, кроме первого, подключены к второй группе информационньк входов переключателя и к информационным входам третьего регистра адреса, выходы разрядов которого соединены с адресными входами второго блока памяти, нулевой выход второго триггера через седьмой элемент задержки подключен к второму входу девятого элемента И, выход которого соединен с входом травления приемом третьего регистра адреса, информационные входы второго блока памяти подключены к третьей группе информационных входов устройства, третий вход синхроимпульсов которого соединен с управляющим входом записи второго блока памяти и через восьмой элемент задержки - с вторым счетным входом третьего регистра адреса, вход установки нуля которого подключен к входу установки исходного состояния устройства, выходы переключателя являются информационными выходами устройства.

1

Изобретение относится к вычислительной технике, предназначено для преобразования кодов с одного языка на другой, в частности для трансляции с языков программирования микропроцессоров, а также для трансляции с макроязыков и может применяться в условиях возможной с смены или модификации используемых языков программирования.

Известно устройство для аппаратурной трансляции, выполненное на основе взаимосвязанных регистра вьщачи, блока памяти, регистров символа, элемента ИЛИ, шести элементов И, схемы сравнения, двух регистров адреса, дешифратора кода пробела, двух триггеров, генератора прямоугольных импульсов, четырех элементов задержки и дешифратора. Аппаратурная реализация данного устройства ягшяется независимой от используемых языков. Настройка его на конкретные языки программирования осуществляется путем составления карты заполнения блока памяти на основе несложного преобразованиятаблиц соответствия символических и двоичных кодов вхоного и выходного языков С11|.

Недостатками данного технического решения являются невозможност выявления недопустимых входных конструкций, а также невозможность трансляции макрокоманд.

Наиболее близким к изобретению по технической сущности является устройство для аппаратурной трансляции, содержащее семь элементов И элемент ИЛИ, регистры символа, регистр вьщачи, схему сравнения, два регистра адреса, дешифратор кода пробела, три триггера, генератор прямоугольных импульсов, четыре элмента задержки, дешифратор и блок памяти, вход записи, информационны входы и информационные выходы которого подключены соответственно к первому входу синхроимпульсов устройства, к первой группе информационных входов устройства и к первой группе входов регистра вьщачи, выходы и вторая группа входов которого соединены соответственно с выходами устройства и с выходами регистров символа, информационные входы которых подключены к второй группе информационных входов устройства, входы и выходы депшфрато15063 2

ра соединены соответственно с выходами первого регистра адреса и с управляюпщми входами регистров символа, входы которых подключены к первой группе информационных входов схемы сравнения, вторая группа информационных входов которой соедчнена с информационными выходами блока памяти, информационные входы первого и второго регистров адреса подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами второго регистра адреса, вторая группа информационных входов устройства подключена к входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоугольных импульсов, выход которого подключен к входу считывания блока памяти и через первый элемент задержки - к входу второго элемента задержки и к первым входам первого и второго элементов И, выход первого элемента И соединен с первыми управляющими входами приема первого регистра адреса .и регистра вьщачи, выход второго элемента И подключен к управляющему входу схемы сравнения, первый выход которой соединен с вторым управляющим входом приема первого регистра адреса и с первым счетным входом второго регистра адреса, второй вькод схемы сравнения соединен с управляющим входом приема второго регистра адреса, вход установки исходного состояния устройства подключен к установочным входам первого и второго триггеров и к первому входу первого элемента ИЛИ, второй вход синхроимпульсов устройства соединен с вторым входом первого триггераи с первыми входами третьего и четвертого элементов И, первый и второй выходы условий блока памяти подключены к первому входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпульсов устройства соединен через третий элемент задержки с первым счетным входом второго ре- гистра адреса, инверсный выход первого триггера подключен к второму входу четвертого элемента И, прямой выход - к.второму входу третьего элемента И и к входу выбора приема-вьщачи регистров символа.

3

второй вход триггера и вход управления вьщачей регистра вьщачч соединен с выходом шестого элемента И, прямой выход второго триггера подключен к первому входу шестого элемента Инк вторым входам первого и пятого элементов Р1, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки - к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента И подключен к второму входу элемента ИЛИ, выход которого соединен с установочными входами третьего триггера, первого и второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра вьщачи, вход и выход седьмого элемента И соединены соответственно с выходамивторого регистра адреса и с информа- щгонным входом третьего триггера, прямой выход которого подключен к выходу индикации ошибки C2J.

Однако известное устройство не позволяет выполнять трансляцию макрокоманд, когда одной конструкции входного языка ставится в соответствие несколько самостоятельных конструкций выходного языка, т.е. оно не позволяет вьтолнять трансляцию с микроязыков. Это приводит к сужению класса языков, для которых может быть организован процесс трансляции с помощью данного устройства, а следовательно и области его применения. Макропрограммирование является широко распространенным и эффективным методо построения программ в вьиислительной технике, поэтому отсутствие возможности трансляции с макроязыков является существенным недостатком.

Целью изобретения является расширение функциональных возможностей путем обеспечения трансляции с макроязыков.

Поставленная цель достигается тем, что в устройство, содержащее семь элементов И, первый элемент ИЛИ, регистры символа, регистр вы50634

дачи, схему сравнения, два регистра адреса, дешифратор кода пробела, три триггера, генератор прямоугольных импульсов, четьфе элемен5 та задержки, дешифратор и первый блок памяти, управляющий вход записи, информационные входы и информационные выходы которого подключены соответственно к первому вхо10 ДУ синхроимпульсов устройства, к первой группе информационных входов устройства и к первой группе информационных входов регистра выдачи, вторая группа информационных

15 входов которого соединена с выходами разрядов регистров символа, информационные входы которых подключены к второй группе информационных входов устройства, входы и вы20 ходЫ дешифратора соединены соответственно с выходами разрядов первого регистра адреса и с управляющими вxoдal Iи записи регистров символа, выходы разрядов которых под25 ключены к первой группе информационных входов схемы сравнения, вторая группа информационных входов которой соединена с информационными выходами первого .блока памяти, инЭ-. формационные входы первого и второго регистров адреса подключены к информационным выходам первого блока памяти, адресные входы которого соединены с выходами разрядов второго регистра адреса, вторая группа информационных входов устройства подключена к входам дешифратора кода пробела, выход которого соединен с установочным вхоQ дом первого триггера и с управляющим входом запуска генератора прямоугольных импульсов, выход которого подключен к управляющему входу считывания первого блока памяти

5 и через первьй элемент задержки к входу второго элемента задержки и к первым входам первого и второго элементов И, выход первого элемента И соединен с первыми управ0 ляющими входами приема первого регистра адреса и регистра вьщачи, выход второго элемента И подключен к управляющему входу разрешения сравнения схемы сравнения, первый

55 выход которой соединен с вторым управляющим входом приема первого регистра адреса и с первым счетным входом второго регистра адреса.

5

вход установки исходного состояния устройства подключен к установочным входам исходного состояни первого и второго триггеров и к первому входу первого элемента ИЛИ второй вход синхроимпульсов устройства соединен с единичным вхо дом первого триггера и с первыми входами третьего и четвертого элементов И, первый и второй выходы условий первого блока памяти подключены соответственно к единичному входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпульсов устройства через третий элемент задержки соединен с первым счётным входом второго регистра адреса, нулевой выход первого триггера подключен к второму входу четвертого элемент И, единичный выход - к второму входу третьего элемента И и к управляющему входу выбора приема-выдачи регистров символа, вход управления вьщачей регистра вьщачи соединен с выходом шестого элемента И, единичный выход второго триггера подключен к первому входу шестого элемента И и к вт.орым входам первого и пятого элементов И, нулевой выход второго триггера соединен с вторым входом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки - к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента И подключен к второму входу первого элемента ИЛИ, выход которого соединен с установочными входами трет го триггера., первого и второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра выдачи, входы и выход седьмого элемента И соединены соответственно с выходами разрядов второго регистра адреса и с единичным входом третьего триггера, единичный выход которого подключен к выходу индикации ошибки устройства, второй выход схемы сравнения соединен с управляюшим входом приема второго регистра адреса, введены третий регистр адреса, второй блок памяти, переключатель, восьмой

5063 6

и девятый элементы И, второй элемент ИЛИ и четыре элемента задержки, причем выход шестого элемента И через пятый элемент задержки 5 подключен к первому входу восьмого элемента И, инверсный выход первого разряда регистра выдачи подключен к управляющему входу вывода переключателя и к второму . входу

10 восьмого элемента И, выход которого соединен с первым входом второго элемента ИЖ, подключенного выходом к управляющему входу останова генератора прямоугольных импульсов

1-5 и к единичному входу второго триггера, прямой выход первого разряда регистра выдачи.соединен с первым счетным входом третьего регистра адреса с первым входом девятого

20 элемента И и через шестой элемент задержки - с входом управления считыванием второго блока памяти, первый информационный выход которого подключен к второму входу второ-

25 го элемента ИЛИ, информационные выходы, начиная с второго, второго блока памяти соединены с первой группой информационных входов переключателя , выходы разрядов регист30 ра выдачи, кроме первого, подключены к второй группе информационных входов переключателя и к информационных входам третьего регистра адреса, выходы разрядов которого соединены с адресными входами второго блока памяти, нулевой выход второго триггера через седьмой элемент задержки подключен к второму входу девятого элемента И, выход

которого соединен с входом управления приемом третьего регистра адреса, информационные вхоДы второго блока памяти подключены к третьей группе информационных входов устройства, третий вход синхроимпульсов которого соединен с управляющим входом записи второго блока памяти и через восьмой элемент задержки с вторьм счетным входом третьего регистра адреса, вход установки нуля которого подключен к входу установки исходного состояния устройства, выходы переключателя являются информационными выходами устройства.

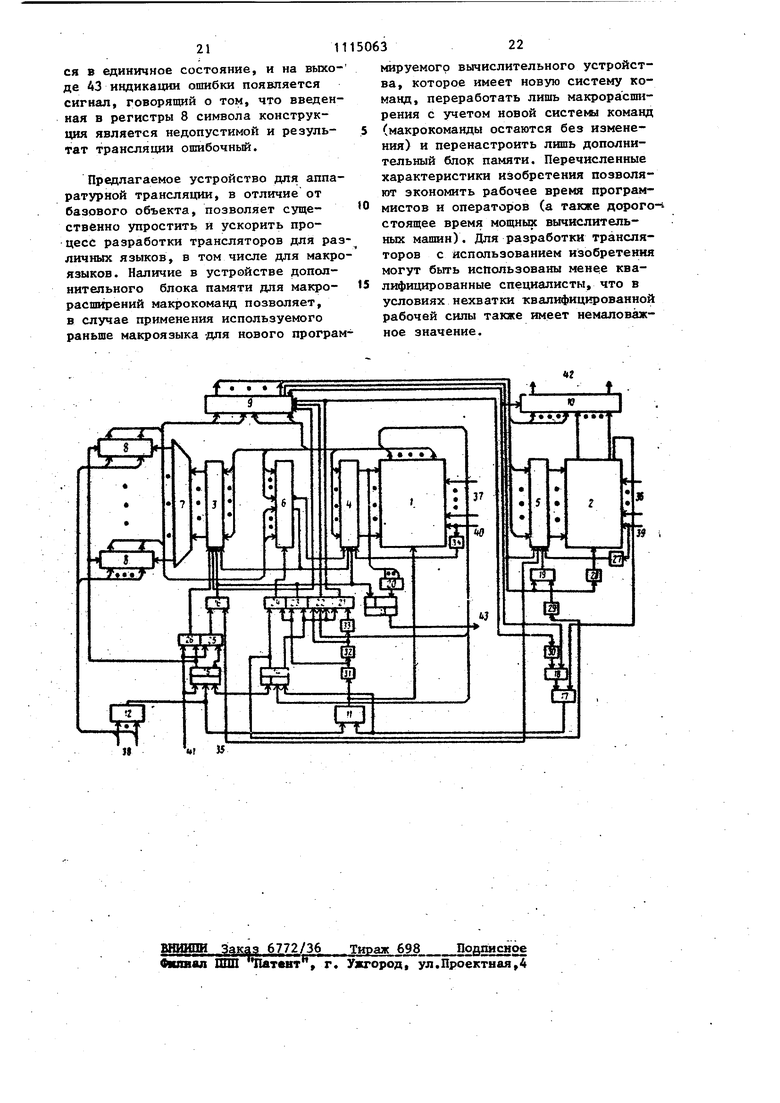

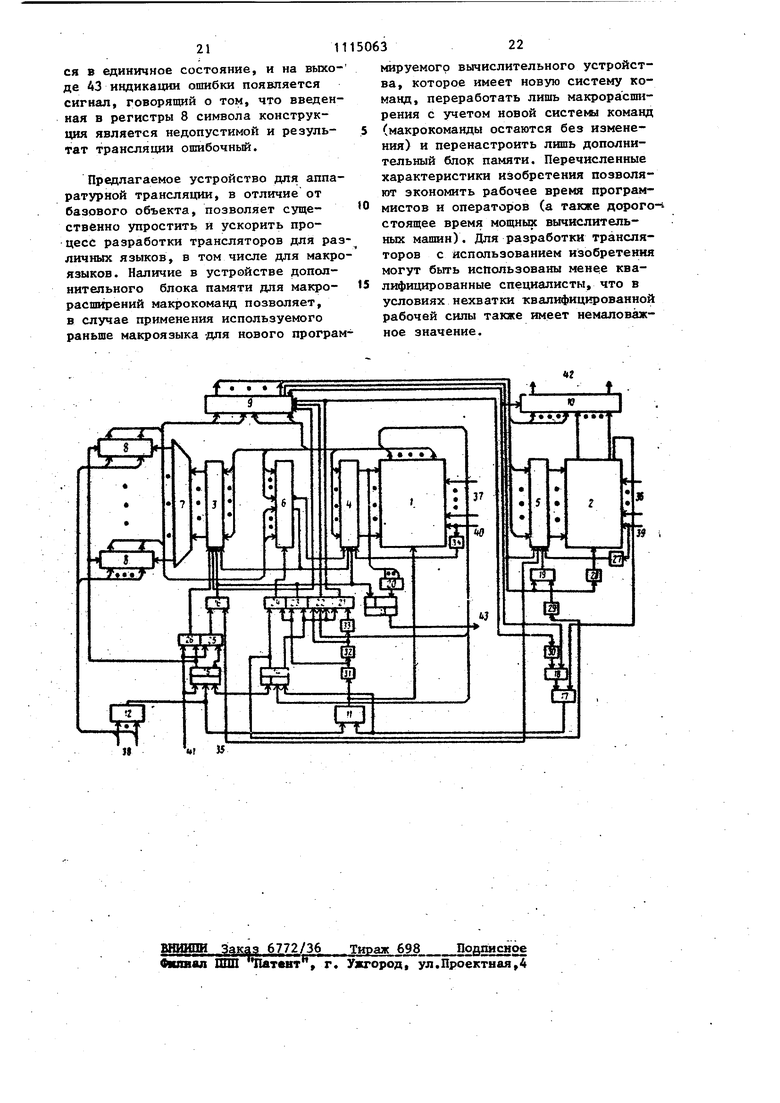

На чертеже изображена схема предлагаемого устройства.

Устройство содержит блоки 1 и 2 памяти, регист)ы 3-5 адреса, схему 7 6 сравнения, дешифратор 7, регистры 8 символов, регистр 9 вьщачи, переключатель,10, генератор 11 пря моугольных импульсов, дешифратор 12 кода пробела, триггеры 13-15, два элемента ИШ 16 и 17, элементы И 18-26, элементы 27-34 задержки. На схеме также обозначены вход 35 установки исходного состояния устройства, группы информационных вхо дов 36-38 устройства, входы 39-41 синхроимпульсов устройства, группа выходов 42 устройства, выход 43 индикации ошибки. Входы 36 и 37, 39 и 40 могут, например, подключаться к стандартному интерфейсу вычислительной машины типа 2К, к наборной клавиатур на пульте управления устройства ил к пишущей машинке типа Консул, вход 35 и выход 43 - соответственно к кнопке начальной установки и к световому индикатору на пульте управления устройства, выходы 42 к информационным входам внешнего для устройства блока памяти, хранящего двоичную программу на выход ном языке. Перед началом работы в блок 1 п мяти заносится информация, позволяющая установить взаимно однознач ное соответствие мехэду кодами вход ного и выходного языkoв. Для этого на основе анализа конструкций вход ного языка, представленных в симво лическом виде, строится древовидный граф, в узлах которого находятся отдельные символы алфавита входного языка, а связи между узлами (ветви графа) указывают на символы, являющиеся соседними в символическом коде конструкции. В конечных узлах графа (листьях) помещается двоичный код выходного языка, соответствующий одной из конструкций входного языка. Узел, имеющий исходящие ветви, является порождаюш11м, более одной исходящей ветви - ветвящимся. По графу соста ляются карты заполнения блоков 1 и памяти. Сцелью упрощения и упорядочени процесса решения данной задачи нео ходимо руководствоваться следующей методикой. 1. Если построение графа для выбранного языка программирования не проводилось, то идти к 2. Иначе 3В (требуется достройка графа дополнительно введенными конструкциями) идти к 2.9, 2. Строится граф для выбранного языка программирования следующим образом. 2.1.Строится начальный узел графа - к-орень. 2.2.Выбирается произвольная символическая конструкция входного языка. 2.3.Выбирается первый символ конструкции. 2.4.Граф достраивается узлом, который соединяется ветвью с последним из построенных узлов и имеет на единицу больший ранг. Идти к 2.6. 2.5.Производится достройка графа узлом, который соединяется ветвью с породившим последний из рассмотренных узлов, имеет тот же ранг, что и рассмотренный, и располагается справа от него. 2.6.Если построенный узел не является листом (листом узел является в том случае, если соответствующий ему символ является пробелом), то он помечается выбранным символом и выбирается следующий символ. Идти к 2.4. Иначе идти к 2.7.. 2.7.В лист записьгоается группа двоичных кодов (в частном случае один) конструкций выходного языка, являющихся двоичными эквивалентными рассмотренной конструкции входного языка. 2.8.Если рассмотрены все конструкции входного языка, то идти к 3. Иначе идти к 2.9. 2.9. Выбирается следующая конструкция входного языка. 2.10.Выбирается первый символ конструкции. 2.11.Выбирается узел нулевого ранга, если таких узлов несколько - то крайний левый. 2.12.Если символ конструкции совпадает с символом выбранного узла, идти к 2.13. Иначе идти к 2.15. 2.13.Выбирается следующий символ конструкции. 2.14.Выбирается крайний левый узел из порожденных рассмотренным узлом, являющийся листом. Идти к 2.12. Иначе идти к 2.5. 2.15.Если рассмотренный узел имеет справа узлы, порожденные 9 тем же узлом, что и он сам, выбирается соседний справа. Идти к 2.12. Иначе идти к 2.5. 3.Если предполагается организовать процесс трансляции с проведением частичного контроля входных конструкций на наличие недопустимых символических обозначений, идти к 7 . Если же необходим полный контроль, идти к 4. Для предварительной оценки объе ма требуемой памяти и времени тран ляции по графу можно воспользовать ся формулами, приведенными в конце методики. 4.Если основная численная разм ка графа не проводил;ась, идти к 5 В противном случае (проводилась достройка графа) идти к 4.1. 4.1.Выбирается узел из имеющих порояденные неразмеченные узлы, значение HI основной разметки которого наименьшее. 4.2.Переменной М присваивается значение основной разметки листа, находящегося в конце маршрута начинающегося узлом, порожденным узлом К1 и являющимся соседним с крайним левым из неразмеченных, порожденных тем же узлом. 4.3.Уничтожается основная разметка всех узлов, величины HI кото рых больше М. 4.4.Идти к 5.7. 5.Проводится основная разметка графа. 5.1.Узел нулевого ранга (если их несколько, то крайний левый) по мечается числом Н1-1 (корень дерева - нулем) . 5.2.Крайний певый узел из поро денных последним помеченным узлом помечается числом HI HI + 1. 5.3.Если помеченный узел не яв ляется листом, идти к 5.2. Иначе запоминается значение HI (Н HI) Идти к 5.4 5.4.Выбирается узел, помеченный числом Н1 Н1-1. 5.3 Если выбранный узел являет ся ветвящимся и имеет порожденные узлы, расположенные правее -узла HI + 1, то идти к 5.7. Иначе идти к 5.6. 5.6. Если выбранный узел помечен .дислом HI О, то идти к 6. И че идти к 5.7. 310 5.7.Выбирается крайний левый узел из неразмеченных, порожденных узлом HI. 5.8.Выбранный узел помечается числом HI HI + 1. Идти к 5.3. 6. Составляются основная и дополнительная карты памяти для случая сплошного контроля входных конструкций на наличие недопустимых символических обозначений. 6.1.Номера А и А1 строки карты памяти (т.е. адрес соответствующей ячейки памяти) основного и дополнительного блоков памяти соответственно принимаются равными нулю (А OJ А1 0). 6.2.Выбирается узел, помеченный номером HI 1. 6.3.Если символ выбранного узла имеет несколько двоичных эквивалентов, то выбирается строка А А-1 и значение третьего поля ее увеличивается на единицу. Идти к 6.8. Иначе идти к 6.4. 6.4. В первое поле строки А заносится код символа узла HI, например, в коде КОИ-7 (выбор кода определяется устройством ввода символических конструкций), если выбранный узел является листом - то код пробела. 6.5. Если узел HI порожден ветвящимся узлом и не является крайним правым среди порожденных этим узлом, то во второе поле заносится двоичный код величины А А, + (Н1„ - HI,) -Н Н.1л ,НЬ-, . где л, п - индексы, обозначающие принадлежность переменных соответственно узлу HI (левому) и соседнему справа от HeroJ - число узлов от HI л до П( 4и-А jj включительно, являющихся листьями. в противном случае во второе поле заносится код 1... 1 . 6.6. В том случае, если выбранный узел является листом, заполнение третьего поля произвольно, иначе в него заносится двоичное значение ранга на единицу большего ранга узла HI. 6.7. В четвертое поле записывается признак типа формата заполненной строки - нуль.

6.8.Если узел HI не лист, то выбирается узел Н1 HI + 1 и строка А А + 1. Идти к 6.3. Иначе идти к 6.9.

6.9.В случае, если записанный в листе код является-единственным, вдти к 6.15. Иначе идти к 6.10.

6.10.- В крайний .правый разряд первого поля строки А основного блока памяти заносится единица, в оставшиеся разряды - код числа А1.

6.11.Выбирается первый код макрорасширения, записанного в листе.

6.12.Если двоичный код макрорасширения является последним, то в крайний правый разряд строки А1 дополнительной карты памяти записывается единица, иначе - нуль. В остальные разряды заносится выбранный код макрорасширения.

6.13.Выбирается строка А А +

6.14.Если выбранный код макрорасширения не является- последним, следующий код считается выбранным. Идттл к 6.12. Иначе идти

к 6.16.

6.15.В первое поле строки А

А + 1 заносится выбранный двоичный код конструкции выходного языка. I

6.16.Второе поле предназначено для признака вставки: если в код конструкции выходного языка

не требуется вставлять код какоголибо символа -конструкции входного языка, то в поле записывается нулевой код, иначе -единичный.

6.17.Если признак вставки равен нулю, то в третье поле записывается произвольный код, иначе в него заносится двоичный код ранга узла, в котором находится вставляемый символ.

6.18.В четвертое поле записывается признак формата заполненной строки - единица.

6.19.Если при составлении карты использованы не все узлы -графа (HI Н1мд), выбирается узел HI НТ + 1 и строка А А+1. Идти .

к 6.3. Иначе идти к 10.

7. Если вспомогательная численная разметка графа не проводилась, то .идти .к 8, Иначе (проводилась достройка графа) идти к 7.1.

7,1. Выбираетс-й ветвящийся узел не имеющий порозвденные неразмеченные узлы, для которого наименьшим

является значение разметки Н2 сред узлов двух типов: крайнего левого из размеченных порожденных им и ближнего верхнего в направлении от упомянутого ветвящегося узла к корню дерева.

7.2.Уничтожается вспомогательная численная разметка всех узлов от Н2 + 1 до ,. включительно.

7.3.В первом случае (а также если ветвящийся узел относится одновременно к узлам двух .типов) идти к 8.5. Иначе выбрать узел Н2 и идти к 8.2.

8.Вьшолняется вспомогательная численная разметка графа.

8.1.Узел нулевого ранга (если их несколько, то крайний левый) помечается числом HI 1 (корень дерева - нулем).

8.2.Выбирается крайний левый узел из порожденных выбранным ранее.

I- 8.3.Если узел, породивший выбранный, является ветвящимся, выбранный узел помечается числом .

8.4.Если выбранный узел не является листом, то идти к 8,2. Инач идти .к 8.5.

8.5.Выбирается узел Н2. Запоминается значение его разметки

(Н Н2). I

8.6.Если выбранный узел имеет справа от себя непомеченные узлы, порожденные тем же узлом, что и он сам, то крайний левый из них помечается номером Н2 - И + 1. Идти к 8.4. Иначе.идти к 8.7.

8.7.Выбирается узел Н2 Н2-1.

8.8.Если Н2з О, идти к 8.6. Инче идти к 9.

9.Строятся основная и дополнительная карты памяти для случая организации процесса трансляции с частичным контролем входных констрций на наличие недопустимых символческих обозначений.

9.1,Номер строки основной и дополнительной карт памяти принимается равным нулю (А OJ А1 0).

9.2,Выбирается узел, помеченны номером Н2 1.

9.3,В первое по.ле строки А зап1ис:ывается код символа узла Н2, если узел Н2 является листом - то код пробела.

1311

9.4. Если выбранный узел не имеет справа от себя узлов, порожденных тем же ветвящимся, что и выбранный, то во второе поле заносится код 1 ... 1 . Иначе в него записывается двоичный код числа, определяемого по формуле

АП АД+ 1 -н (Н2р- Н2д) +

(2)

+ К.

Н2,Н2п.т где л, п - индексы, обозначающие

принадлежность переменных соответственно левому и правому узлу из рассматриваемой пары узлов;

К - количество листьев, положенных в конце всех маршрутов, проходящих через узлы от Н2д до Н2, включительно, но не проходящих через узл со значениями разметки, большими Н2п-1 .

9.5.Заполнение третьего поля произвольно, если ранг узла Н2+1 не превьшает ранга узла И 2, иначе в него записывается двоичный код ранга узла Н2 + 1.

9.6.Четвертое поле предназначено для записи признака типа формата заполнения строки - О.

9.7.Если ранг узла Н2 + 1 больше ранга узла Н2, выстирается узел Н2 Н2 + 1 и строка А А + 1. Идти к 8.3. Иначе идти к 9.8.

9.8.В случае, если записанный в листе код является единственным. Идти к 9.14. Иначе идти к 9.9.

9.9.В крайний правый разряд первого поля строки А основного блока памяти заносится единица, в оставшиеся разряды - код числа А1.

9.10.Выбирается первый код макрорасширения, записанный в листе.

9.11.Если двоичный код макрорасширения является последним, в крайний правый разряд строки А1 дополнительной карты памяти записывается единица, иначе - нуль. В остальные разряды заносится выбранный код макрорасширения.

9.12.Выбирается строка А1 А1+

9.13.Если выбранный код макрорасширения не является последним, выбирается следующий код макрорасширения. Идти к 9.11. Иначе идти

к 9.15.

506314

9.14.В первое поле строки А А+1 заносится выбранный двоичный код конструкции выходного языка.

9.15.Второе поле предназначено 5 для признака вставки: если в код

конструкции выходного языка не требуется вставлять код какого-либо символа конструкции входного языка, то в поле записывается нулевой код, иначе - единичный.

9.16.Если признак вставки равен нулю, в третье поле записывается произвольный код, иначе в него за,писывается .двоичньй код ранга узла,

в котором находится вставляемый символ.

9.17.В четвертое поле записывается признак формата заполненной строки - единица.

9.18.Если при составлении карты использованы не все узлы графа (Н2 / ), выбирается узел Н2 Н2 + 1 и строка А А+1. Идти

к 9.3. Иначе идти к 10.

10. Конец.

Оценка объема занимаемой памяти и времени трансляции по графу производится следующим образом:

ЕОо

(3) Ъ Кд

(4)

ЕДз,

К

АУ1

памяти в ячейках основного (дополнительного) блока памяти

максимальное знаИчение разметки графа;

количество лис1;ьев графа;

количество кодов макрорасш фения, записанных в 1-м листе;

время трансляции конструкции, длительность такта устройства генератора HMfiyJIbCOB. (|АКС значение разметки узлов графа, в ко торых записаны символы рассматри ваемой конструкции (максимальное значение) , количество кодов макрорасширения в лист.е конструкции количество узлов располо енных левее узлов, имеющи разметку Н , и имеющих тот же по рождающий узел, среднее время тра сляции конструкции при разных частотах использования отдельны конструкций, время трансляции программы, количество конструкций в программе, длительность так та ввода символа в устройство; количество симво лов в коде 1-й K конструкции вход ного языка. Приведенные формулы имеют одина ковый вид для обоих вариантов составления карты памяти. При выборе конкретного варианта переменная Н заменяется на соответствующую пере менную HI или Н2. В рассматриваемом устройстве в случаях совпадения двоичного кода символа входного языка из группы регистров 8 символа с двоичным кодом символа с выхода блока 1 памяти, поступаюпщх на входы схемы 6 сравнения, устанавливается новое значение номера регистра символа, ука;занное в третьем поле ячейки па мяти, адрес перехода в блоке 1 пам ти на единицу больше предьщущего. В случае же несовпадения номер регистра символа остается без изме нений, а адрес перехода совпадает со значением второго поля ячейки памяти. Это позволяет после перебора всех допустимых значений содер жимого анализируемого регистра сим вола выполнить переход яа некоторый фиксированный адрес, появление кода которого на выходе регистра 4 адреса свидетельствует о наличии запрещенной комбинации в группе регистров 8 символа, В устройстве в качестве такого адреса выбран адрес последней ячейки памяти, распознаваемый элементом И 20 (код адреса 1. ..1). Устройство работает следующим образом. При включении устройства на вход 35 подается сигнал, устанавливающий триггеры 14 и 15 и регистр 5 адреса в нулевое состояние и поступающий через элемент ИЛИ 16 для установки в нуль регистра 4 адреса . Затем производится запись информации в блок 1 памяти. Ка информационные входы 37 устройства поступает первое слово для записи в нулевую ячейку памяти, адрес которой установлен в регистре 4 адреса. Сопровождающий данное слово синхроимпульс по входу 40 поступает на вход элемента 34 задержки и на вход управления записью в блок 1 памяти, в результате чего происходит прием слова в соответствующую ячейку памяти. После этого на счетном входе регистра 4 адреса появляется сигнал, прошедший через элемент 34 задержки, и значение адреса увеличивается на единицу. В следующем такте поступает очередное слово по- входам 37 и сопровождающий-его синхроимпульс по входу 40. Запись данного слова в блок 1 памяти и увеличение значения адреса в регистре 4 адреса выполняется также, как и в предыдущем такте. Аналогичным образом вьшолняется заполнение блока памяти кодами макрорасширений макрокоманд с входов 36, сопровождающий каждый код синхросигнал поступает по входу 39 на вход управления записью блока 2 памяти и через элемент 27 задержки на счетный вход регистра 5 адреса. Этот процесс продолжается до заполнения блоков 1 и 2 памяти, после чего устройство считается подготовленным к работе. Если блок 1 памяти выполнен не в виде программируемого, а в виде постоянного запоминающего устройства, подготовка устройства к работе заключается в установке двух пла из некоторого набора плат, каждая пара из которых ориентирована на определенную пару входного и выходного языков, и в подачь сигнала начальной установки на вход 35 для установки в нуль триггеров 14 и 15 и регистра 4 адреса аналогично описанному. В режиме записи конструкции вход ного языка в регистры 8 символа с входов 38 последовательно друг за другом поступают символы конструкции входного языка, а по входу 41 - сопровождающие их синхроимпульсы. По первому синхроимпульсу происходит запись символа в первый регистр 8 символа следующим образом. Так как на инверсном выходе триггера 15 .единица, то первый cинxpoи fflyльc через элемент К 25 и элемент ИЛИ 16 проходит для установки в пуль регистров 3 и 4 адреса и регистра 15. Этот же синхроимпульс поступает на единичный вход триггера 15. К момен ту появления импульса на выходе дешифратора 4 триггер 15 переключае ся в единичноесостояние и на входах выбора приема-выдачи регистров 8 символа с выхода триггера 15 устанавливается режим приема кода. Таким образом, запись первого символа в первый регистр 8 символа выполнена. Второй синхроимпульс с входа 41 проходит уже через эпемент И 26, так как триггер 15 находится в еди ничном состоянии, и поступает на счетный вход регистра 3 адреса. В результате этого (появляется сиг. нал на управляющем входе одного из регистров 8 символа с соответствующего выхода дещифратора 4) прои водится запись кода очередного символа в следующий регистр 8 символа Все поступающие символы обрабатываются аналогичнь1м образом до тех пор, пока не поступит код пробела. По коду пробела на выходе дешифратора 12 появляется сигнал, переводящий триггер 15 в инверсное состояние, что меняет уровень напряжения на входах выбора приема-вьщачи регистров 8 символа, и производящий запуск генератора 11 прямоуголь ных импульсов. Синхрои1«1ульс с входа 41, поступивший с символом Пробел, проходит через элемент И 25 1 318 и элемент ШБ1 16 и устаиапливает в нуль регистр 3 адреса. На этом режим приема конструкщти входного языка заканчивается. В режиме трансляции по сигналу с генератора 11 прямоугольных импульсов считывается информация из блока 1 памяти. Кроме того, через элемент 31 задержки и элемент И 24 (так как триггер 14 в единичном состоянии на инверсном выходе) он поступает на управляющий вход схемы 6 сравнения, в результате чего сравниваются коды с выходов блока 1 памяти и с выходов регистра 8 символа, адрес которого установлен в регистре 3 адреса. При их совпадении появляется сигнал на выходе схемы 6 сравнения, что приводит к увеличению адреса блока 1 памяти в регистре 4 адреса на единицу и к приему в регистр 3 с выходов блока 1 памяти адреса следующего символа. По следующему синхроимпульсу с выхода генератора 11, если коды на входах схемы 6 сравнения совпадают, в устройстве ВЫПОЛНЯК1ТСЯ те же действия. В случае несовпадения кодов символов на схеме 6 сравнения сигнал появляется не на прямом выходе, а на инверсном. Поэтому значение регистра 3 адреса не меняется, а в регистр 4 адреса принимается адрес перехода в блоке 1 памяти. Режим трансляции продолжается до тех пор, пока при считывании информации из блока 1 памяти на выходе условий, соединенном с входом триггера 14 (четвертое поле ячейки - см. методику) не появится единица, переводящая триггер в единичное состояние на прямом выходе, Высокий уровень напряжения с прямого выхода триггера 14 открывает стробирующие входы элементов И 21-23. В результате этого сигнал с выхода элемента 31 задержки пройдет через элемент И 23 и на вход управления приемом с первой группы входов регистра 9 выдачи, и двоичный код конструкции выходного языка (либо начальный адрес макрорасширения в блоке 2 памяти) принимается в регистр вьщачи. Этот же сигнал приведет к приему в регистр 3 адреса номера вставляемого символа, код которого вьщается с соответствующего регистра 8 символа на вторую группу входов регистра 9 выдачи. Ее19

ли на выходе условий блока 1 памяти соединенном с входом элемента И 22 (признак вставки - второе поле ячейки памяти), - единица, сигнал с выхода элемента 32 задержкипроходит на вход управления приемом с второй группы входов регистра 9 выдачи, и код вставляемого символа принимается в регистр вьщачи. Затем сигнал с выхода элемента 26 задержки проходит через элемент И 21, на другом входе которого присутствует единица с прямого выхода триггера 14, на вход управления вьщачей регистра 9 вьщачи,

Двоичный код (кроме младшего разряда), записанный в регистре 9 вьздачи и выданный из него по сигналу с выхода элемента И 22, поступает на входы переключателя 10 и регистра 5 адреса.

Если в крайнем правом разряде регистра 9 выдачи записан нуль, то высокий уровень напряжения с инверсного выхода разряда поступает на вход элемента И 18 и на управляющий вход переключателя 10, в результате чего на выходы 42 устройства с выходов регистра 9 вьщается двоичный код конструкции выходного языка К моменту поступления сигнала с инверсного выхода младшего разряда регистра 9 выдачи на один из входов элемента И 18 на его другой вход: через элемент 30 задержки поступает сигнал с выхода элемента И 21, по которому был выдан код из регистра 9 вьздачй. В результате этого с выхода элемента И 18 через элемент ИЛИ 17 на вход генератора 11 прямоугольных импульсов поступает логическая единица, приводящая к его остановке. Эта же единица поступает на вх;од триггера 14, переводит его в единичное состояние на инверсном выходе и тем самЬ1м подготавливает устройство к обработке следующей конструкции входного языка. На этом режим вьщачи заканчивается.

Если же в мпадщем разряде регистра 9 вьщачи записана единица, то с прямого выхода данного разряда она поступает на вход элемента 28 задержки и элемента И 19, на другом входе которого еще сохраняется высокий уровень напряжения с выхода элемента 29 задержки. Появление

506320

единицы на выходе элемента И 19 приводит к приему в регистр 5 адреса с выходов регистра 9 вьздачй начального адреса макрорасширения транс5 лируемой макрокоманды. После -этого с выхода элемента 28 задержки поступает сигнал на вход управления считыванием блока 2 памяти, и с его выходов двоичный код первой конструк

10 ции макрорасширения вьщается через переключатель 10 на выходы 42 уст ройства, так как на управляющем входе переключателя нуль с инверсного выхода мпадшего разряда регист15 ра 9 вьщачи.

Следующий импульс с выхода генератора 11 прямоугольных импульсов аналогично ранее описанному приводит к выдаче кода из той же ячей0 ки блока 1 памяти и записи его в регистр 9. Значение младшего разряда кода также поступает на счетный вход регистра 5 адреса, вход элемента 28 задержки и вход элемента

5 И 19. Поскольку на другом входе

элемента И 19 к этому времени низкий уровень напряжения, поступающего с выхода элемента 29 задержки (из-за переключения триггера 14

0 в нуль на инверсном выходе), на вход управления приемом регистра адреса сигнал не поступает. Содержимое регистра 5 адреса увеличивается сигналом, поступившим на его

5 счетный вход. Затем с выхода элемента 28 задержки на вход управления считыванием поступает сигнал, по которому очередная двоичная конструкция выходного языка вьщает0 ся на выходы 42 через переключатель 10.

Описанные действия повторяются до тех пор, пока из младшего разряда блока 2 памяти не вьщается еди5 ница, что соответствует последнему коду макрорасширения. Данная единица, пройдя чере элемент ИЛИ 17, останавливает генератор 11 прямоугольных импульсов и переводит

0 триггер 14 в единичное состояниена инверсном выходе. Таким образом, трансляция макрокоманды закончена и устройство может приступать к приему и трансляции следующей консS трукции.

Если в процессе трансляции с выхода регистра 4 адреса появляется код 1... 1, элемент И 20 цереключает11

21

ся в единичное состояние, и на выхода 43 индикации ошибки появляется сигнал, говорящий о том, что введенная в регистры 8 символа конструкция является недопустимой и результат трансляции ошибочный.

Предлагаемое устройство для аппаратурной трансляции, в отличие от базового объекта, позволяет существенно упростить И ускорить процесс разработки трансляторов для различных языков, в том числе для макроязыков. Наличие в устройстве дополнительного блока памяти для макрорасширений макрокоманд позволяет, в случае применения используемого раньше макроязыка -для нового програм

506322

мируемого вычислительного устройства, которое имеет новую систему команд, переработать лишь макрорасш рения с учетом новой систеьы команд 5 (макрокоманды остаются без изменения) и перенастроить лишь дополнительный блок памяти. Перечисленные характеристики изобретения позволяют экономить рабочее время програм0 мистов и операторов (а также дорого-i стоящее время мощных вычислительных машин). Для разработки трансляторов с использованием изобретения могут быть использованы ква15 лифицированные специалисты, что в условиях нехватки квалифицированной рабочей силы также имеет немаловажное значение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для аппаратурной трансляции | 1982 |

|

SU1056210A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1137481A2 |

| Система для трансляции с проблемноориентированного языка | 1976 |

|

SU674028A1 |

| Устройство для преобразования языков | 1983 |

|

SU1111176A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Транслятор языков программирования | 1981 |

|

SU1387018A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

УСТРОЙСТВО ШШ АППАРАТУРНОЙ ТРАНСЛЯЦИИ, содержащее семь элементов И, первый элемент ИЛИ, регистры символа, регистр выдачи, схему сравнения, два регистра адреса, дешифратор кода пробела, три , генератор прямоугольных импульсов, четыре элемента задержки, дешифратор и первый блок памяти, вход записи, информационные входы и информационные выходы которого подключены соответственно к первому входу синхроимпульсов устройства, к первой группе информационных входов устройства и к первой группе информационных входов регистра вьщачи, вторая группа информационных входов которого соединена с выходами разрядов регистров символа, информационные входы которьк подключены к второй группе информационных входов устройства, входы и выходы дешифратора соединены соответственно с выходами разрядов первого регистра адреса и с управляющими входами записи регистров символа, выходы разрядов которых подключены к первой группе информационных входов схемы сравнения, вторая группа информационных входов которой соединена с информационными выходами первого блока памяти, информационные входы первого -и второго регистров адреса подключены к информационным выходам первого .блока памяти, адресные входы которого соединены с выходами разрядов второго регистра адреса, вторая группа информационных входов устройстваподключена к входам дешифратора кода пробела, выход которого соединен с установочным входом первого триггера и с управляюпщм входом запуска генератора прямоугольных импульсов, выход которого подключен к управляющему входу считывания первого блока памяти и через первый элемент задержки - к входу второго элемента задержки и к первым входам первого и второго элементов И, выход первого элеменУ1 та И соединен с первыми управляющими входами приема первого регистра 9 адреса и регистра вьщачи, выход вто&э рого элемента И подключен к управляющему входу схеьал сравнения, первый выход которой соединен с вторым управляющим входом приема первого регистра адреса и с первым счетным входом второго регистра адреса, вход установки исходного состояния устройства подключен к установочным входам исходного состояния первого и второго триггеров и к первому входу первого элемента ШШ, второй вход синхроимпульсов устройства соединен с единичным входом первого

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3500457/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-23—Публикация

1983-05-05—Подача