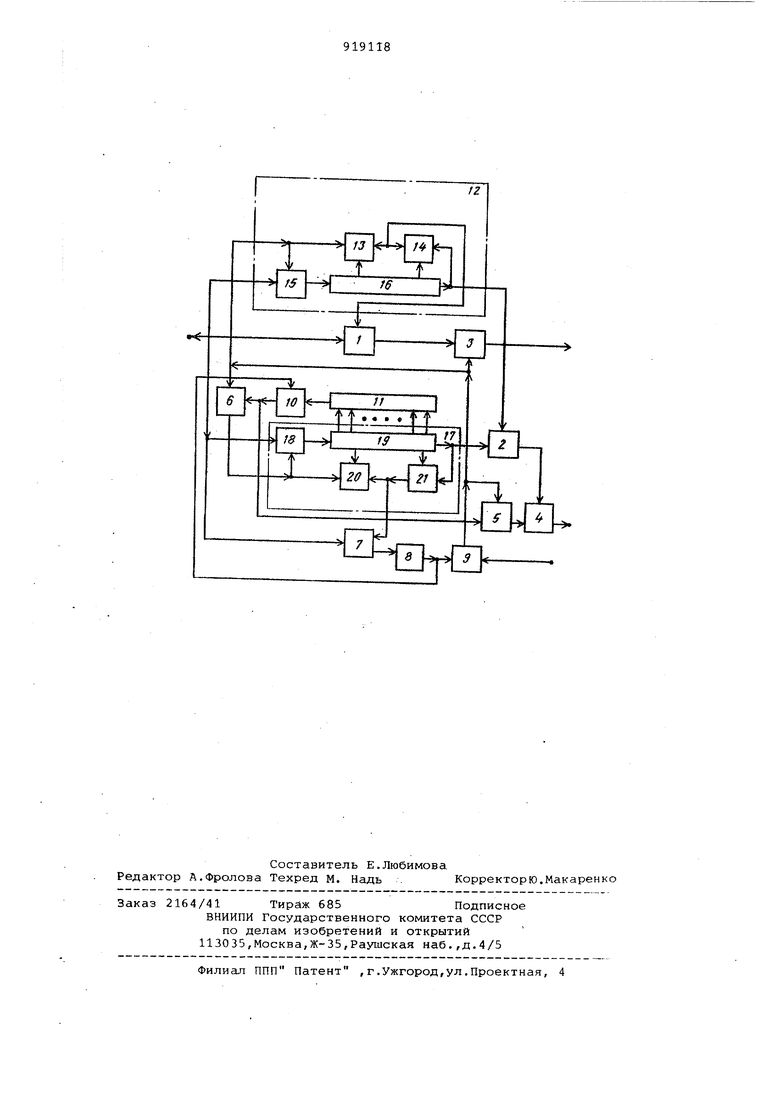

Изобретение относится к радиотех нике и может использоваться для размеров и контроля параметров дискретного канала связи. Известно устройство для определения достоверности контрольной двоичн информации, содержащее последователь но соединение первый сумматор и первый выходной клапан, последовательно соединенные второй сумматор и вто рой выходной клапан, последовательно соединенные счетчик и входной триггер, выход которого подключен к упра ляющему входу первого выходного клапана, первый формирователь контрольной последовательности, первый выход которого подключен к одному из входов первого сумматора, и второй формирователь контрольной последовательности, первый выход которого под ключен к одному из входов второго сумматора, другой вход которого соединен со вторым выходом первого формирователя контрольной последователь Однако в известном устройстве для определения достоверности контрольной двоичной информации требуется значительное время. Цель изобретения - сокращение времени определения достоверности. Поставленная цель достигается тем, что в известное устройство введены третий сумгиатор, первый элемент ИЛИ и последовательно соединенные анализатор, дополнительный триггер и второй элемент ИЛИ, при этом второй выход второго формирователя контрольной последовательности подключен к второму из входов третьего сумматора, выход которого подключен к входу счетчика, выход которого подключен к другому -входу дополнительного триггера, выход которого подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом входного триггера, с первым входом первого формирователя контрольной последовательности и с другим входом второго элегиента ИЛИ, выход которого подключен к первому входу второго формирователя контрольной последовательности, рлзряд 1ые выходы которого подключены к входам анализатора, а второй вход соединен с другими входами первого и третьего сумматоров и со вторым входом первого формирователя контрольной последовательности, а выход первого элемента ИЛИ подключен к другому входу второ выходного клапана. При этом каждый формирователь ко рольной последовательности содержит последовательно соединенные входной элемент совпадения, выходной управляемый регистр, выходной сумматор и входной клапан, выход которого подключен к другому входу выходного уп равляемого регистра, дополнительный выход которого подключен к другому входу выходного сумматора, а другой вход входнгго клапана соединен с соответствующим входом входного эле мента совпадения. На чертеже представлена структур ная электрическая схема предлагаемо го устройства. Устройство для определения досто верности контрольной двоичной инфор мации содержит первый и второй сумматоры 1 и 2 , первый и второй выходные клапаны 3 и 4, первый и второй элементы ИЛИ 5 и б, третий сумм тор 7, счетчик 8, входной триггер 9 дополнительный триггер 10, анализатор 11, первый формирователь 12 кон рольной последовательности, состоящий из входного клапана 13, выходного сумматора 14, входного элемента 15 совпадение и выходного управл емого регистра 16, второй формирова тель 17 контрольной последовательности, состоящий из входного элемен та 18 совпадения, выходного управляемого регистра 19, входного клапана 20 и выходного сумматора 21. Устройство работает следующим об разом. Перед сеансом замера параметров канала связи входной триггер 9 со входа устройства устанавливается в единичное состояние, закрывая первый выходной клапан 3 и через первый элемент ИЛИ 5 второй выходной клапан 4, а также как управляющий сигнал поступает на вхсэд первого формирователя 12 и через второй элемент ИЛИ 6 на в.ход второго формирователя 17, устанавливая их в режим приема синхросигнала и разрешая режим формирования контрольных Лоследовательностей. Сигналы управления закрывают цеп прохождения сигналов обратной связи выходных управляемых регистров 16 и 19 через выходные сумматоры 14и 21 на входных клапанах 13 и 20 и открывает через входные элементы 15и 18 совпадения цепи прохождения сигналов со входа устройства (из канала связи) на заполнение выходны управляемых регистров 16 и 19. На втором формирователе 17 начинается пооцесс проверки последовательности поступающей из канала связи на ее соответствие выбранному закону формирования комбинаций. Сигналы с выходного сумматора 21 поступают на вход третьего сумматора 7, на другой вход которого поступают символы из канала связи иепосредственно. При наличии факта передачи комбинаций в канале связи и отсутствии помех в канале связи с выхода третьего сумматора 7 будет поступать нулевая последовательность. При достижении определенного порога, который определяется диапазоном просчета подряд принятых нулевых символов счетчиков 8, на его выходе проявляется сигнал, поданный к установочным входам входного и дополнительного . триггеров 9 и 10. В результате этого открываются первый и второй выходные клапаны 3 и 4, а первый и второй формирователи 12 и 17 переключаются из режима синхронизации в режим ге-. нерирования контрольных последовательностей. Первый и второй формирователи 12 и 17 работают синхронно, последовательности сигналов, поступающие на входы второго сумматора 2 полностью совпадают, и через открытый второй выходной клапан 4 на выход устройства поступает нулевая последовательность, характеризующая нор.мальный режим работ. Одновременно с этим через открытый первый выходной клапан 3 с первого сумматора 1 на выход устройства поступает поток ошибок. Он образуется путем позначного сравнения последовательности, формируемой первым формирователем 12 и последовательности, поступающей из канала связи. Так как после фазирования эти последовательности совплляют, то пои отсутствии помех в канале связи с первого сумматора 1 поступают нули. Наличие искажения приводит к несоответствию последовательностей и приводит к появлению единиц на выходе первого сумматора 1, что и является потоком ошибок. Через определенное время сработает анализатор 11, настроенный на определенную комбинацию сигналов, формируемых на регистре 19. По этому сигналу дополнительный триггер 10 устанавливается в единичное состояние, закрывает через первый элемент ИЛИ 5 второй выходной клапан 4 и переключает второй формирователь 17 из режима формирования контрольной последовательности в режим синхронизации. После этого второй формирователь 17 работает в, режиме синхронизации, как это было описано при первоначальном включении в связь. При этом первый формирователь 12 продолжает работать в режиме формирования контрольной последовательности, продолжая режим замера ошибо После выделения порога срабатывания управляющий сигнал со счетчика 8 вновь переключает дополнительный триггер 10 в положение, когда второй формирователь 13 вновь устан ливается в режим генерирования конт рольной последовательности, с одновременным открыванием цепи проверки синфазности через второй выходной клапан 4. После пересинхронизации второго (формирователя 17 его фазовое положе ние будет синхронным с фазовьш поло жением канальной последоватльности. В случае, если за цикл прибор расфазирован не был,это фазо вое положение с.оответствует фазовом положению первого формирователя 12, что фиксируется нулевой последевательностью, выдаваемой со второго сумматора 2 через второй выходной клапан 4 потребителю. В случае сбоев прибора в цикле з мера эти последовательности не совпадают и на выход устройства поступают единицы, свидетельствующие о необходимости стирания потока ошибо за последний цикл замера. Поскольку сигналы с анализатора поступают периодически, то с таким же периодом производится переключение второго формирователя 17 из режима генерирования контрольных последовательностей в режим синхронизации. Таким образом, в режиме синхронизации одновременно ведется замер параметров канала связи независимо от времени синхронизации второго формирователя 17, за счет чего объем на,бираемых статистических параметров канала связи за один и тот же интервал времени существенно возратает, что и предопределяет в конечном итоге сокращение времени определения достоверности. Формула изобретения 1. Устройство для определения дос товерности контрольной двоичной информации, содержащее последовательно соединенные первый сумматор и пер вый выходной клапан, последовательно соединенные второй сумматор и второй выходной клапан, последовательно соединенные счетчик и входной триггер, выход которого подключен к упра ляющему входу первого выходного клапана, первый формирователь контроль-, ной Последовательности, первый выход которого подключен к одному из входов первого сумматора, и второй формирователь контрольной последовательности, первый выход которого подключен к одному из входов второго сумматора, другой вход которого соединен со вторым выходом первого формирователя контрольной последовательности, отличающееся тем, что, с целью сокращения времени определения достоверности, введены третий сумматор, первый элемент ИЛИ и последовательно соединенные анализатор, дополнительный триггер и второй элемент ИЛИ, при этом второй выход второго формирователя контрольной последовательности подключен к одному из входов третьего сумматора, выход . которого подключен к входу счетчика, выход которого подключен к другому входу дополнительного триггера, выход которого подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выход сим входного триггера, с перввлм входом первого формирователя контрольной последовательности и с другим входом второго элемента ИЛИ, выход которого подключен к первому входу второго формирователя контрольной последовательности, разрядные выходы которого подключены к входам анализатора, а второй вход соединен с другими входами первого и третьего сумматоров и со вторым входом первого формирователя контрольной последовательности, а выход первого элемента ИЛИ подключен к другому входу второго выходного клапана. 2. Устройство по п.1, отличающее с я тем, что каждый формирователь контрольной последовательности содержит последовательно соединенные входной элемент совпадения, выходной управляемый регистр,выходной сумматор и входной клапан, выход которого подключен к другому входу выходного управляемого регистра, дополнительный выход которого подключен к другому входу выходного сумматора, а другой вход входного клапана соединен с соответствующим входом входного элемента совпацения. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 440044, кл. Н 04 L 1/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема рекуррентного сигнала фазового пуска | 1979 |

|

SU873443A1 |

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU726560A1 |

| Устройство синхронизации М-последовательности | 1989 |

|

SU1748274A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

Авторы

Даты

1982-04-07—Публикация

1979-10-10—Подача