(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ.СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретных сигналов | 1978 |

|

SU746668A2 |

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU720465A2 |

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU726561A2 |

| Устройство для передачи и приема дискретных сигналов | 1975 |

|

SU557403A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1436276A1 |

| Устройство для защиты от ошибок в системе передачи с решающей обратной связью | 1976 |

|

SU728153A1 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство кодирования блоков информации | 1990 |

|

SU1785084A1 |

Изобретение относится к устройствам передачи и приема дискретнЕлх сиг налов, используемых на дуплексных каналах связи в условиях воздействия помех. Известно устройство 1 для nepe- дачи и приема длскретных сигналов, используемое на дуплексных каналах связи с различной величиной запаздывания в прохождении по ним сигналов для повышения достоверности передачи информации в условиях воздействия канальных помех. В известном устройстве канал обратной связи используется для передачи сигналов запроса или квитанции о принятых кодовых комбинациях, что сни :жает скорость передачи информации. Наиболее близким по технической сущности к изобретению является устройство 2 для передачи и приема дискретных сигналов, содержащее первый переключатель, выход которого подключен ко входу кодирукадего блока и через первый накопитель-повторитель к первому входу первого переключателя. Первый выходйодирующего блока соединен с первым входом первого блока сло жения, второй выход - со входом второго элемента задержки, выходы которого соединены с первыми входами соответствующих блоков сравнения. Выход второго блока сложения подключен ко вторым входам блоков сравнения, выходы которых подключены ко входам соответствующих регистров и к первым входам соответствующих элементов управления. Выходы регистров соединены со входами блоков памяти, выходы которых подключены ко вторым, входам сос)тветствующих элементов управления, выходы которых соединены с первыми входами элемента памяти, первого счетчика и, с первыми выходами декодирующего блока и элемента памяти. Первый выход,первого счетчика подклю Чен к третьему входу первого переключателя, второй выход - к первому входу второго накопителя-повторителя, ;ко второму входу которого прдключен второй выход декодирукяцего блока. Третий выход счетчика соединен со вторьм входс 4 элемента памяти, а третий выход декодирукяпего блока - со вторым входсМ второго блока сложения. Выход первого блока сложения подключен к первому выходу устройства, выхсзд второго накопителя-повторителя -

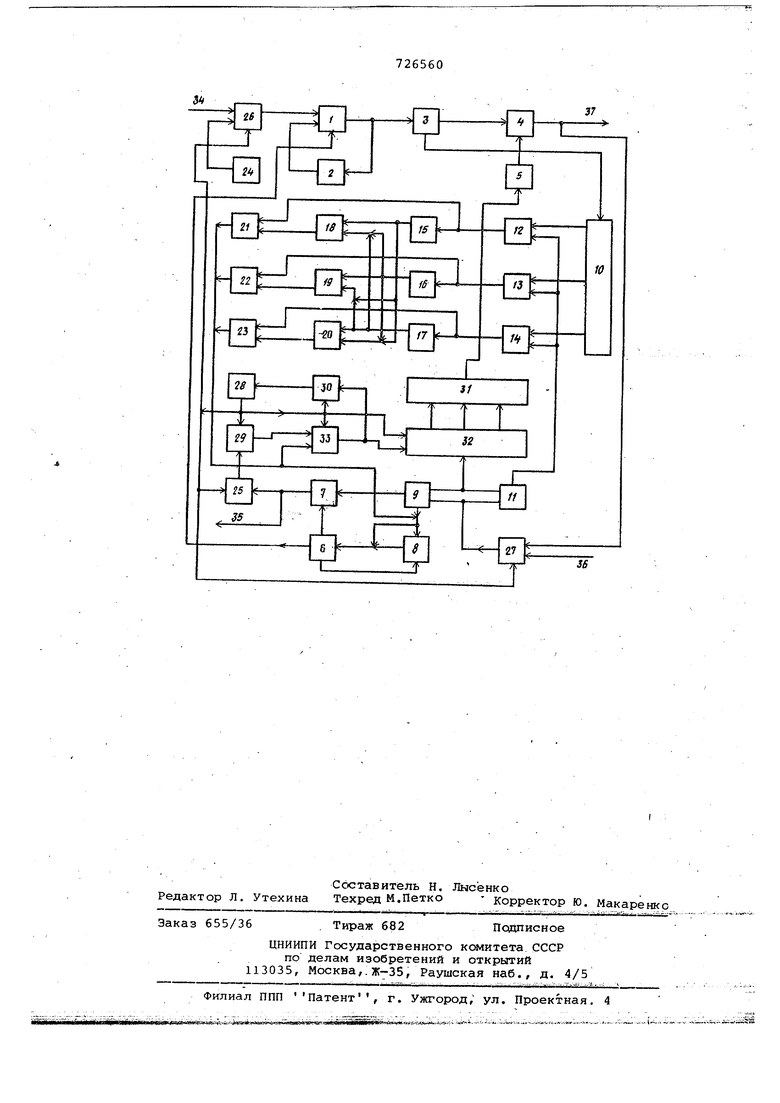

726560 o второму выходу устройства, а выход lepBorb блока задержки - ко второму входу первого блока сложения. Недостатком известного устройства яШГяГётея отсутствие контроля исправности функциональных блоков и узлов, что снижает надежность устройства. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что Ь предложенное устройство введены второй и третий переключатели, вто рой и третий счетчики, блок управления, да тчик, анализатор, триггер, ком мутатор и третий элемент задержки. Вы ход датчика подключен к первому вхо,-, ДУ второго переключателя, второй вход которого соединен с первым входом уст ройства, а выход - со вторым входом пертзого переключателя. Выход блока уПравления подключен к третьему входу второго переключателя, к первым входам второго и третьего счетчиков, к первому входу триггера, к первому входу коммутатора, к первым входам анализатора и третьего переключателя, второй вход которого с.оединен с выходом первого блока сложения, а третий вход - Кб вторым входам устройства. Выход третьего переключателя соединен с первыми входам декодирующего блока и второго блока слОжёния. Выход второго накрпителя-повторйтёля-подключен ко второму входу анализатора, выход которого соединен СО вторым входом второго счетчика. Вы ходы элементов управления подключены ко второму входу триггера, третий вход которого соединен с выходом вто рого счетч;ика. Выход триггера подклю qSinrO BTopOMy входу коммутаторами ко второму входу третьего счетчика, выход которого соединен со иходом блока управления. Третий выход декодиру ющего блока подключен к третьему вхо ду коммутатора. Выходы последнего со единены с соответствукщими входами третьего элемента задержки, выход ко торого подключен ко второму входу пе вЬУОэлемента задерж1си. Структурная схема устройства показана на чертеже. . Устройство содержит первый переключатель 1, первый накопитель-повто ритель 2, кодирующий блок 3, первый блок- сложения 4, первый элемент задержки 5, первый счетчик 6, второй накопитель-повторитель 7, элемент па мязгд 8, декодирующий блок 9, второй элемент задержки 10, второй блок сло жения 11, блоки сравнения 12-14, резгистры 15-17, блоки памяти 18-20, элементы управления 21-23, датчик 24 анализатор 25 контрольной последовательности сигналов, второй 26 и третий 27 переключатели, блок управления 28, второй 29 и третий 30 счетчики, третий элемент, задержки 31, ко мутатор 32 и триггер 33, первый вход

4 4, второй выход 35, второй вход 36, ервый выход 37. Устройство работает следующим обазом . Блок управления 28 сигналами со воих выходов определяет два режима аботы устройства: рабочий режим - пеедача и прием информационных сигнаов по каналам связи, i;i контрольный ежим - передача и анализ на приеме онтрольной последовательности сигалов .. , В рабочем режиме сигналы с выхоа блока управления 28 устанавливают ереключатели 26 и 27 и коммутатор 32 в положения, обеспечивающие подлючение соответственно первого (инор ационного) входа 34 .устройства к ервому входу переключателя 1, второо (канального) входа 36 устройства о входу декодирующего блока 9 и перому входу блока сложения 11, второ- го выхода декодирующего блока 9 ко входу элемента задержки 5 через коммутатор 32 и элемент 31 без внесения дополнительного запаздьшания при прохождении сигналов по этому тракту. В этом режиме работа предложенного устройства аналогична работе известного устройства.- . При переходе в контрольный режим по сигналам с выхода блока управления 28 устанавливается в исходное положение триггер 33, счетчики 29, 30, изменяется положение переключателей 26, 27 и подключается анализатор 25 для анализа сигналов с в&хода накопителяповторителя. 7. Сигналы контрольной последовательности с выхода датчика 24 через переключатели 26 и 1 поступают в кодируквдий блок 3 и накопительповторитель 2. В блоке 3 поступившие сигналы преобразуются в комбинации избыточного кода. Затем сигналы кодовой комбинации с выхода блока 3 через блок сложения 4, где производится сложение проверочных символов кодовой комбинации с проверочными символами, образованными декодирующим блоком 9, поступают через выход 37 устройства, переключатель 27 на. вход декодирующего блока 9 и первый вход второго блока сложения 11. Декодиругаций блок 9 по информационным символам этой комбинации формирует проверочным символы и выдает из с одного из своих выходов на второй вход блока сложения 11 и через коммутатор 32, элементы за,цержки 31 и 5 на второй вход блока сложения 4. Элемент задержки .5 обеспечивает согласование во времени поступления сигналов на первой и второй входы блока 4. Так как в начальной стадии контрольного режима сигналы с выхода декодирующего блока 9 проходят через блоки 32 и 31 на вход элемента 5 без запаздывания, то в блоке сложения 4 проверочные символы, сформированные блоком 9 по информационным символам комбинации, поступившей на его вход в данный момент, складываются с проверочными, . символами следующей передаваемой ком бинации. Поэтому сигналы с выхода бло ка сложения 11, являющиеся результат сложения проверочньк символов, посту пивших вместе с комбинацией, и сим волов, сформированных декодирующим блоком 9, совпадают с контрольными символами, сформированными кодирующим блоком 3 и поступаю1ци 1и с первого выхода элемента задержки 10 на вход блока сравнения 12. Входные сиг налы на остальных б-поках сравнения не совпадают един с другим. Если в это время открыт элемент управления, подсоединенный к выходу блока сравнения с несовпадающими входами то на входы счетчика 6 и элемента памяти 8 ошиб ка перевопоступают сигналы дя устройство в режим запроса и повторения комбинаций. Сигналы ошибка поступают также на второй вход триггера 33, удерживая его в исходном положении. В этом случае на вход анализатора 25 входные сигналы не поступают. Однако после появления нескольких сигналов совпадения на выходе блока сравнения 12 сигнал с выхода регистра 15 изменяет состояние блоков памяти 18-20, открывает элемент управ ления 21, подключенный к блоку сравне ния 12 и закрывает другие элементы уп Сигнал сшибка с выход равления , элементов 21-23 не поступает. По окон чании цикла запроса на вход анализато ра 25 с выхода второго накопителя-пов торителя 7 начинают поступать сигналы ЕСЛИ поступившие на вход анализатора 25 сигналы соответствуют контрольной последовательности, то с выхода анализатора 25 на вхся счетчика 29 начинают поступать сигналы, под воздействием которых счетчик 29 срабатывает и выдает сигнал на первый вход триггера 35, переводя триггер из исходного состояния (например-. левого ), в другое {единичное). По сигналу с выхода триггера при пере ходе его в единичное состояние срабатывает коммутатор 32 и подключает второй выход декодирующего блока 9 ко второму входу элемента задерж ки 31, вводя тем самым дополнительную задержку в цепь прохождения проверочных символов из блока 9 в первый блок сложения на время, равное длительности передачи одной кодовой комбинаций. В результате этого совпадение сигналов происходит уже не на входах блока сравнения 12, а на входах блока сравнения 13, один из входов которого подключен ко,второму выходу элемента 10. Сигналы ошибка с выхода блока 12 через открытый элемент управления 21 поступают на второй вход триггера 33, переводя его в ну левое состояние, и на вход счетчика 6 и переводит устройство в режим запроса до тех пор, пока под воздействием сигналов совпадения.с выхода блока сравнения 13 через регистр 16 и блок памяти 19 не закрывается элемент управления 21, через который проходили сигналы ошибка, и не открывается элемент управления 22, подключенный к блоку сравнения 13 с совпадагацими входными сигналами, т. е. пока не прекратится поступление на вход счетчика 6 с.игналов ошибка. После выхода устройства из режима запроса на вход анализатора 25 опять начинают поступать сигналы контрольной последовательности. При правильном ее приеме анализатор 25 начинает выдавать на вход счетчика 29 сигналы, под воздействием которых счетчик 29 вырабатывает сигнал на переключение триггера 33. Сигнал с выхсяа триггера поступает на переключение комму,татора 32. Коммутатор 32 подключает сигналы проверочных символов с выхода декодирующего блока 9 на третий вход элемента задержки 31, увеличив тем самым задержку в прохождении сигналов с выхода блока 9 на вход блока 4 на время, равное длительности передачи одной комбинации. В результате с выхода элемента управления 22 начинают выдаваться сигналы ошибка, так как сигналы на входе блока сравнения 13 перестают совпадать один с другим, а совпадение входных сигналов происходит на входах блока сравнения 14. В дальнейшем устройство работает аналогично. Полная проверка исправности действия всех узлов и блоков устройства завершается после установления такой величины задержки в элементе 31, когда совпадение входных сигналов происходит в блоке сравнения, подключенным к последнему выводу элемента задержки 10. Триггер 33 под воздействием сигналов с выхода счетчика 29 и с объединенного выхода элементов управления 21-23, поступающих на разные входы триггера, периодически изменяет своесостояние, обеспечивая управление коммутатосчетчиком, емкость которого выбрана равной числу выводов с элемента задержки 10 или большей, чем это число. Появление сигнала с выхода счетчика 30 на входе блока управления 28 служит признаком окончания контрольной проверки работе-, способности устройства. При исправном действии всех узлов и блоков устройства время его контрольной проверки всегда одинаково. При появлении неисправности время контрольной проверки увеличивается. Поэтому производя измерение времени или подсчета,числа тактов работы устройства от.мсмента перек.пючения его в режим контроля и до момента поступ:л,ения в блок управления 28 сигнала с вахода счетчика 30, можно судить о результате контрольной проверки ТВ а .Задержка в срабатьтании сче чику 30 происходит при наругиении периодичности поступления на управляющие входы триггера 33.сигналов оши ка и сигналов с выхода счетчика 29 tTaK приналичии неисправностей в тра те передачи информационных сигналов анализатор 25 контрольной последовательности сигналов не вырабатывает сигналы соответствия и не выдает их на вход счетчика 29. При наличиине. исправностей, приводящих к Постоянно му выделению сигналов ошибка , на пример при отказах кодиругацего или декодирующего блоков, блоков сложения, а также элементов задержки, бло ков сравйёния, регистров, блокбв памяти, при несогласованных задержках в прохождений сигналов через элемент 31 и через элемент 10 от его входа До выхода, подключенного через соотв вётствующий блок сравнения к открыто му элементу управления, сигнала на вхбдй трётЁёг 6 с ч ётчик а так же п ос тупатет, что г1Е иводит к зад.ержкё окрн.чания контрольного режима и обнару.женйю, таким образом, наличйя не исправности в устройстве. Предложенное устройство позволяет проверить исправность действия практически всех узлов и блоков устройства, чтоповйиаетего надёжн.ость . Формула.изобретения . Устройство для передачи и приема дискретных сигналов, содержащее первый переключатель, выход которого подключен ко вхоДу коДйрукщего бл ка и через первый накопите/ ь-повторитель к первому входу первого переключателя, первый .выход кодирующего блока соединен с первым входом перво го блока сложения, второй выход кодирующего блока подключен ко входу второго эл емента задержки, выходы ко Торого соединены с первымивходамй соответствующих блоков сравнения, вы ход второго блокасложемия П13дю1ИЧей ко вторьмвхсдам блоков cpaB HeHiiW, йыходь которьлх подклинены ко входам соответствующих регистров и к пер. вым входам соответствукщих элё лeнтoв управлён я, выходы регистров соедине ны сЬ входами блокоВ памяти, выходы подключены ко вторым входам соответствукщих элементов управления выходы которых соединены с первымй входами элемента памяти, первого счё .Чйка и с первыми выходами декоДйруюЩегр 6лока и -элемента памяти, первый выход первого счетчика подключен к третьему-входу первого переклюнателя , второй выход первого счетчика соединен с первым входом второго накопителя-повторителя, ко .второму входу которого подключен второй выход декодируквдего блока, третий выход счетчика соединен со вторым входом элемента памяти, третий выход декодирующего блока соединен со вторым входом второго блока сложения, выход первого блока сложения: подключен к первому выходу устройства , выход второго накопителя-повторителя соединен со вторым выходом устройства, выход первого блока задержки подключен ко второму . входу первого блока сложения, о тл и чающееся тем, что, с целью повышения надежности устройства, в него введены второй и третий переключатели, второй и Третий счетчики, лОк уп завления, датчик, анализатор, триггер, коммутатор и- третий элемент задержки, выход датчика подключен к первому входу второго переключателя, второй вход которого соединен с первым, входом устройства, а выход - со втбрым входом первого переключателя, выход блока управления подключен к третьему входу второго переключателя, к первым входам второго и третьего счетчиков, к первому входу триггера, к первому входу ксммутатора, к первым входам анализатора и третьего переключателя, второй вход которого соединен; с вьзходом первого блока сложения, а третий вход подключен к.о второму входу устройства, выход третьего переключателя соединен с первыми входами декодирующего блока и второго блока сложения, выход второго накопителя-повторителя подключён ко второму входу анализатора, выход которого соединен со вторым входом второго счетчика, выходы элементов управления подключены ко второму входу триггера, третий ВХ.ОД которого соединен с выходом второго счетчика, выход триггера подключен ко второму входу коммутатора, и ко второму входу третьегосчетчика, ййк од которого соединен со входсм блока управления, третий выход декодиругацего блока подключен к третьему входу коммутатора, выходы которого соединены с соответствующими входами третьего элемента задержки, выход третьего элемента задержки подключен ко второму вхсяу первого элемента задержки , . Источники информации, принятые во внимание при экспертизе 1. Авторское свидётёльство СССР №447745, кл. G 08 С 25/02, 26.03.73. 2. Авторское свидетё41ьство СССР № 557403, .кл. G ОЗ С 19/28, 13.10.75 (прототип).

37

36

Авторы

Даты

1980-04-05—Публикация

1977-10-10—Подача