(54) ЧАСТОТНО-ИМПУЛЬСНОЕ ДИФФЕРЕНЦИРУЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсное дифференцирующее устройство | 1990 |

|

SU1751755A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU920722A1 |

| Частотно-импульсное диференцирующее устройство | 1977 |

|

SU640315A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1979 |

|

SU862150A1 |

| ВСГ.СОЮЗ-НА1§ | 1973 |

|

SU374617A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 1972 |

|

SU426318A1 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU424144A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

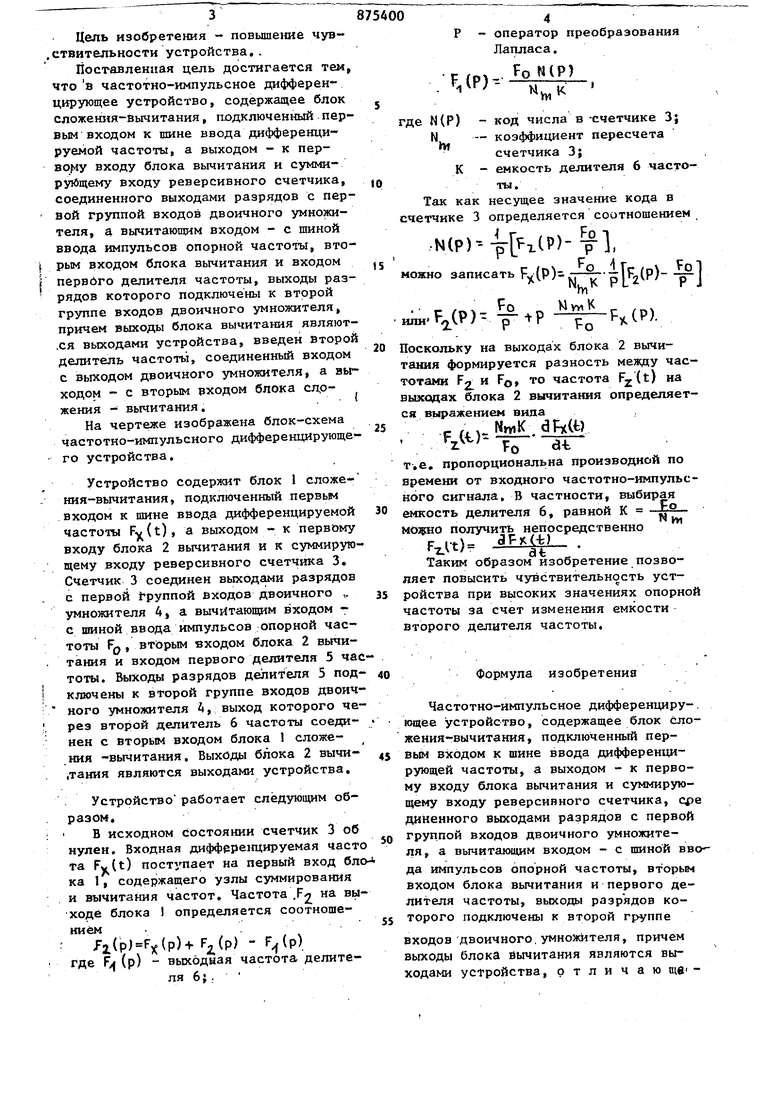

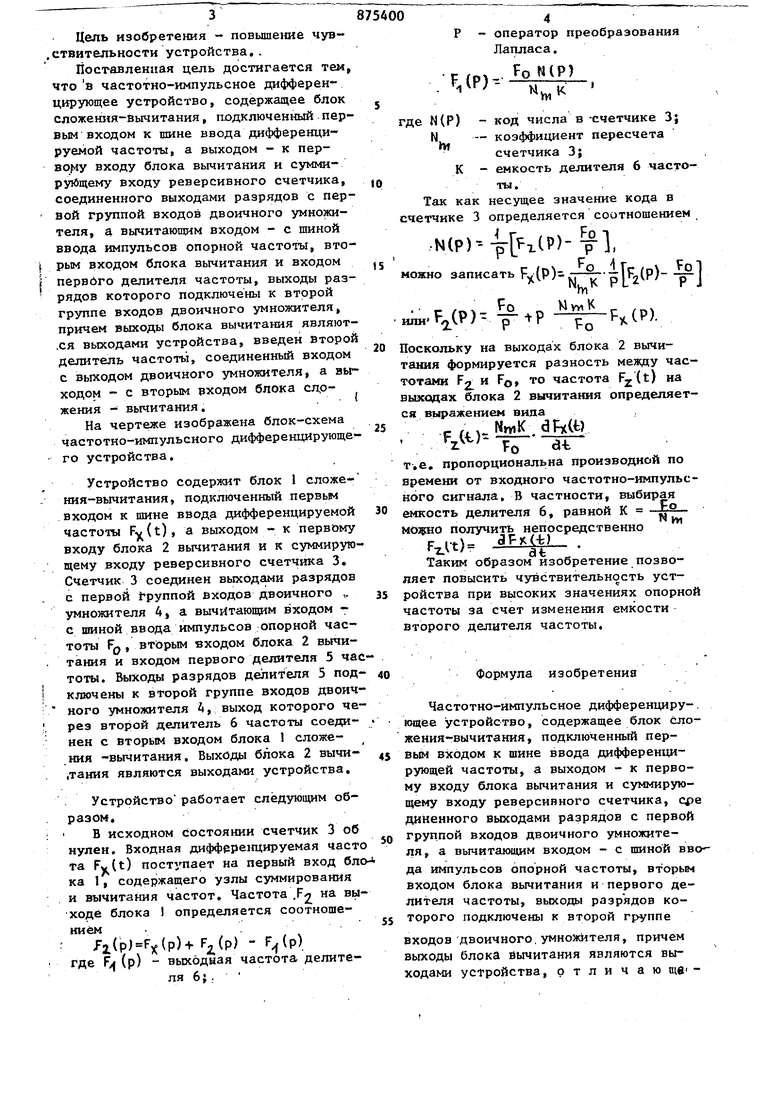

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам.дифференцирова«ия частотно-импульсных сигналов. Известно частотно-ямпульснОе дифференцирующее устройство, содержащее делитель частоты, двоичный умножитель, реверсивный счетчик и блок вы. чнтания р . . . Недостатком устройства является пониженная точность да1фференцироваНИЯ из-за наличия апериодического за / паздыванИя.; Известно также частотно-ймпульсное дифференцирзлощее устройство, содержащее блоки суммирования и вычи-. . тания, триггер знака, элемент ИЛИ, делитель частоты, двоичный умножитель и реверсивньп1 счетчик f2j. Недостатком данного устройства яв ляется пониженная чувствительность ди еренцнрования при высокой опорной частоте. ;. Наиболее близким к предлагаемомуявляетсй частотно-импульсное дифференцирующее устройство, содержащее блок сложения - вычитания, подключенный .первым входом к шине ввода дифференцируемой частоты, а ыходомк первому входу блока вычитания и суммирующему входу реверсивного счетчика, соединенного выходами разрядов с первой группой входов двоичного умножителя, а вычитающнм входом - с шиной ввода импульсов опорной частоты, вторья4 входом блока вычитания и входом делителя частоты, выходы разрядов которого подключены к второй группе входов двоичного умножителя, соединенного выходом с вторым входом блока сложения - вычитания, причем выходы блока вычитания являются выходами устройства. f3j Недостатком известного устройства является пониженная чувствительность при высоких значениях опорной часо.ты. .. 3 Цель изобретения - повьшение чув.ствителькости устройства,. Поставленаая цель достигается тем что в частотно-импульсное дифференцирующее устройство, содержащее блок сложения-вычитания, подключенный первым входом к шине ввода дифференцируемой частоты, а выходом - к первому входу блока вычитания и суммируйщему входу реверсивного счетчика, соединенного выходами разрядов с первой группой входов двоичного умножителя, а. вычитающим входом - с шиной ввода импульсов опорной частоты, вторым входом блока вычитания и входом первбго делителя частоты, выходы разрядов которого подключены к второй группе входов двоичного умножителя, причем выходы блока вычитания являют,ся выходами устройства, введен второй делитель частоть, соединенный входом с выходом двоичного умножителя, а выходом - с вторьм входом блока сдожения - вычитания. На чертеже изображена блок-схема частотно-импульсного дифференцирующего устройства. Устройство содержит блок I сложения-вычитания, подключенный первьм входом к тине ввода дифференцируемой частоты Fy(t), а выходом - к первому входу блока 2 вычитания и к суммирующему входу реверсивного счетчика 3. Счетчик 3 соединен выходами разрядов с nepBoii Группой входов двоичного ,. умножителя 4, а вычитающим входом с шиной ввода импульсов опорной частоты FQ , вторым входом блока 2 вычитания и входом первого делителя 5 час тоты. Выходы разрядов делителя 5 подключены к второй группе входов двоичного умножителя А, выход которого через второй делитель 6 частоты соедийен с вторым входом блока 1 сложе.ния -вычитания. Выходы блока 2 вычи,тания являются выходами устройства, . Устройство работает следующим образом. В исходном состоянии счетчик 3 об нулен. Входная дифференцируемая часто та Fw(t) поступает на первый вход бло ка 1, содержащего узлы суммирования и вычитания частот. Частота f ходе блока I определяется соотношением fi(p)F(p)4. F,,(p) - F(p) где FX(р) - выходная частота делителя 6 ;. О Р - оператор преобразования Лапласа. ptpx. FoN(P м,„к где N(P) - код числа в -счетчике 3; N. - коэффициент пересчета счетчика 3; - емкость делителя 6 частоты. Так как несущее значение кода в счетчике 3 определяется соотношением Н(Р))-т1. можно записать Fy(P)(p)- f/rk-k ,4 МуиК .„. ).Р Поскольку на выходах блока 2 вычитания формируется разность между частотами . о частота Fjrit) на выходах блока 2 вычитания определяется выражением вида Fa)..iW FO at т.е. пропорциональна производной по времени от входного частотно-импульсного сигнала, В частности, выбирая емкость делителя 6, равной К МОЩ1О получить непосредственно ) ( Таким образом изобретение позволяет повысить чувствительность устройства при высоких значениях опорной частоты за счет изменения емкости второго делителя частоты. Формула изобретения Частотно-импульсное дифференциру-. ющее устройство, содержащее блок сложения-вычитания, подключенный первьпи входом к шине ввода дифференцирующей частоты, а выходом - к первому входу блока вычитания и суммирующему входу реверсивного счетчика, ере диненного выходами разрядов с первой группой входов Двоичного умножителя, а вычитакмцим входом - с шиной вво да импульсов опорной частоты, вторым входом блока вычитания и первого делителя частоты, выходы разрядов которого подключены к второй группе ходов двоичного,умножителя, причем ыходы блока вычитания являются выодами устройства, отличаю щв- е с я тем, что, с цель повьгаекия чувствительности устройства, в него введен второй делитель частоты, соед ненный входом с выходом двоичного ум ножителя а выходсж - с вторым входом блока сложения-вычитания. -Источники информации, принятые во внимание при экспертизе 0 6 1.Авторское свидетельство СССР № 374617, кл, G 06 G 7/18, 197Г. 2.Авторское свидетельство СССР по заявке 2506746/18-24, кл. G 06 F 7/38, 1977. 3.Авторское свидетельство СССР № 622110, кл. G.06 F 7/18, 1977 (прототип) . ,

Авторы

Даты

1981-10-23—Публикация

1980-02-27—Подача