1

Изобретение относится к области автоматики и вычислительной техники и может быть применено в информационно-измерительных и управляющих системах с широким диапазоном пзменения входного частотно-импульсного сигнала.

Известно дифференцирующее устройство, содержащее частотно-имнульсный вычитающий блок, входы которого соединены соответственно с входом устройства и выходом двоичного умножителя, подключенного входами к выходам делителя опорной частоты и выходам реверсивного счетчика, входами соединенного соответственно с входом устройства п выходом двоичного умножителя.

Известно также дифференцирующее устройство, содержан1,ее знаковый, триггер и частотно-импульсный умножитель с включенным на его входе элементом «ИЛИ, входы которого подключены к выходам частотно-имиульсного вычитающего блока и входом знакового триггера, а выход частотно-импульсного умпожителя соединен с счетным входом реверсивного счетчика.

Наиболее близким по технической сущности к изобретению является устройство для дифференцирования частотно-импульсных сигналов, содержащее блок управления, соединенный входом с входом устройства, неуправляемый делитель частоты, выход которого подключен к счетному входу основного счетчика, генератор опорной частоты, трп управляемых делителя частоты, три группы логических элементов «И, соединенных первыми входами с поразрядными выходами основного счетчика п подключенных выходами к соответствующим цифровым входам управляемых делителей частоты, блок вычитания импульсов с включенным на его входах распределителем импульсов, сигнальные входы которого подключены к выходам первого и второго управляемых делптелей частоты, причем выход вычитающего блока соедииеп с спгиальиым входом третьего управляемого делителя частоты, сигнальные входы первого и второго управляемых делителей частоты подключены к входу неуправляемого делителя частоты, а вторые входы групп элементов «И всех грунн, управляющий вход распределителя импульсов и входы обпуления управляемых делителей частоты и основного счетчика соединены с соответствующими выходами блока управления.

Известные устройства имеют ограниченный диапазон изменения входной дифференцируемой частоты.

Цель изобретения - расщнренне диапазона изменения в.ходного сигнала.

Это достигается тем, что в предлагаемое дифференцирующее устройство введены два управляемых делителя частоты, дещифратор и

логический блок, подключенный входами к входу устройства и выходам дешифратора, соединенного входами с поразрядными выходами осповпого счетчика, причем выходы логического блока соединены с входами управления изменением коэффициентов деления дополнительных управляемых делителей частоты. Сигнальный вход первого дополнительного управляемого делителя частоты, подключенного выходом к входу неуправляемого делителя частоты, соединен с выходом генератора опорной частоты, а сигнальный вход второго дополпительного управляемого делителя частоты, подключенного выходом к выходу устройства, соединен с выходом третьего основного управляемого делителя частоты.

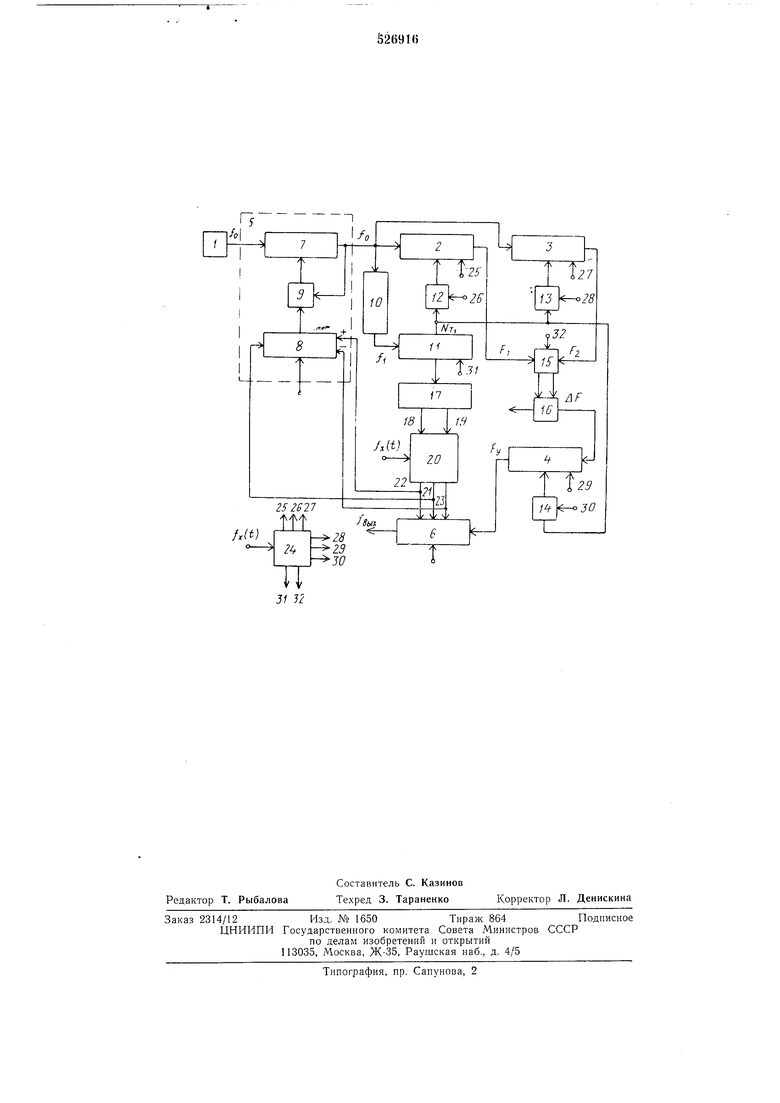

На чертеже показана блок- схема предлагаемого устройства.

Устройство содержит генератор 1 онорной частоты, управляемые делители 2, 3, 4 частоты, дополнительные управляемые делителя 5 и 6 частоты, каждый из которых состоит из вычитающего счетчика 7, реверсивпого сдвигающего регистра 8 и группы логических элементов «И 9, пеуправляемый делитель частоты 10, основной суммирующий счетчик II, три группы элементов «И 12, 13 и 14, распределитель импульсов 15, вычитающий блок 16, дешифратор 17 с двумя выходами 18 и 19 опорных значений кода, логический блок 20 с сдвигающим выходом 21 и двумя знаковыми выходами 22 и 23, блок управления 24 с восемью выходами 25-32 управления узлами устройства.

Устройство работает следующим образом.

В блоке управления 24 из последовательности импульсов входного сигнала lx(t) формируются управляющие сигналы, определяющие последовательность работы узлов устройства. С выхода генератора 1 импульсы опорной частоты fo подаются на счетный вход управляемого делителя 5 частоты, где она делится на коэффициент М, образующийся в виде параллельного кода в регистре 8. Частота с выхода делителя 5 поступает на счетные входы неуправляемого делителя 10 и управляемых делителей 2 и 3, в делителях 2 и 3 делится на коэффициенты, занисанные в виде параллельного кода в регистрах памяти соответствующего делителя. В делителе 10 частота делится па постоянный коэффициент К. Частота с выхода делителя 10 поступает па счетный вход счетчика 11, где ее импульсы суммируются в промежутках времени, равных текущим периодам входного сигнала и формируемых путем подачи на вход обнуления счетчика 11 импульсов входного сигнала ix(t) через блок 24.

На выходах разрядов счетчика И в момент опроса с блока 24 образуется код , пропорциональный текущему периоду Тг входиого сигнала

/о

Т.

Лг

М-К

Этот код через элементы «И 14 и элементы «И 12 либо 13 в зависимости от сигналов управления с выходов 30, 26 и 28 блока 24 записывается в предварительно очищенные от старой информации сигналами сброса с выходов 29, 2Г), 27 регистры памяти управляемых делителей частоты 2, 3 и 4. Элемеиты «И 14 открываются по каждому импульсу окончания текущего периода, и в регистр памяти управляемого делителя 4 записывается код i-ro периода. Элементы «И 12 и 13 открываются поочередю, в результате чего в регпстр памяти одного занисывается код г-го периода, а в другом остается код (i-1)-го периода, записанный в предыдущем такте.

На выходе делителей 2 и 3 в зависимости от содержимого регистров памяти образуются частоты

/.(0 ; PAf-T,):-.

Эти частоты поступают на распределптель импульсов 15, который управляется сигналом от блока 24 таким образом, что всегда на одном из его выходов присутствует частота Px(i), а на другом F(t-Ti) независимо от того, на какие входы эти частоты ноступили. В блоке 16 формируется знак и величина разности этих частот hFx(t), пропорциональная производной входной частоты и текущему периоду входного сигнала

F.,(.

А/(/) /,(/).

(it

Эта частота поступает на счетный вход управляемого делителя частоты 4, осуществляющего деление ее па величину Лг,- нропорцнопальную текуще.му периоду входного сигпала. Частота на выходе делителя 4

df(t}

у/о

dt

Эта частота делится в управляемом делителе 6 на коэффициент М, такой же как в делителе 5, в результате чего выходная частота устройства

К dfAt) )---т. е. нропорциональна производиой входиого сигнала но времени.

Частота fo является промежуточной и ее изменение не сказывается на выходном сигнале. Это обстоятельство позволяет ностроить автоматическую следящую систему изменения входной частоты fi основного счетчика 11 в зависимости от измепения входной частоты устройства txCO и соответственно кода NT. в счетчике 11 путем соответствующего изменения коэффициента деления делителя 5 в зависимости от превышения кодом N т в счетчике 11 опорных значений. Следяшая система Быполияется из дешифратора 17, подключенного к выходам разрядов счетчика 11 и логического блока 20, подключенного к двум выходам дещифратора 17 и к входу устройства.

Опорное значение кода Лм,;,,, при достижении которого кодом в счетчи -;е 11 на гялходе 18 дешифратора 17 появляется г.;(нал, выбирается из еоображений обеспечения требуемой дискретности изменения для минимального значения периода входного сигнала

100

h-T

Л.

где б - требуемая дискретность изменения кода иериода /л-. Опорное значение кода Умпкс, по достижении которого на выходе 19 дешифратора 17 появляется сигнал, выбирается вдвое большим, чем Л/.мин- При уменьшении входной частоты f.vfO в счетчике 11 начинает увеличиваться, и когда входная частота станет вдвое меньшей максимальной входной частоты, т. е. f.xГО /макс/2 код в счетчике 11 достигает значения Уыакс и на выходе 19 дешифратора 17 появляется сигнал, по которому в логическом блоке 20 вырабатывается сигпал знака. По этому сигналу по выходу 22 устанавливаются реверсивные сдвигающие регистры 8 в делителях 5 и 6 на сложение. Затем вырабатывается сигнал сдвига, который по выходу 21 поступает на сдвиговые входы регистра 8, осуществляя сдвиг влево кода в регистре, в результате чего коэффициент деления делителей 5 и 6 увеличивается вдвое относительно первоначального значения. Соответственно вдвое уменьшаются частота о п /ь Код в счетчике И уменьшается и изменяется в диаиазоне Лмин Лг.. Л/макс- При дальнейшем уменьшении входной частоты код NT

опять увеличивается и при fx(О /максГО/4 вновь достигает значения/V. . Процесс увеличения вдвое коэффициентов деления делителей 5 и 6 повторяется. Аналогично работает устройство и дальше, каждый раз увеличивая вдвое коэффициенты деления делителей 5 и 6 при достижении кодом Лт-. в счетчике 11

опорного значения Лмакс.

Если входная частота fx(t) начинает увеличиваться, коэффициенты деления делителей 5 и 6 уменьшаются. При увеличении входной частоты вдвое относительно первоначальной, соответствующей установленному коэффициенту деления делителей 5 и 6, код в счетчике 11 уменьшается до значения При этом на выходе 18 дешифратора 17 появляется сигнал, по которому в блоке 20 с учетом отпосительного появления во времени входного сигнала вырабатываются сигнал изменения знака управления регистрами 8 на вычитание и сигнал сдвига регистров вправо, в результате чего коэффициепт деления делителей 5 и 6 уменьшается вдвое и соответственно код NT увеличивается и начинает изменяться в диапазоне т Лмакс. Аналогично работает устройство и дальше, каждый раз уменьшая

коэффициенты деле/ ая де штслс 5 и 6 идвоё при уменьшении кода в счетчике 11 до величи); опорного кода Лмиц. При таком построении устройства верхняя

граница входной частоты ограничивается быстродействием счетных разрядов, а нижняя входная частота может изменяться практически неограниченно. При этом, объем счетных узлов устройства лишь па 1-2 разряда превышает требуемый объем для максимально входной частоты. Бла -одаря этому )редлагаемое устройство расширяет диапазон измене ия входной частоты при оптимальном объеме счетных узлов устройства.

.

Формула изобретения

Устройство для дифференцирования частотно-импульсных сигналов, содержащее блок управления, соединенный входом с входом устройства, нeyпpaвляe Ь Й делитель частоты, выход которого подключен к счетному входу основного счетчика, генератор опорной частоты, три управляемых делителя частоты, три груп 1Ь элсментов «и, соединенных

первыми в.ходали с поразрядным выходами ос овного сче1Ч 1ка и )х выходам к соответству 0 Ц1 м Ц 1фровым входам управляемых делителей частоты, блок импульсов с включенным на его в.чодах распреде. ителсм импульсов, сигнальные входы которого подкл очень к выходам первого и второго у равляемых дел телей частоты, причем выход блока соедине с сигналь 1ым входом третьего управляемого делителя частоты, сигнальные входы первого и вторО -о управляемых дел1 телей частоты под лючень к входу неуправляемо о делителя частоты, а вторые входы элементов «И всех групп, управля 0 дий вход рас ределителя 1мпульсов i входы обнуления у равляе 1з х дел телей частоты основного счетчика соединены с соответствующи.ми выходами блока управления, отл чающееся тем, что, с целью расширения Д 1апазона изменения входного сигнала, в устройство дополнительно введены два управляемых делителя частоты, дещифратор и логический блок, под хлю3енный входами к входу устройства и вы.ходам дешифратора, соединенного входами с поразрядными вы.ходами основного счетчика, причем выходы логического блока соединены с входами управления изменением коэффициентов деления дополнительных управляемых делителей частоты, сигнальный вход первого дополнительного управляемого делителя частоты, подключенного выходом к входу неунравляемого дел 1теля частоты, с выходом генератора опорной частоты, с 1гнальнь Й вход второго дополнительного управляемого делителя частоты, подключен 1ого выходом к выходу устройства, с выходом третьего основного управляемого де лителя частоты.

2S2S27

.W

28 2.9 -да

U

31 32

(:

Т

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсный функциональный преобразователь | 1975 |

|

SU543945A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU525235A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Умножитель частотно-импульсных сигналов | 1981 |

|

SU968812A1 |

| Часточно-импульсное дифференцирующее устройство | 1977 |

|

SU691891A1 |

| Пересчетное устройство | 1981 |

|

SU993460A1 |

| Умножитель частоты | 1990 |

|

SU1775840A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Умножитель частоты низко-частотных сигналов | 1977 |

|

SU744906A1 |

Авторы

Даты

1976-08-30—Публикация

1975-06-18—Подача