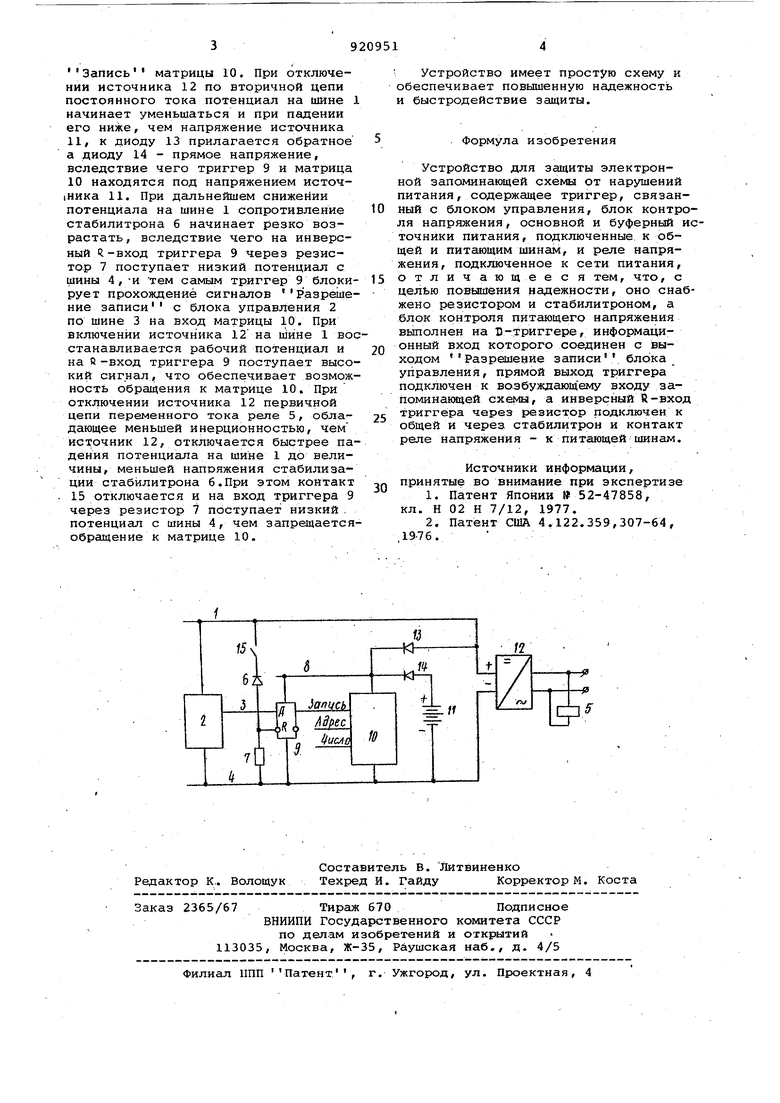

.(54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ЭЛЕКТРОННОЙ ЗАПОМИНАЮЩЕЙ СХЕМЫ ОТ НАРУШЕНИЙ Изобретение относится к защите электронной техники от нарушений питания. . Известно устройство защиты полупроводниковой запоминающей схемы, содержащее блоки контроля и коммутации основного и буферного источников питания 1. Недостаток его - сложность схемы Наиболее близким по техническим средствам и достигаемому результату является устройство для защиты запоминающей схемы от нарушения питания содержащее триггер, связанный с блоком управления, блок контроля напряжения, основной и буферный источники питания, подключенные к общей и питающим шинам, и реле напряжения, подключенное к сети питания 12. Недостаток этого устройства - пониженная надежность. Цель изобретения - повышение надежности. Для достижения этой цели устройст во снабжено резистором и стабилитроном, а блок контроля питающего напряжения выполнен на D-триггере, информационный вход которого соединен, .с выходом Разрешение записи блока управления, прямой выход триггера

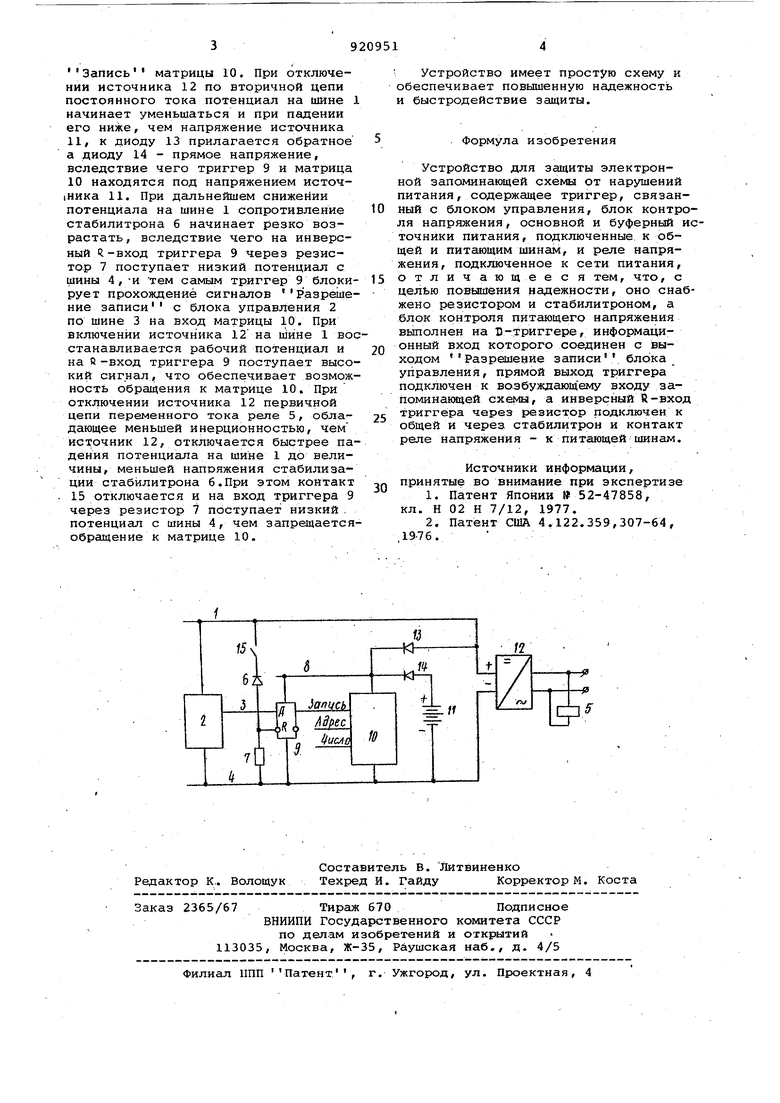

ПИТАНИЯ подключен к возбузвдающему входу запоминающей схемы, а инверсный R-вход триггера через резистор подключен к общей и через стабилитрон и контакт реле напряжения - к питающей шинам. На чертеже представлена схема устройства. Схема устройства содержит шину питания 1 блока управления 2, шину Разрешение записи 3 и общую шину 4, реле контроля напряжения сети 5, стабилитрон 6, резистор 7, шину питания 8, D-триггер 9, запоминающую матрицу 10, буферный 11 и основной 12 источники питания с развязывающими диодами 1-3 и 14, контакт 15 реле 5. Напряжение источника 11 несколько ниже напряжения источника питания 12, поэтому при работе источника 12 к диоду 14 приложено обратное, а диоду 13 - прямое напряжение, вследствие чего блок 2, триггер 9 и матрица 10 находятся под напряжением источника 12. йясокий потенциал с шины 1 через замкнутый контакт 15, стабилитрон 6 поступает на кнверсный й-вход триггера 9, тем самым разрешается прохождение сигнала .Разрешение записи с блока управления 2 по шине 3 через триггер 9 на вход Запись матрицы 10. При отключении источника 12 по вторичной цепи постоянного тока потенциал на шине начинает уменьшаться и при падении его ниже, чем напряжение источника 11, к диоду 13 прилагается обратное а диоду 14 - прямое напряжение, вследствие чего триггер 9 и матрица 10 находятся под напряжением источ1ника 11. При дальнейшем снижении потенциала на шине 1 сопротивление стабилитрона 6 начинает резко возрастать, вследствие чего на инверсный Ч -вход триггера 9 через резистор 7 поступает низкий потенциал с шины 4, -и тем самьом триггер 9 блоки рует прохождение сигналов Paspeiae ние записи с блока управления 2 по шине 3 на вход матрицы 10. При включении источника 12 на Ыине 1 во станавливается рабочий потенциал и на и-вход триггера 9 поступает высо кий сигнал, что обеспечивает возмож ность обращения к матрице 10. При отключении источника 12 первичной цепи переменного тока реле 5, обладающее меньшей инерционностью, чем источник 12, отключается быстрее па дения потенциала на шине 1 до величины, меньшей напряжения стабилизации стабилитрона 6.При этом контакт 15 отключается и на вход триггера 9 через резистор 7 поступает низкий . потенциал с шины 4, чем запрещается обращение к матрице 10. Устройство имеет простую схему и обеспечивает повышенную надежность и быстродействие защиты. Формула изобретения Устройство для защиты электронной запоминающей схемы от нарушений питания, содержащее триггер, связанный с блоком управления, блок контроля напряжения, основной и буферный источники питания, подключенные к общей и питающим шинам, и реле напряжения, подключенное к сети питания, отлич ающее с я тем, что, с целью повышения надежности, оно снабжено резистором и стабилитроном, а блок контроля питающего напряжения выполнен на тз-триггере, информационный вход которого соединен с выходом Разрешение записи , блока управления, прямой выход триггера подключен к во-збуждающему входу запоминающей схемы, а инверсный R-вход триггера через резистор подключен к общей и через стабилитрон и контакт реле напряжения - к питающей шинам. Источники информации, принятые во внимание при экспертизе 1.Патент Японии №52-47858, кл. Н 02 Н 7/12, 1977. 2.Патент США 4.122.359,307-64, .19.76.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для проверки средств защиты трехфазной сети от перенапряжений | 1986 |

|

SU1411880A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ПРОГРАММАТОР | 2011 |

|

RU2470389C1 |

| Установка для нанесения гальванических покрытий на ферромагнитные изделия | 1988 |

|

SU1576597A2 |

| Устройство для пожарной сигнализации | 1977 |

|

SU669373A1 |

| Устройство для токовой защиты электроустановки | 1990 |

|

SU1777195A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

Авторы

Даты

1982-04-15—Публикация

1980-07-07—Подача