(54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1978 |

|

SU818013A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Цифровой демодулятор сигналов относительной фазовой манипуляции | 1986 |

|

SU1374443A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1040525A2 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Устройство для программного управления с восстановлением информации | 1988 |

|

SU1603344A1 |

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| Устройство для ввода информации (его варианты) | 1985 |

|

SU1290286A1 |

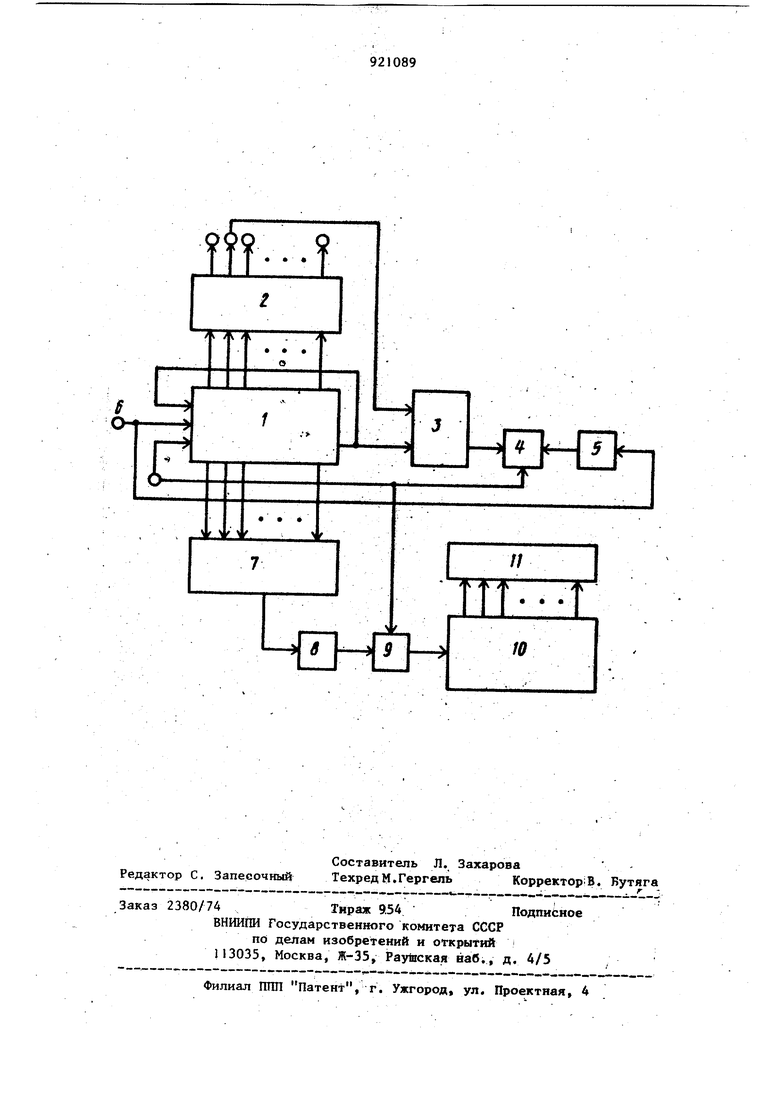

Изобретение .о.тносится к импульсной технике и может быть использовано в аппаратуре передачи данных и телеграфии. Известен распределитель импульсов .по авт. св. № 818013, являкщийся наиболее близким техническим решением к предлагаемому и содержащи регист, соединенный с дешифратором, элементы И, НЕ и триггер 1. Недостатком этого устройства является невозможность контроля коли чества сбоев элементов и определени их статистических характеристик 1л Цель изобретения - расширение фу циональных возможностей. Для достижения этой цели в расп ределитель импульсов, содерхсащий регистр, соединенный с дешифратором элемент И, НЕ и триггер , установоч ный вход которого соединен со вторым выходом дешифратора, а счетный вход - с другим выходом регистра и его входом, причем выход триггера подключен к первому входу элемента И, второй вход которого череэ элемент НЕ соединен с тактирующим входом регистра, при этом выход элемента И подключен к установочному входу регистра, введены соединенные последовательно дополнительный дешифратор, инвертор, дополнительный элемент И, счетчик импульсов и индикаторный блок, причем входы дополнительного дешифратора соединены с соответствующими выходами регистра, а другой вход дополнительного элемента И подключен к выходу элемента И. На чертеже представлена структурная схема распределителя. Распределитель содержит регистр I сдвига с перекрестной обратной свяэью, дешифратор 2, выходы которого являются выходами распределителя, счетный триггер 3, элемент 4 И, элемент 5 НЕ, вход 6, дешифратор 7 нуля, инвертор 8, элемент 9 И, сче.ч3 9 чик 10 импульсов и индикаторный блок 11. Распределитель работает следуюОим образом. На вход 6 поступает тактовая час тота периоды которой следует расп ределить во времени. В условиях отсутствия помех расп ределитель после установки в начале работы в исходное состояние работает обЫЧ1ШМ образом. На выходах дешифратору 2 появляются распределенные по ,времени сигналы в соотве ствий с изменением состояний регист ра 1. Эта последовательность импуль сов до воздействия на регистд i помехи остается неизменной и правильг яой. При переходе последнего триг гера регистра 1 в исходное состояние, что является признаком (по необязательным) конца текущего цикла триггер 3 по счетному входу устанавливается в состояйие, разрешающее работу элемента 4. Так как на второй вход последнего с вьпсода элемента 5, поступает сигнал в противофазе с сигналом на входе 6 регистра I, то на выходе элемента 4 образуется сигнал во время дейстйия отрицательного полупериода входной такто вой частоты, который сбрасывает регистр 1 в исходное состояние..Естественно что если при этом регистр «е находится в исходном состоянии (наличие сбоя) , то он приведен в это состояние принудительно. Триггер 3 приводится в исходное состояние сигналом со втогого выхода дешиф« ратора 2, сдвинутым во времени относительно импульса сброса. При возникновении сбоя.распредели теля один или несколько триггеров регистра 1 во время его последнего триггера в ноль находятся в единице. Это означает, что дешифратор 7 нуля, связанный с выходами всех раз 4 рядов регистра 1 и вьщеляющий его нулевое состояние на своем выходе, не вырабатывает рабочий снгийл и с инвертора 8 появляется сигнал, разрешаюв(ий через элемент 9 прохождение импульса с выхода элемента 4 на вход счетчика 10, который фиксирует и запоминает такие импульсы. Состояние счетчика 10 (количество накопленных импульсов о сбоях) отображается индикаторным блоком 11. При этом необходимая для срабатывания счетчика 10 задержка рабочего сигнала на выходе инвертора 8 обеспечивается элементами дешифратора 7 (после сброса в ноль регистра импульсом с выхода элемента 4) |i этим же инвертором 8. По данньгм, снимаемым со счетчика 10, можно судить о надежности работы прибора, а их фиксация через определенные промежутки времени дает возможность строить кривые распределения сбоев, т.е. получить различные их статические характеристики. Формула изобретения Распределитель импульсов по авт. св. IP 818013, отличающийся тем, что, с цейью расиирения функциональных возможностей, в него введены соединенные последовательно дополнительный дешифратор, инвертор, дополнительный элемент И, счетчик.импульсов, и индикаторный блок, причем входы дополнительного дешифратора соединены с соответствующими выходами регистра, а другой вход дополнительного элемента И подключен к выходу элемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2688504/18-21, 03 К 17/62, 27.11.79.

Авторы

Даты

1982-04-15—Публикация

1980-07-09—Подача