ел ьо

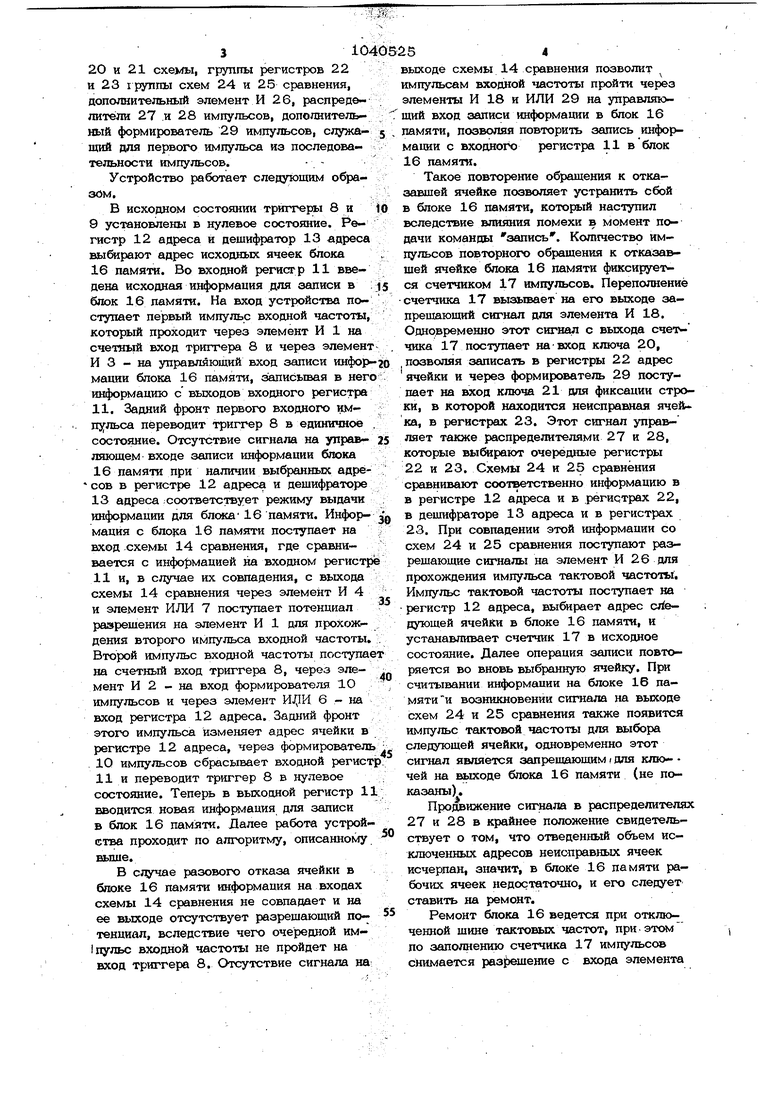

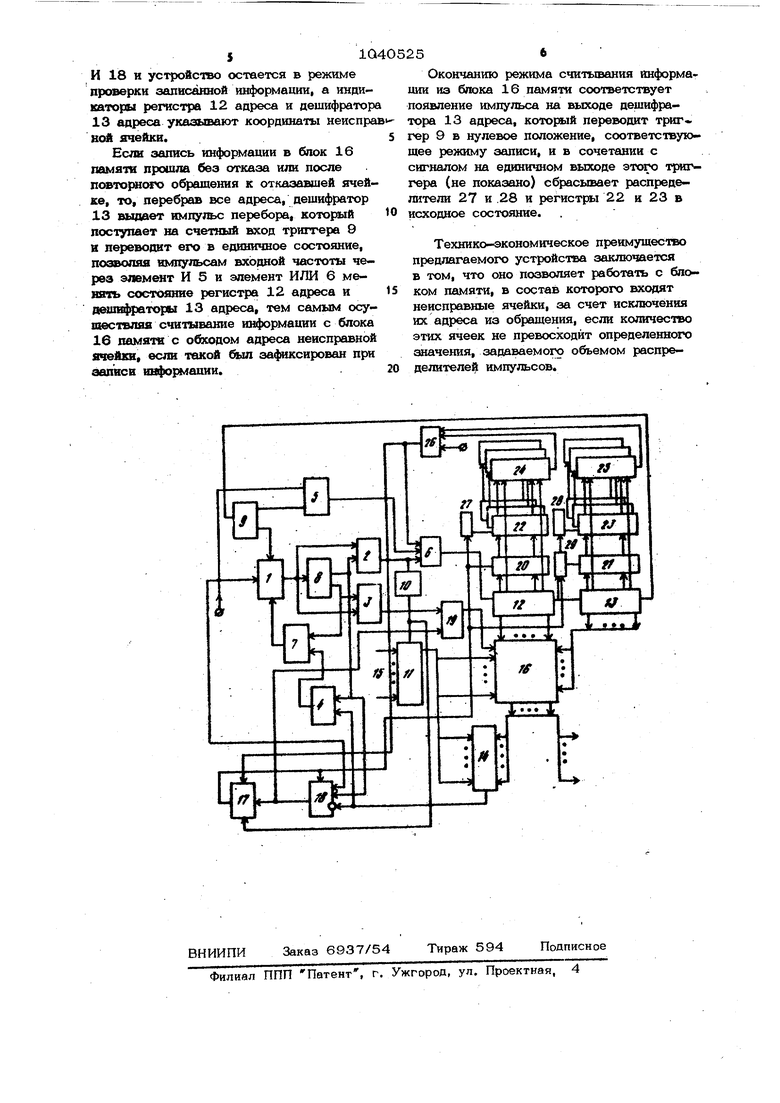

ел Изобретение относится к запоминаю дим устройствам. По основному авт. св. № 963107 иэ вестно устройство, содержащее входной регистр, регистр адреса, дешифратор, схе му сравнения, первый элемент ИЛИ, вы ход которого подключен к входу регистра Адреса, одни иэ выходов которого соединены с первыми выходами устрЬйства, а Другой выход подключен к входу дешифратора адреса, ojvm иэ выходов которого соединены с вторыми выходами устройства, выход1 1 входного регистра подклю чены к третьим выходам устройства и к одним иэ входов схемы сравнения, другие входы которого соединены с первыми входами устройства, второй элемент ИЛИ пять элементов И, два триггера и формирователь импульсов, причем второй вход устройства подключен к первым входам первого и пятого элементов И, выход первого элемента И соединен с первыми входами второго и третьего элементов И и счетным входом первого трсггера, нулевой выход которого подключен к вто pceviy входу третьего элемента И и перво му входу второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, единичный выход пер-вого триггера подключен к первому входу четвертого элемента И и второму входу второго элемента И, выход которого соединен с першлм входом первого элемент ИЛИ и входом формирователя импульсов, выход которого подключэн к одному иэ входов входного регистра, другие входы которого соединены с шинами ввода информации, выход схемы сравнения подклю чен к второму входу четвертого элемента И, выход которого соединен с вторым вхо дом второго элемента ИЛИ, другой выход дешифратора адреса подключен к сченому входу второго триггера, нулевой и единичный выходы которого соединены соответственно с третьим входом первого и входом пятсяго элементов И, выход пятого элемента И подключен к вт рому входу первогчэ элемента ИЛИ, дополнительный элемент ИЛИ, первый вход которого подключен к выходу третьего элемента И, а выход дополнительного элемента ИЛИ является четвертым выходом устройства, дополнительный элемент И, первый вход которого подключен к первому входу первого элемента И, вто рсЛ вход - к единичному выходу первого триггера, а третий вход дополнительного элемента И подключен к выходу схемы сравнения, и счетчик импульсов, первый вход которого подключен к выходу дополнительного элемента И и к второму входу дополнительного элемента ИЛИ, второй вход - к выходу формирователя импульсов, а выход счетчика импульсов подключен к четвертому входу дополнительного элемента И fl j . Однако, работа в таком устройстве прекращается при неисправности единичной ячейки памяти в блоке и нет возможности обойти адрес неисправной ячейки, что снижает надежность устройства. Цель изобретения - повышение надежности устройства за счет исключения адреса неисправной ячейки из обращения. Поставленная цель достигается тем, что в устройство для контроля блока па-, мяти введены распределители импульсов, группы регистров, ключи, группы схем сравнения, дополнительный формирователь импульсов и дополнительный элемент И, выход которого подключен к одним из входов счетчика импульсов и первого элемента ИЛИ, один из входов является входом тактовых сигналов, а другие входы соединены с выходами схем сравнения групп, одни из входов которых подключены к выходам регистров соответствующих групп, одни из входов которых соединены с выходаь4И ключей, а другие - с выходами распределителей импульсов, одни из выходов регистра адреса и дешифратора адреса соединены с одним из входов ключей и с другими входами схем сравнения соот ветствующих групп, вход первого распределителя импульсов, другой вход первого ключа и первый вход дополнительного формирователя импульсов соединены с выходом счетчика импульсов, второй вход дсшлнительного формирователя импульсов подключен к другому выходу регистра адреса, а выходы соединены с другим входом второго ключа и входом второго распределителя импульсов. На чертеже представлена структурная схема предлагаемого устройства для контроля блока памяти. Устройство для контроля блока памяти содержит элементы И 1-5, элементал ИЛИ 6 и 7, триггеры 8 и 9, фсфмирователи 10 импульсов, выходной регистр 11, регистр 12 адреса, дешифратор 13 адреса, .схему 14 сравнения, шины 15 ввода информации, соединенные через регистр 11 с контролируемым блоком 16 памяти, счетчик 17 импульсов, элемент И 18, элемент ИЛИ 19, ключи 20 и 21 схемы, группы регистров 22 и 23 группы схем 24 и 25 сравнения, дополнительный элемент И 26, распределители 27 и 28 импульсов, дополнительный формирователь 29 импульсов, служащий для первого импульса из последовательности импульсов. Устройство работает следующим образом. В исходном состоянии тригтеръ 8 и 9 установлены в нулевое состояние. Регистр 12 адреса и дешифратор 13 адреса выбирают адрес исходньк ячеек блока 16 памята. Во входной регистр 11 введена исходная информация для записи в блок 16 памяти. На вход устройства поступает первый импульс входной частоты который проходит через элемент И 1 на счетньШ вход триггера 8 и через элемен И 3 - на управляющий вход записи инфор мании блока 16 памяти, записывая в нег информацию с выходов входного регистра 11. Задний фронт первого входного TIMпульса переводит триггер 8 в единичное состояние. Отсутствие сигнала на управляющем входе записи информации блока 16 памяти при наличии выбранных адрё сов в регистре 12 адреса и дещифратрре 13 адреса соответствует режиму выдачи информации для блока 16 памяти. Информация с 16 памяти поступает на вход схемы 14 сравнения, где сравнивается с информацией на входном регистр 11 и, в случае их совпадения, с выхода схемы 14 сравнения через элемент И 4 и элемент ИЛИ 7 поступает потенциал разрешения на элемент И 1 для прохождения второго импульса входной частоты. Второй импульс входной частоты поступа на счетный вход триггера 8, через элемент И 2 - на вход формирователя 1О импульсов и через элемент ИЦИ 6 - на вход регистра 12 адреса. Задний фронт этого импульса изменяет адрес ячейки в регистре 12 адреса, через формирователь . 10 импульсов сбрасывает входной регист 11 и переводит триггер 8 в нулевое состояние. Теперь в выходной регистр 1 вводится новая информация для записи в блок 16 памяти. Далее работа устройства проходит по алгоритму, описанному выше. В случае разового отказа ячейки в блоке 16 памяти информация на входах схемы 14 сравнения не совпадает и на ее выходе отсутствует разрешающий по тенциал, вследствие чего очередной имI пульс входной частоты не пройдет на вход триггера 8. Отсутствие сигнала на; выходе схемы 14 сравнения позволит импульсам входной частоты пройти через элементы И 18 и ИЛИ 29 на управляющий вход записи информации в блок 16 памяти, позволяя повторить запись информации с входного регистра 11 в блок 16 памяти. Такое повторение обращения к отказавшей ячейке позволяет устранить сбой в блоке 16 памяти, который наступил вследствие влияния помехи в момент подачи командь запись. Количество импульсов повторного обращения к отказа&шей ячейке блока 16 памяти фиксируется счетчиком 17 импульсов. Переполнение счетчика 17 вызывает на его выходе запрещающий сигнал для элемента И 18. Одновременно этот сигнал с выхода счетчика 17 поступает на вход ключа 20, ,позволяя записать в регистры 22 адрес ячейки и через формирователь 29 поступает на вход ключа 21 для фиксации строки, в которой находится неисправная ячейка, в регистрах 23. Этот сигнал управляет также распределителями 27 и 28, которые очередные регистры 22 и 23. Схемы 24 и 25 сравнения сравнивают соответственно информацию в в регистре 12 адреса и в регистрах 22, в дешифраторе 13 адреса и в регистрах 23. При совпадении этой информации со схем 24 и 25 сравнения поступают разрешающие сигналы на элемент И 26 для прохождения импульса тактовой частоты. Импульс тактовой частоты поступает на регистр 12 адреса, выбирает адрес cjfeдующей ячейки в блоке 16 памяти, и устанавливает счетчик 17 в исходное состояние. Далее операция записи повторяется во вновь выбранную ячейку. При считывании информации на блоке 16 памяти и возникновении сигнала на выходе схем 24 и 25 сравнения также появится импульс тактовой частоты для выбора следующей ячейки, одновременно этот сигнал является запрещающим / для клю- чей на ыыходе блока 16 памяти (не показаны) . Продвижение сигнала в распределителях 27 и 28 в крайнее положение свидетельствует о том, что отведенный объем исключенных адресов неисправных ячеек исчерпан, значит, в блоке 16 памяти рабочих ячеек недостаточно, и его следует ставить на ремонт. Ремонт блока 16 ведется при отключенной щине тактовых частот, при этом по заполнению счетчика 17 импульсов снимается раз ющение с входа элемента

И 18 и устройство остается в режиме проверки записанной информации, а индикаторы регистра 12 аареса и дешифратор 13 адреса указывают координаты неиспракой ячейки.

Если запись информации в блок 16 памяти прошла без отказа или после повторн(го обращения к отказавшей ячейке, то, перебрав все адреса, дешифратор 13 выдает импущ с перебора, который поступает на счетный вход триггера 9 и переводит его в единичное состояние, позвопяя импульсам входной частоты через элемент И 5 и элемент ИЛИ 6 менять состояние регистра 12 адреса и 13 адреса, тем самым осуществляя считывание )ормации с блока 16 памяти с обходом адреса неисправной 1пейки, если такой был за4мксирован при записи информации.

Окончангао режима считывания информации из бтзка 16 памяти соответствует появление импульса на выходе дешифратора 13 адреса, который переводит триг гер 9 Б нулевое положение, соответствующее режиму записи, и в сочетании с сигналом на единичном выходе этого триггера (не показано) сбрасывает распределители 27 и 28 и регистры 22 и 23 в исходное состояние.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно позволяет работать с блоком памяти, в состав которого входят неисправные ячейки, за счет исключения их адреса из обращения, если количество этих ячеек не превосходит определенного значения, задаваемого объемом распределителей импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПАМЯТИ п6 авт. св. № 963107, отличающееся тем, что, с целью повышения его надежности, в него введены распределители импульсов, группы регистров, ключи, группы схем сравнения, дополнительный формирователь импульсов и дополнительный элемент И, выход которого подключен к одним из входов счет- чика импульсов и первого элемента ИЛИ, один из входов является входом тактовых сигналов, а другие входы соединены с выходами схем сравнения групп, одни из входов которых подключены к выходам регистр соответст ющих групп, одни из входов которых соединены с выходами ключей, а другие - с выходами распределителей импульсов, одни из выходов регистра адреса и дешифратора адреса соединены с одним из входов ключей и с другими входами схем сравнения соот ветствующих групп, вход первого распределителя импульсов, другой вход первого ключа и первый вход дополнительного формирователя импульсов соединены с выходом счетчика импульсов, второй вход дополнительного формирователя импульсов подключен к другому выходу регистра (Л адреса, а выходы соединены с другим входом второтч) ключа и входом второго распределителя импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

Авторы

Даты

1983-09-07—Публикация

1981-03-12—Подача