Изобретение относится к вычислительной технике, в частности к эапоминающим устройствам, и может быть использовано в -факсимильной технике связи.

Целью изобретения является увеличение информационной емкости устройства.

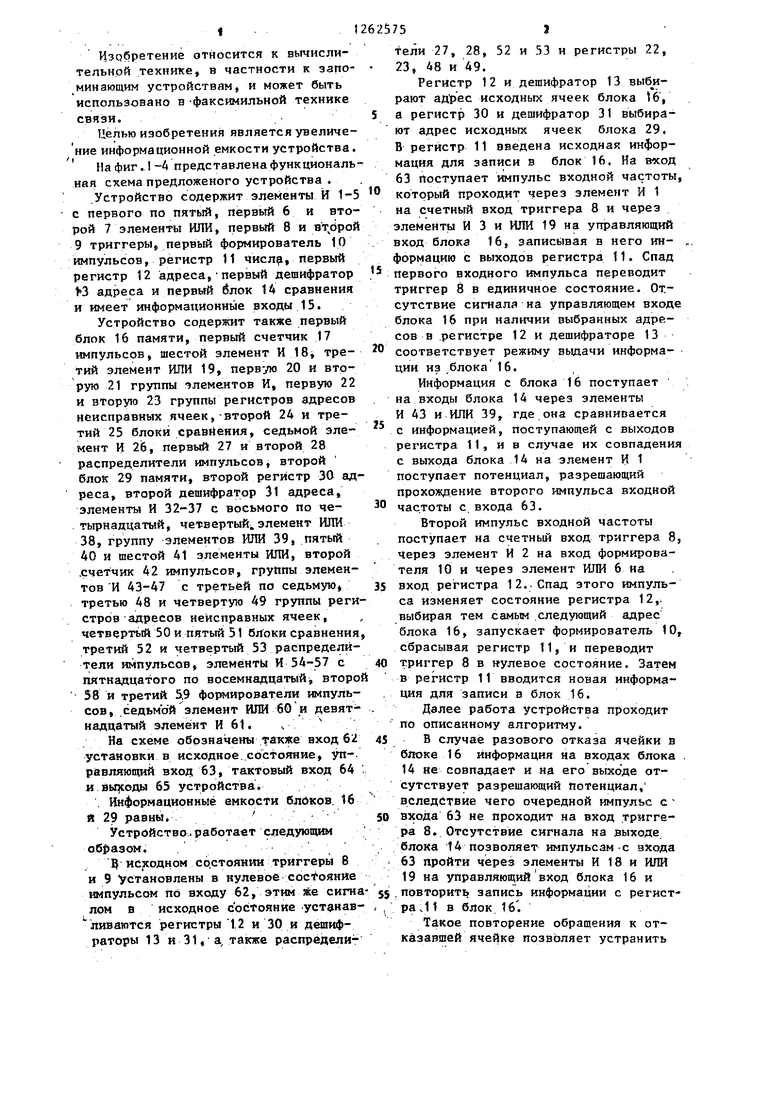

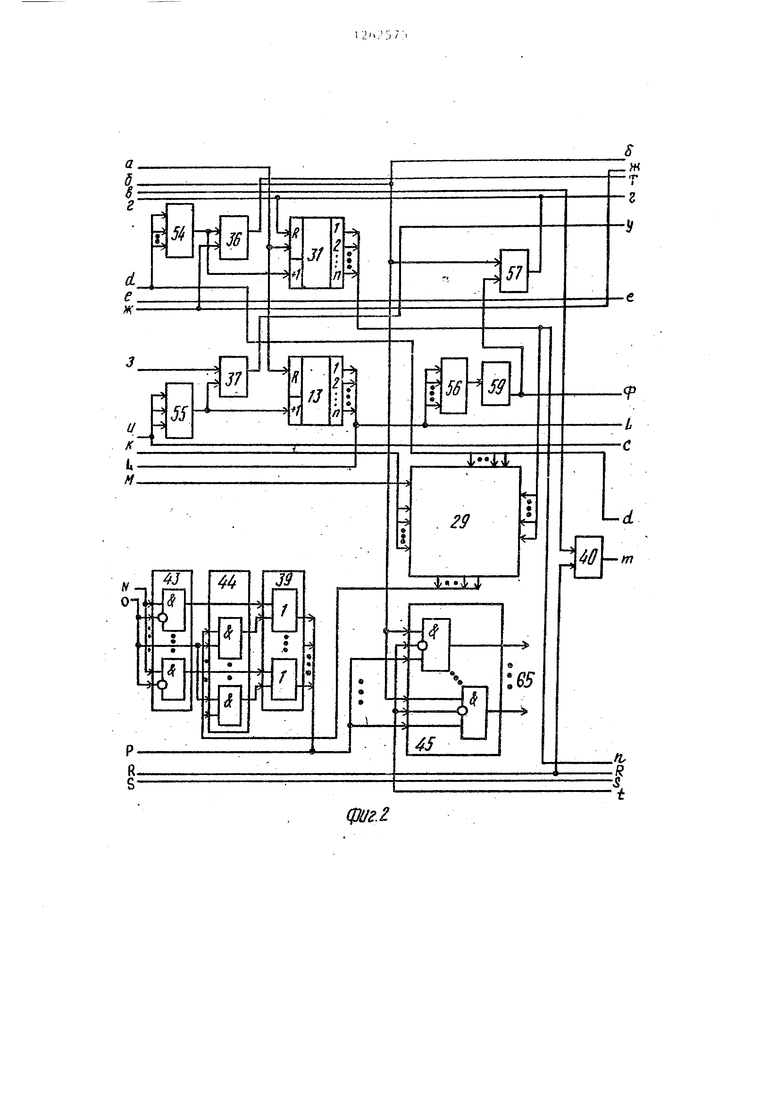

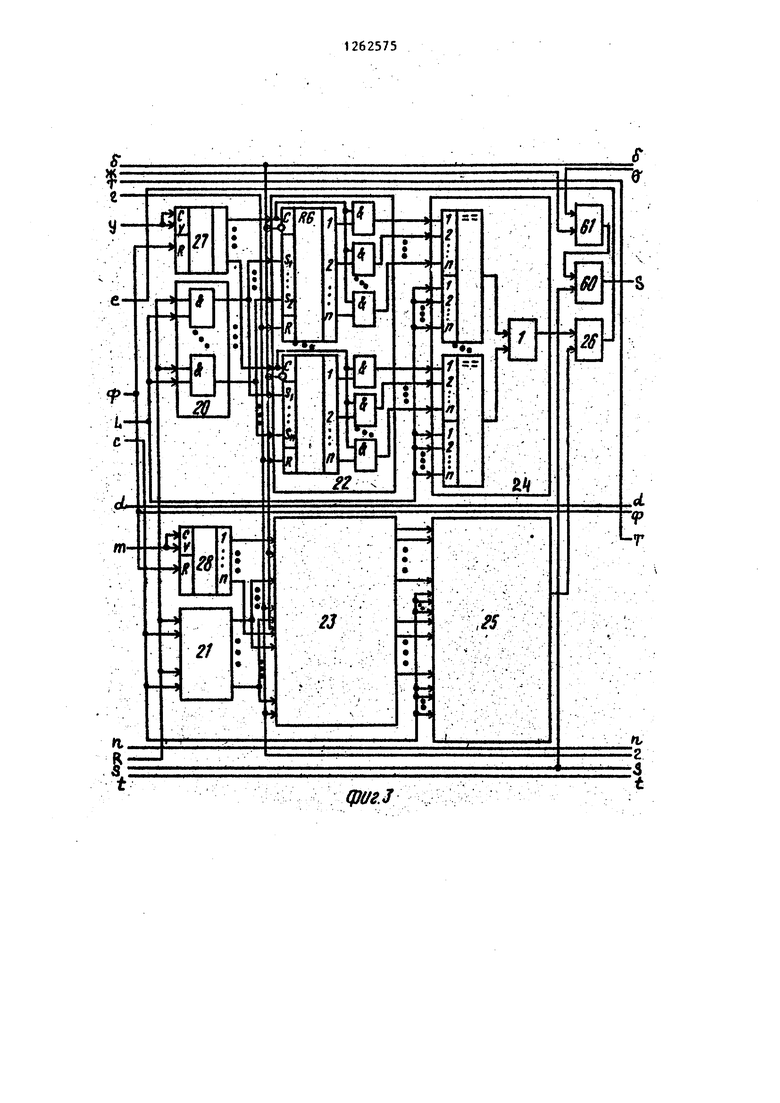

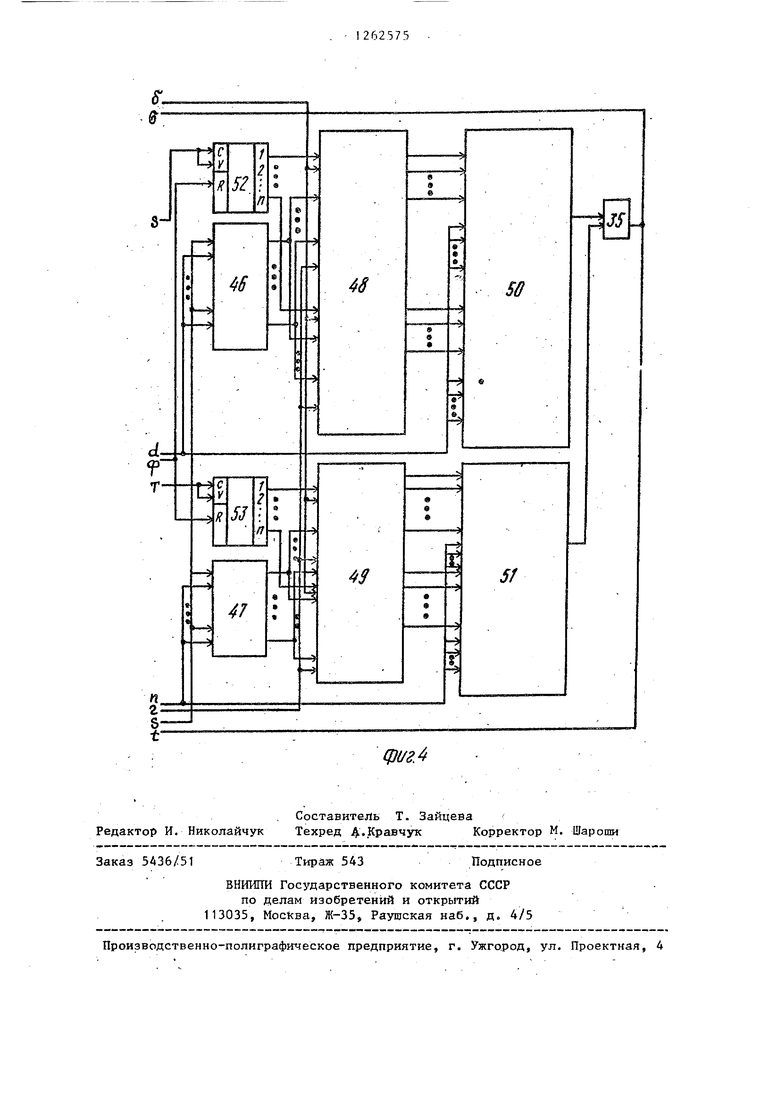

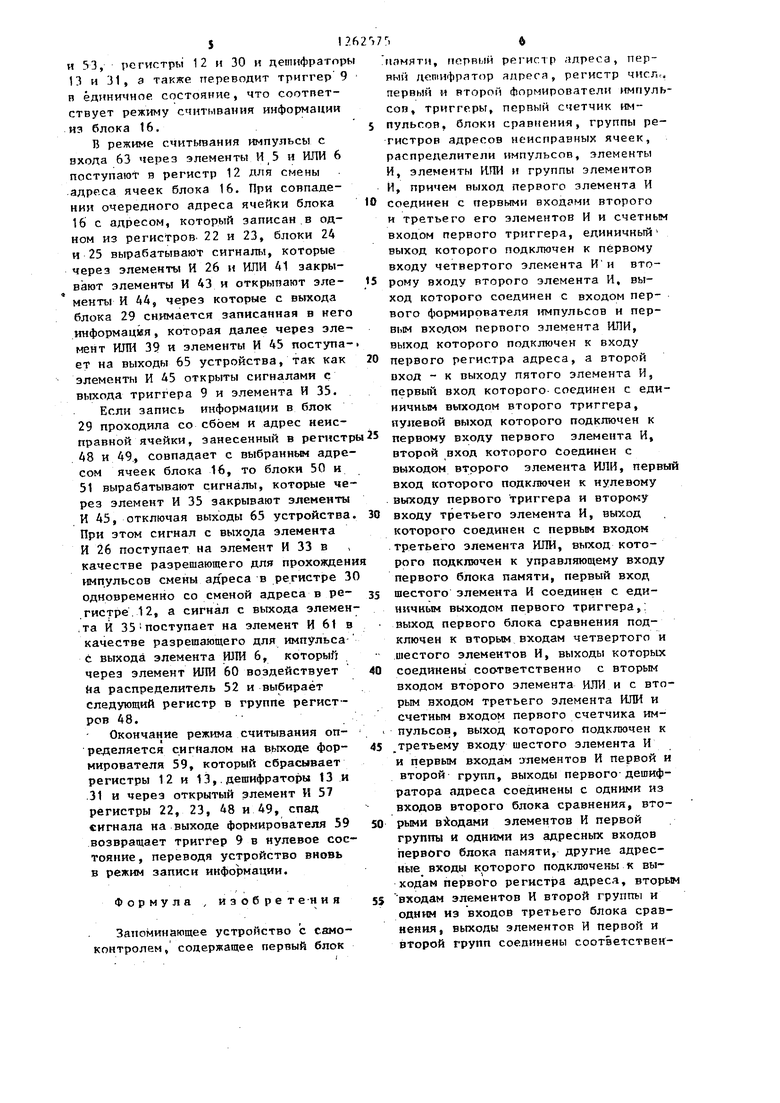

На фиг .1-4 представлена функциональная схема предложеного устройства .

Устройство содержит элементы И с первого по пятый, первый 6 и второй 7 элементы ИЛИ, первьгй 8 и 9 триггеры, первьй формирователь 10 импульсов, регистр И числ, первый регистр 12 адреса, первый дешифратор Ю адреса и первый блок 14 сравнения и имеет информационные входы 15.

Устройство содержит также первый блок 16 памяти, первый счетчик 17 импульсов, шестой элемент И 18 третий элемент ИЛИ 19, перв-ую 20 и вторую 21 группы элемеятов И, первую 22 и вторую 23 группы регистров адресов неисправных ячеек,-второй 24 и третий 25 блоки сравнения, седьмой элемент И 2i6, первый 27 и второй 28 распределители импульсов второй блок 29 памяти, второй регистр 30 адреса, второй дешифратор 31 адреса, элементы И 32-37 с восьмого по четьфнадцатый, четвертый элемент ИЛИ 38, группу элементов ИЛИ 39, пятый 40 и шестой 41 элементы ИЛИ, второй .счетчик 42 импульсов, группы элементов И 43-47 с третьей по седьмую, третью 48 и четвертую 49 группы регистров адресов неисправных ячеек, четвертый 50 и пятый 51 блоки сравнения третий 52 и четвертый 53 распределители иИпульсов, элементы И 54-57 с пятнадцатого по восемнадцатый, второ 58 и третий 5,9 формирователи импульсов, седьмой элемент ИЛИ 60 и девят надцатый элемент И 61. ч

На схеме обрзначени также вход 62 установки в исходное .состояние, уп-. рдвляюпщй вход 63, тактовый вход 64 и выводы 65 устройства.

. Информационные емкости бликов. 16 и 29 равны.

Устройство.работает следующим образом.

Э исходном состоянии триггеры 8 и 9 установлены в нулевое сое ояние импульсом по входу 62, этим йсе сигна лом в исходное состояние устанавливаются регистры 1,2 и 30 и дешифраторы 13 и 31, а, также распределители 27, 28, 52 и 53 и регистры 22, 23, 48 и 49.

Регистр 12 и дешифратор 13 выб рают адрес исходных ячеек блока 16, а регистр 30 и дешифратор 31 выбирают адрес исходных ячеек блока 29. В регистр 11 введена исходная информация для записи в блок 16. На вход 63 поступает импульс входной частоты который проходит через элемент И 1 на счетный вход триггера 8 и через элементы И 3 и ИЛИ 19 на управляющий вход блока 16, записывая в него информацию с выходов регистра 11. Спад первого входного импульса переводит триггер 8 в единичное состояние. Отсутствие сигналя на управляющем вход блока 16 при наличии выбранных адресов в регистре 12 и дешифраторе 13 соответствует режиму выдачи информации из блока 16.

Информация с блока 16 поступает на входы блока 14 через элементы И 43 и ИЛИ 39, где она сравнивается с информацией, поступающей с выходов регистра 11, и в случае их совпадени с выхода блока 14 на элемент И 1 поступает потенциал, разрешающий прохождение второго импульса входной частоты с входа 63.

Второй импульс входной частоты поступает на счетный вход триггера 8 через элемент И 2 на вход формирователя 10 и через элемент ИЛИ 6 на вход регистра 12..Спад этого импульса изменяет состояние регистра 12,. выбирая тем самым следующий адрес блока 16, запускает формирователь 10 сбрасывая регистр 11, и переводит триггер 8 в нулевое состояние. Затем в регистр 11 вводится новая информация для записи в блок 16.

Далее работа устройства проходит по описанному алгоритму.

В случае разового отказа ячейки в блоке 16 информация на входах блока 14 не совпадает и на его выходе отсутствует разрешающий Потенциал, вследствие чего очередной импульс с входа 63 не проходит на вход триггера 8. Отсутствие сигнала на выходе блока 14 позволяет импульсам-с входа 63 пройти через элементы И 18 и ИЛИ 19 на управляющий вход блока 16 и ,повторить запись информации с регистра; 1 в блок 16.

Такое повторение обращения к отказавшей ячейке позволяет устранить сбой в блоке 16, который наступил вследствие влияния помехи в момент сигнала на управляющий вход блока 1 Количество импульсов повториого обращения к отказавшей ячейке блока 16 фиксируется счетчиком 17, переполнение которого вызывает на его выходе запрещающий сигнал для элемента И 18, при этом обращение к бл ку через элемент И 3 прекращается, разрешается прохождение импульсов тактовой ««:астоты с входа 64, которые поступают на управляющий вход блока 29, записывая в него информацию с регистра 11. Х)дновременно с игнап с выхода сче чика ,17 поступает на разрешающие входы элементов И 20 и 21, записыва /в регистры 22 и.23 адрес неисправно ячейки блока 16. Неисправность ячей ки блока памяти может характеризоваться также выходом из строя ключе (не показан), подключающих ячейку памяти к выходу, блока памяти и входящих в состав микросхем, на которы построен .блок памяти. Количество импульсов обращения к блоку 29 фиксируется счетчиком 42. Сигнал переполнения счетчика 17 через- элемент ИЛИ 41 закрьтает элементы И 43 и открывает элементы И 44, к которым подводится информация с выхода блока 29 для контроля правильности записи информации в него, пос редством сравнения в блоке 14 инфор мации на выходе блока 29 и информац на выходе регистра 11, Если запись информации в блок 29 прошлабез сбоев, то на выходе блока 14 появляется сигнал, который через элемент И 4 и элемент ИЛИ 7 поступает на элемент И 1 в качестве разрешающего для прохождения импуль са смены адреса в блоке 16 через элементы И 2 или ИЛИ бив блоке 29 через элементы И 32 и ИЛИ 38, одновременно импульсы с выхода элемента И 32 через формирователь 58 устанавливают в исходное состояние счетчики 17 и 42, а спад импульса с выхода элемента И 2 через формировател 10 сбрасывает регистр 11. При установке счетчика 17 в исход ное состояние исчезновение сигнала переполнения счетчика 17 через элемент ИЛИ 40 воздействует на распределитель 28, с помощью которого выбирается очередной регистр из регист 754 ров 23. -Дешифрптор 13 измпияоч ci;oe состояние под воздейстпипм сипглла с выхода элемента И 55, который фпксирует момент переполнения регистра 12 и тем самым выбирает новую группу ячеек памяти блока 16. Распределитель 27 выбирает новый регистр в группе регистров 22 сигналом с выхода элемента И 32, кото- . рый проходит через элемент И 37 в момент фиксации переполнения регистра 12. ., Далее работа устройства проходит по описанному алгоритму при обращении к блоку 16 памяти. Если запись информации в блок 29 происходит со сбоями и появляется сигнал пeJ eпoлнeния счетчика 42,то , этот сигнал поступает на элементы И 46 и 47, через которые в соот- ветствующие из регистров 48 и 49 записывается адрес неисправной ячей- . ки блока 29, спад .этого сигнала через элемент И 3 воздействует на регистр 3Q, выбирая о51ередную ячейку блока 29, и через элемент ИЛИ 60 воздействует на распределитель 52, выбирая новый регистр в группе регистров 48 для записи адреса ячейки блока 29, если она окажется неисправной. Обра щение- к блоку 29 продолжается до момента записи информации в него без сбоя. Если при записи информации в блок 29 все ячейки перебраны, то появляется сигнал на выходе дешифратора 31, который воспринимается как сигнал отказа, указывающий на то, что сохранить рабочий объем памяти блока 16 за счет ячеек блока 29 невозможно, и блоки 16 и 29 памяти следует ремонтировать или заменить на другие. При :ремонте: блока 16 отключается от входа 6$источник тактовых импульсов, при заполнении счетчика 17 снимается разрешение с соответствующего элемента И 18 и устройство остается режиме проверки записанной инфорации, а индикаторы (не показаны) егистров 12 и дешифратора 13 указыают координаты неисправной ячейки. Выбор последнего адреса ячейки лока 16 при записи информации в него иксируется элементом И 56, при этом а его выходе появляется сигнал, оторый по спаду запускает формироатель 59, импульс с выхода которого брасывает распределители 27, 28, 52 S и 53, pervfCTpbi 12 и 30 и дешифрато О и 31, э также переводит триггер и единичное состояние, что соотпетствует режиму считывания информации из блока 16. В режиме считывания импульсы с входа 63 через элементы И 5 и ИЛИ 6 поступают в регистр 12 для смены адрр-са ячеек блока 16. При совпадении очередного адреса ячейки блока 16 с адресом, который записан.в одном из регистров 22 и 23, блоки 24 и 25 вырабатывают сигналы, которые через элементы И 26 и ИЛИ 41 закрывают элементы И 43 и открыпают элементы И 44, через которые с выхода блока 29 снимается записанная в нег информация, которая далее через эле мент ИЛИ 39 и элементы И 45 поступа ет на выходы 65 устройства, так как элементы И 45 открыты сигналами с выхода триггера 9 и элемента И 35. Если запись информации в блок 29 проходила со сбоем и адрес неисправной ячейки, занесенный в регист 48 и 49, совпадает с выбранным адре сом ячеек блока 16, то блоки 50 и 51 вырабатывают сигналы, которые че рез элемент И 35 закрывают элементы И 45, отключая выходы 65 устройства При этом сигнал с выхода элемента И 26 поступает на элемент И 33 в качестве разрешающего для прохожден импульсов смены адреса в регистре одновременно со сменой адреса в регистре.12, а сигнал с выхода элемен ,та И 35поступает на элемент И 61 качестве разрешающего для импульса с выхода элемента ИЛИ 6, который через элемент ИЛИ 60 воздействует ha распределитель 52 и выбирает следующий регистр в группе регистров 48. Окончание режима считывания определяется сигналом на выходе формирователя 59, который сбрасывает регистры 12 и 13,.дешифраторы 13 и .31 и через открытый элемент И 57 регистры 22, 23, 48 и 49, спад сигнала на выходе формирователя 59 возвращает триггер 9 в нулевое сос тояние , переводя устройство вновь в режим записи информации. Формула , изобретения Запоминающее устройство с самоконтролем, содержащее первый блок памяти, первый региглр адреса, первый дешифратор адреса, регистр числе. первый и втором формирователи импульсоп, триггеры, первый счетчик импульсов, блоки сравнения, группы регистров адресов неисправных ячеек, распределители импульсов, элементы И, элементы ИЛИ и группы элементов И, причем выход первого элемента И соединен с первыми входами второго и третьего его элементов И и счетным входом первого триггера, единичный выход которого подключен к первому входу четвертого элемента И и второму входу второго элемента И, выход которого соединен с входом первого формирователя 1тмпульсав и первым входом первого элемента ИЛИ, выход которого подключен к входу первого регистра адреса, а второй вход - к выходу пятого элемента И, первьпЧ вход которого- соединен с единичньм выходом второго триггера, нулевой выход которого подключен к первому входу первого элемента И, второй вход которого Соединен с выходом второго элемента ИЛИ, первый вход Которого подключен к нулевому выходу первого триггера и второку входу третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к управляющему входу первого блока памяти, первый вход шестого элемента И соединен с единичным выходом первого триггера,; выход первого блока сравнения подключен к вторым входам четвертого и шестого элементов И, выходы которых соединены соответственно с вторым входом второго элемента ИЛИ и с вторьт входом третьего элемента ИЛИ и счетным входом первого счетчика импульсов, выход которого подключен к третьему входу шестого элемента И и первым входам элементов И первой и второй групп, выходы первого дешифратора адреса соединены с одними из входов второго блока сравнения, вторыми в: одами элементов И первой группы и одними из адресных входов первого блока памяти, другие адресные входы которого подключены к выходам первого регистра адреса, вторым входам элементов И второй группы и одним из входов третьего блока сравнения , выходы элементов И первой и второй групп соединены соответствен7но с одними из входов регистров адресов неисправных ячеек первой и второй групп, выходы которых подключены соответственно к другим входам второго и третьего блоков сравнения, выходы которых соединены с входами сед мого элемента И,выход первого формиро бателя импульсов подключен к перво установочному входу первого счетчик импульсов и одному из входов регист ра числа выходы которого соединены одними из входов первого блока ; сравнения и числовыми входами первого блока памяти, другие входы регистра числа являются ииформационными входами устройства, второй вхо пятого элемента И, третьи входы пер вого и шестого элемечтов И являются управлянщим входом устройства, о тл и ч а ю щ в е с я тем, что, с цв лью увеличения информационной емкос устройства, в него введены второй блок памяти, второй регистр адреса, второй дешифратор адреса, второй счетчик импульсов, третий формиройа тель импульсов, третья и чертвертая группы регистров адресов неисправных ячеек, четвертый и пятый блоки срав нения, третий и четвертый распредели тели импульсов, группы элементов И с третьей по седьмую, группа элементов ИЛИ, элементы И с восьмого по девятнадцатий и элементы ИЛИ с четвертого по седьмой, причем первые входы пятого и седьмого элементов ИЛИ, восьмого и десятого элементов И соединены с выходом первого формирователя импульсов, второй вход восьмого элементв И подключен к выходу первого элемента И, а выход к в5соду второго формирователя импуль сов, первйму входу тринадцатого элемента И и первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И и вторым входом пятого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к входу второго регистра адреса, выходы которого соединены с входами пятнадцатого элемента И, первыми входами элементов И шестоЯ группы, одними из входов третьего блока сравнения и одними иа адресных входов второго блока памяти, другие адресные входы которого подключены к выходам второго дешифратора адреса первым входам элементов И седьмой группы и одним из входов четвертого 758 блока сравнения, выходы третьеIo и четвертого блоков сравнепия сооди(1еяы с входами одиннадцатого элемента И, а другие входы - с выходами реристров адресов неисправных ячеек третьей и четвертой групп соответственно, одни из входов которых подключены к выходам элементов И шестой и седьмой групп соответственно, вторые входы которых, первый вход седьмого элемента ИЛИ и TpeTira вход четвертого элемента ИЛИ соединены с выходом второго счетчика импульсов, счетный вход которого подключен к выходу десятого элемента И и управляющему входу второго блока памяти, информационные входы которого соединены с выходами регистра числа, а выходы - с первыми входами элементов И четвертой группы, выходы которых подключены в первым входам элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И третьей группы, первые входы которых подключены к выходам первого блока памяти, вторые входь элементов И третьей и четвертой групп соединены с выходом шестого элемента ИЛИ, второй вход которого и первый вход девятого элемента И подключены к выходу седьмого элементаИ, выход пят-, надцатого элемента И соединен с входом второго дешифратора адреса . и первым входом двенадцатого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ и первому входу девятнадцатого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ, выход которого подключен к первому входу третьего распределителя импуль сов, выход двенадцатого элемента И соединен с первым вгиэдом четвертого распределителя импульсов, выходы . третьего и четвертого распределителей импульсов подключены соответс венно ,к другим входам регистров адресов неисправных ячеек третьей и четвертой групп, выход одинадцатого элемента И соединен с втод1-м входом Двенадцатого элемента И и первыми входами элементов И пятой группы, вторые входы которых подключены к ыходам элементов ИЛИ группы и другим входам первого блока сравнения, ходы шестнадцатого элемента И соеинены с выходами первого регистра дреса, а выход подключен к входу

первого дешифратора адреса и второму входу тринадцатого элемента И, вы.ход которого и выход пятого элемента ИЛИ соединейы с первыми входами первого и второго распределителя импуль« сов соответственно, входы семнадцатого И подключены к выходам первого дешифратора адреса, а выход пбдключен к входу третьего формирователя импульсов, выход которого соединен с первым входом восемнадцатого элемента И и вторыми входами распределителей импульсов, , выход второго формирователя импульсов подключен к второму установочному входу первого счетчика импульсо и установочному входу второго счетчика импульсовj выход восемнадцатого элемента И соединен го счетным

входом второго триггера, управляющими входами второго регистра адреса, первыми установочньми входами второго дешифратора адреса и регистров адресов неисправных ячеек групп, ( вторые установочные входы которых, второй вход восемнадцатого элемента Ни третьи входы элементов И пятой группы подключены к единичному выходу

второго триггера, установочные входы триггеров, первого регистра адреса -и первого дешифратора адреса, вторые установочные входь второго регистра адреса и второго дешифрато ра адреса являютсявходом установки в исходное состояние устройства, тактовым входом и выходами которого , являете я в торой вхйд десятого элемента И и выходы элементов И пятой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Устройство для контроля блока памяти | 1981 |

|

SU1040525A2 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

Изобретение относится к вьтчислительной технике, в частности к эапо.мннающим устройствам, и может быть использовано в факсимильной технике связи. Целью изобретения является увеличение информационной емкости устройства. Устройство содержит первый блок памяти, два формирователя импульсов, два триггера, первый регистр числа, первый- регистр адреса, первый дешифратор адреса, три блока сравнения, первый счетчик импульсов, два распределителя импульсов, две группы регистров адресов неисправных ячеек, две группы элементов И, смесь элементов И, три элемента ИЛИ, а также вновь введенные второй блок памяти, второй регистр адреса, второй дешифратор ддреса, группы элементов И с .третьей- по седьмую, второй счет.чик импульсов, третью и четвертую группы регистров адресов неисправных ячеек, четвертый и пятый блоки сравнения, третий и четвертый распределители импульсов, третий формирователь импульсов, группу элементов ШШ, элементы И с восьмого по двенадцатый и элементы ИЛИ с четвертого по седьмой. Увеличение информационной ем-кости устройства достигается аа счет того, что при отказе ячейки в первом блоке памяти информация записыс вается на второй блок памяти. Контроль состояния ячеек блоков памяти выполняется путем сравнения записанс ной и считанной информации. Обеспечено неоднократное повторное обращение к отказавшей ячейке в обоих блоках памяти для устранения случайного сбоя вследствие влияния помехи и ю Ф ю ел выявления действительно дефектной ячейки памяти. Число повторных обращений к блокам памяти ограничено переполнением счетчиков импульсов. « 4 ил.

Фиг.1

да./

| Аналоговое запоминающее устройство | 1981 |

|

SU963106A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 10405256 кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-06—Подача