Изобретение относится к вычислггтельной технике и может быть использовано в многомашинных вычислительных системах.

Известны устройства для сопряжения, содержащие два регистра, два триггера, элемент запрета, элементы И и ИЛИ, формирователь импульсов и элемент задержки l .

Недостаток этих устройств состоит в ограниченных функциональных возможностях, так как они обеспечивают однонаправленную передачу (прием) информации, что не позволяет на вычислительной системе параллельно решать, например, задачи математической физики методом конечных разностей, потому, что при параллельном выполнении этого алгоритма необходимо, чтобы каждая ЦВМ, входящая в систему, обменивалась информацией, по крайней мере, с двумя, соседними ЦВМ.

Наиболее близким по технической сущности к изобретению является устройство для сопряжения, содержащее элемент И, ИЛИ, элемент запрета, регистр и триггер, единичный выход которого подключен к запрердающему входу элемента запрета, соединенного

основным входом с выходом первого элемента ИЛИ, второй вход первого элемента И соединен с выходом второго элемента ИЛИ, выход элемента запрета соединен с первым управляющим входом регистра, выходом управле- . ния обменом устройства и с первым входом второго элемента И, подключенного своим выходом к единичному

10 входу триггера, нулевой вход которого соединен через формирователь импульса с выходом второго элемента ИЛИ, входы первого и второго элементов ИЛИ, второй вход второго элемен15та И и второй управляющий вход регистра соединены с соответствующими управляющими входами устройства, информационные входы и выходы регистра соединены с информационными вхо20дами и выходами устройства 1 .

Недостаток известного устройства ограниченные функциональные возможности, обусловленные однонаправленной передачей информации.

25

Цель изобретения - расагшрение функциональных возможностей устройства путем обеспечения двухнаправленного обмена.

Поставленная цель достигается тем,

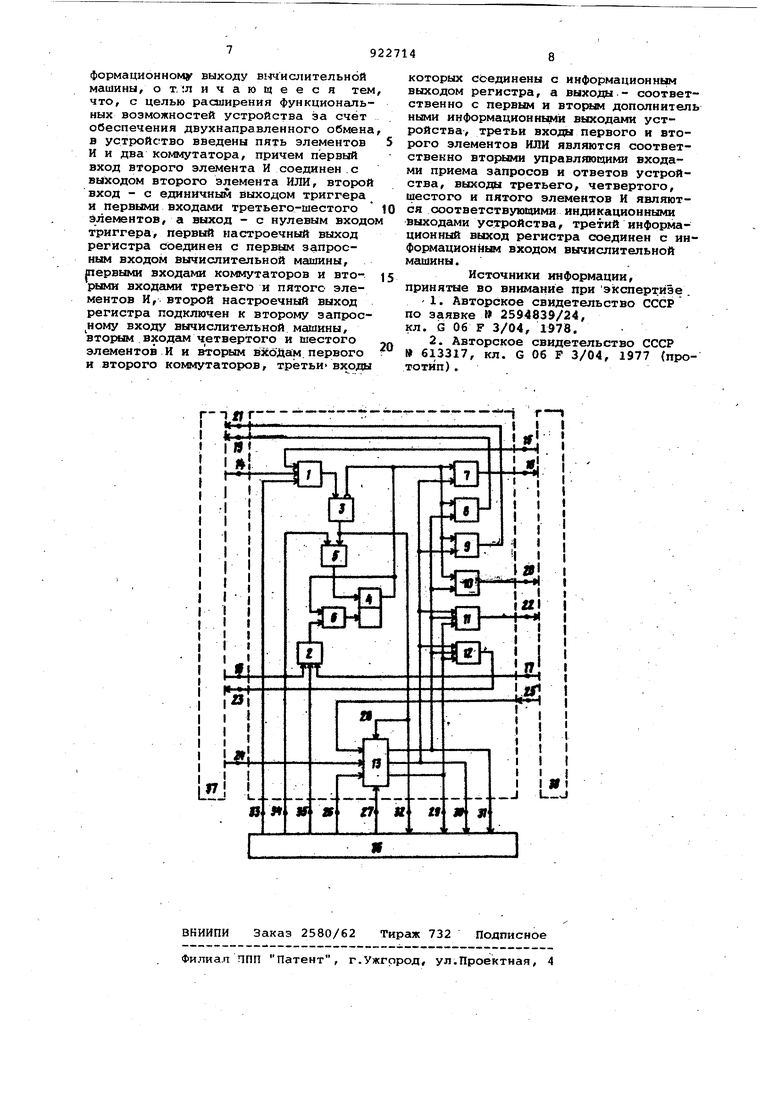

30 что в устройство, содержащее первый элемент И, два элемента ИЛИ, элемент запрета, регистр и триггер, единичный выход которого подключен к запре щающему входу элемента запрета/ Подключенного основным входом к выходу первого элемента ИЛИ, а выходом |К первому управляющему входу регистра, выходу управления обменом устрой ства и первому входу первого элемента И, подключенного- выходом к единич ному входу триггера, первые и вторые входы первого и второго элементов ИЛИ, второй вход первого элемента И и второй управляющий вход регистра соединены соответственно с первыми управляющими входами приема запросов и ответов, первым, вторым и третьим входами задания режима и входом управления выбором направления приема информации устройства, первый и второй информацио1|ные входы и информационный выход регистра подключены соответственно к первому и второму информационным входам и инфо 1ационному выходу устройства, введены пять /элементов И и два коммутатора, приче первый вход второго элемента И среди нен с выходом зторого элемента ИЛИ, (второй вход - с единичным выходом тр гера и первыми входами третьего шестого элементов И, а выход - с ну левым входом триггера, первый настроечный выход регистра сое,цинен U первым настроечным выходом устройст ва, первыми входами коммутаторов и вторыми входами треЛего и пятого элементов И второй настроечный выход регистра подключен к второму на строечному выходу устройства, вторым входам четвертого и шестого элементов И и вторым входом первого и второго коммутаторов, третьи входы которых соединены с информационным выходом регистра, а выхода - соответственно с первым и вторам дополни тельными информационными выходами устройства, третьи входы первого и второго элементов ИЛИ являются соответственно вторыми управлдюЕЩМи входами приема и ответов устройства, выходы третьего, четвер того, шестого и пятого элементов И являются соответствующими индикатор ными выходами устройства, третий информационный вход регистра являет ся третьим информационным входом устройства. На чертеже представлена блок-схе ма устройства. Устройство содержит элементы ИЛИ 1 и 2, элемент 3 запрета, триггер 4 элементы И 5 -10 (элементы И 7-10 образуют группу элементов И), комму туторы 11 и 12, регистр 13, первый и второй управляющие входы 14 и 15 устройства приема запросов, первый ;И второй управляющие входы 16 и 17 устройства приема ответов, первый 1и второй индикаторные выходы 18 и 19 устройства для передачи запросов соответственно на входы 1,4 и 15 со седних устройств третий и четвертый; индикаторные выхода 20 и 21 устройства для передачи ответов соответственно на входы 16 и 17 соседних устройств, первый и второй дополнительные информационные выходы 22 и j23 устройства, первый и второй информационные входы 24 и 25 для приема инфо 1ации с выходов 22-И 23 соседних устройств, третий информационный вход 26 устройства, вход 27 устройства управления выбором направления приема информации, первый управляющий вход 28 регистра для управлег; ния приемом информации в регистр 13, информационный выход 29 устройства, настроечные выхода 30 и 31 устройства, выход 32 управления обменом устройства, первый, третий и второй входы 33-35 задания режима устройства, вычислительную машину 36, аналогич- . ные устройства 37 и 38 сопряжения сопрягаемых вычислительных машин. Устройство работает следующим обраэом. Передача информации. Вычислительная машина 36 является передающей. На входы 33 и 34 она выдает сигнал 1, а на вход 35 - сигнал О. Перед началом работы триггеры 4 всех устройств 37 сопряжения устанавливаются в нулевое состояние сигналами по входам 35, поступгцощими с выходов соответствующих вычислительных магшин. На выходе .элемента запрета после подачи сигнала вход 33 устанавливается сигнал 1, который по выходу 32 разрешает передачу информации из вычислительной машины 36, а по входу 28 - прием информации в регистр 13, поступающей по входу 26 (предполагается, что регистр передающей машины по входу 27 установлен на прием информации с входа 26, а регистры 13 принимающих машин установлены на прием информации с входов 24 и 25}. &1ХОДНЫМ сигналом элемента 3. запрета осуществляется также установка триггера 4 в единичное состояние. Выбор направления передачи управляющих индикаторных сигналов (Запросов и Ответов) и информации с регистра 13 осуществляется с помощью сигналов, поступающих с настроечных выходов регистра 13 на входы коммутаторов 11 и 12 и элементов И 7-10. При и информация с регистра 13 поступает на выход 22 и далее на вход 24 устройства 38, а единичный сигнал Запрос с выхода триггера 4 поступает на выход 18.и далее на вход 14 устройства 38 и, если его триггер 4 находится в нулевом состоянии, эапускает это устройство на прием информации {С и Ct соответственно сигналы на первом и втором настроечных выходах регистра 13) . После записи информации в регистр устройство 38 выдает на вход 17 сигнал 1 ( Ответ ), под действием которого триггер 4 устанавливается в О. На выходе элемента 3 запрета возникает сигнал ., который снова устанавливает сигнал 1 на выходе 32для вычислительной мгоиины 36 О Еозможности записи в регистр 13 очередного слова. Устройство 38 принимает очередное слово в свой ре,гистр только тогда, когда предыду.адее слово принято вычислительной машиной этого устройства, если оно работает в режиме приема информации, или передано дальше, если оно работа ет в качестве ретранслятора. Прием информации. Вычислительнай машина 36 на вход 33 выдает сигнал О, устанавливает триггер 4 по входу 35 в О,а регистр 13 по входу 27 - на прием информации по входам 2 и 25. do сигналу с выхода элемента запрета, появляющемуся при подаче на вход 14 (или 15) сигнала 1, осуществляется прием информации в регистр 13. Этот же сигнал по входу 32 запускает вычислительную машину 36 на прием информации с выходов 29-31 После приема информации вычислительная машийа 36 по входу 34 устанавливает тЕ)Иггер 4 в единичное состояние Сигнал 1 с выхода триггера 4 посту пает на выходы 18 и 21 при С i и (если на выходы 19 и 20 при и ) и далее на входы 14 и 17 (или на входы 15 и 16) соседних устройств. Триггер 4 соседнего устройства, от которого была принята информация, устанавливается в О, М другое соседнее устройство запускается на прием информации, если его триггер 4 находится в нулевом состоянии. Осуществив прием информации, соседнее устройство по входу 16 или 17 (в зависимости от направления движения информации) переключает триггер 4 в нулевое состояние и тем самыгя разрешает прием следующего сло Ретрансляция информации. Вычислительная машина 36 в этом режиме работы является транзитной по передаче информации. На каждый из входов 33и 35 она выдает сигнал О, на вход 34 - сигнал 1, а регистр 13 п входу 27 устанавливает на прием .информации с входов 24 и 25. При поступлении сигнала 1 на вход 14 (или 15) осуществляется прием информации в регистр 13 и установка триг,гера 4 в единичное состояние. Сигнал 1 с выхода триггера поступает на входы элементов И 7-10 и далее На вы ходы 18 и 21, если и , или на выхода 19 и 20, если и . После приема информации соседнее устройство вырабатывает сигнал 1, который по входу 17 или 16 ( в зависимости от направления движения информации) переключает триггер 4 в состояние ,|0 и тем самым разрешает прием очередного слова в регистр 13. . Из описанных режимов работы устройства следует, что оно может находиться в одном из следующих состоя|ний: Передача информации правому соПередача информации левому соседу и Прием информации от правого или левого соседей. Следовательно,цепочка устройств может быть непосредственно использована в качестве асинхронного запоминающего устройства с линейной организацией, а также для построения двухнаправленной двухмерной однородной структуры, которая может выполнять функции асинхронного запоминающего устройства с двухмерным доступом (по вертикали и горизонтали). Таким -образом,. предлагаемое устройство позволяет осуществлять-двухнаправленный обмен информацией между соседними устройствами. Это увеличивает набор операций, эффективно выполняемых вычислительной системой, и позволяет решать параллельно широкий круг задач математической физики методом конечных разностей. Формула изобретения Устройство для сопряжения выч|1Слительных машин, содержащее nepBtHl элемент И, два элемента ИЛИ, элемент запрета, регистр и триггер, единичный выход которого подключен к запрещающему входу элемента запрета, подключенного основным входом к выходу первого элемента ИЛИ, а выхо-. дом - к первому управляющему входу регистра, входу управления обменом вычислительной машины и первому входу первого элемента И, подключенного выходом к единичному входу триггера, первые входы первого и второго элемента ИЛИ являются соответственно входами запросов и ответов устройства, вторые входы .первого элемента И, первого и второго элементов ИЛИ и второй управляющий вход регистра соединены соответственно с первым, вторым и третьим входами задания режима и входом управления выбором направления приема информации вычислительной машины, первый и второй информационные входы и информационный выход регистра подключены сог ответственно к nepBONsy и второму информационным входам устройства и ин-: формационному выходу вмчислительной машины, от, ;личающееся тем что, с целью расширения функциональных возможностей устройства за счёт обеспечения двухнаправленного обмена в устрюйство введены пять элементов И и два коммутатора, причем первый вход второго элемента И соединен с выходом второго элемента ИЛИ, второй вход - с единичным выходом триггера и первыми входами третьего-шестого элементов, а выход - с нулевым входо триггера, первый настроечньй выход регистра соединен с первым запросным входом вычислительной машины, первыми входами коммутаторов и вторыми входами третьего и пятого элементов И, второй настроечный выход регистра подключен к второму запрос ному входу вычислительной машины, вторым входам четвертого и шестого элементов И и вторым взсоДам первого и второго коммутаторов, третьи- входы которых соединены с информационным выходом регистра, а выходы - соответственно с первым и вторшм дополнитель ными информационными выходами устройства, третьи входы первого и второго элементов ИЛИ являются соответственно вторыми управляющими входами приема запросов и ответов устройства, выхода третьего, четвертого, шестого и пятого элементов И являются ооответствукпцими индикационными выходами устройства, третий информационный выход регистра соединен с информационным входом вычислительной МсЦЦИНЫ . Источники информации, принятые во внимание при экспертизе . 1. Авторское свидетельство СССР по заявке t 2594839/24, кл. СЗ Об F 3/04, 1978. 2. Авторское свидетельство СССР № 613317, кл. G 06 F 3/04, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной вычислительной среды | 1979 |

|

SU767752A1 |

| Устройство для сопряжения | 1980 |

|

SU943694A1 |

| Модуль однородной вычислительной среды | 1988 |

|

SU1583933A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для сопряжения вычислительных машин | 1983 |

|

SU1179361A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1984 |

|

SU1191915A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1983 |

|

SU1108431A1 |

Авторы

Даты

1982-04-23—Публикация

1980-06-10—Подача