Изобретение относится к области автоматики, вычислительной техники и кибернетики. Известна ячейка одноро дной вычислительной среды, содержащая вычислительный блок, схему управления вводом, схему управления выводом и блок настройки 1., Недостатком ее является низкое быст родействие, так как согласование (синхронизация) работы элементов осуществляется с помощью операции обобщенного условного перехода, отмечающей готовность к взаимодействию всех элементов среды. Время реализации такого обо щенного оператора пропорционально числу элементов в системе. . Из известных устройств наиболее близким техническим решением к изобрё тению является ячейка однородной вычис лительной среды, содержащая триггер, блок приема запросов, блок приема отве тов, блок передачи запросов, блок Передачи ответов, блок вычисления арифметических функций и блок настройки, первая группа входов и первая группа выходов которого соединена с соответствующими выходами и входами блока вычисления арифметических функций, первый, BTO-J рой, третий и четвертый выходы блока настройки соединены соответственно с первым входом блока пе редачи ответов, первым входом блока приема.запросов, первым входом блока приема ответов, первым входом блока передачи запросов, выход блока приема запросов связан с единичным входом первого триггера, нулевой вход которого подключен к пятому выходу блока настройки, единичный выход триггера соединен с первым входом блока настройки и вторым входом блока передачи ответов, группа входов блока приема запросов, группа входов блока приема ответов и вторая группа входов блока настройки являются входами ячейки, а вторая группа I выходов блока настройки, выходы блока передачи запросов и выхоаы

блока передачи ответов - выходами ячейки 2.

Недостаток ее состоит в том, что только h./2 элементов среды ( И -общее число элементов в системе) при параллельной работе выполняет вычислительные функции, а И/2. элементов - функци буферных регистров, так как в один и тот же момент времени только h/2 элементов среды могут быть элементами передатчиками, а И/2 элементов - приемниками информации (обработка информации осуществляется после приема). Таким образом, в и/2 элементах среды не полностью используются их вычис лительные возможности.

Цель изобретения - повышение эффективности вычислительной среды, повышение быстродействия.

Эта цель достигается тем, что в ячейку введен второй триггер, единичный выход которого соединен со вторым входом блока передачи запросов и вторым входом блока настройки, единичный вход второго ;Триггера подключен к шестому выходу блока настройки, а нулевой вход подсоединен через формирователь импульсов к выходу блока приема ответов.

Блок настройки содержит первый и второй регистры, формирователи-импуль- сов, коммутаторы, элемент запрета и регистр настройки, первый, второй и третий выходы которого являются соответственно первым, третьим и четвертым выходами блока настройки. Четвертый выход регистра настройки соединен с .первым входом первого коммутатора, а пятый выход - с первым входом второго коммутатора, выход которого является вторым выходом блока, настройки. Второй вход второго коммутатора соединен со входом первогоформирователя импульсов и перBbiM входом блока настройки, управляющие входы первого и второго регистров соответственно с выходами первого и второго формирователей импульсов. Информационные входы первого регистра являются второй группой входов блока настройки, выходы первого коммутатора второй группой выходов блока настройки Второй вход первого коммутатора подключен к выходу второго регистра, вход второго формирователя импульсов соеди чен со входом запрета элемента запрете и. пЬдключе н ко второму входу блока настройки. Выход элемента запрета соециI нен с шестым выходом блока настройки. Вход регистра настройки., информационный вход элемента запрета, пятый выход блока настройки и информационный вход второго регистра являются первой группой входов блока настройки, а выход первого регистра, первый и второй входы блока настройки - первой группой выходов блока настройки.

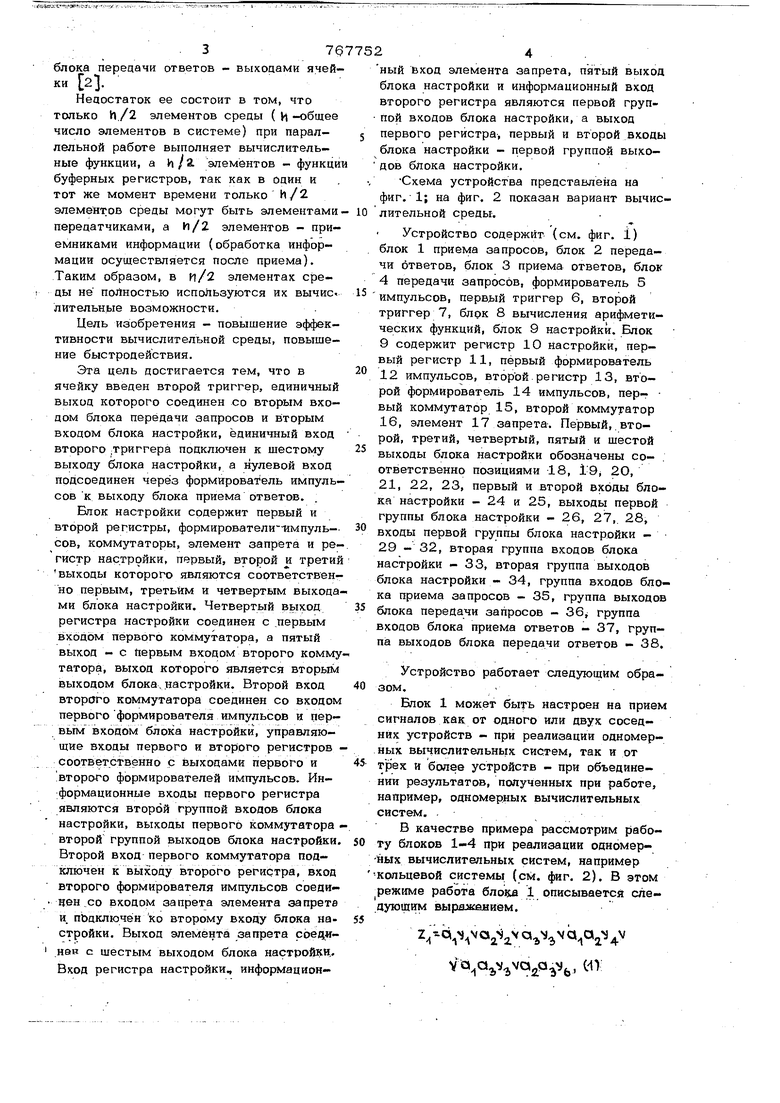

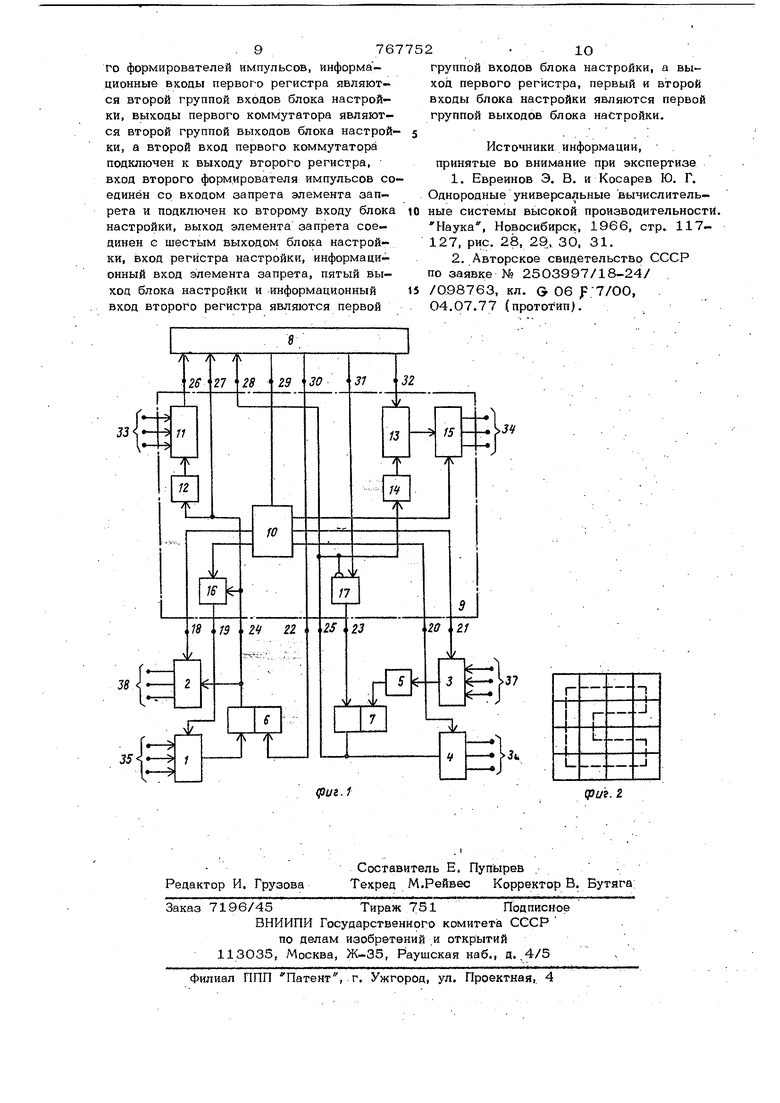

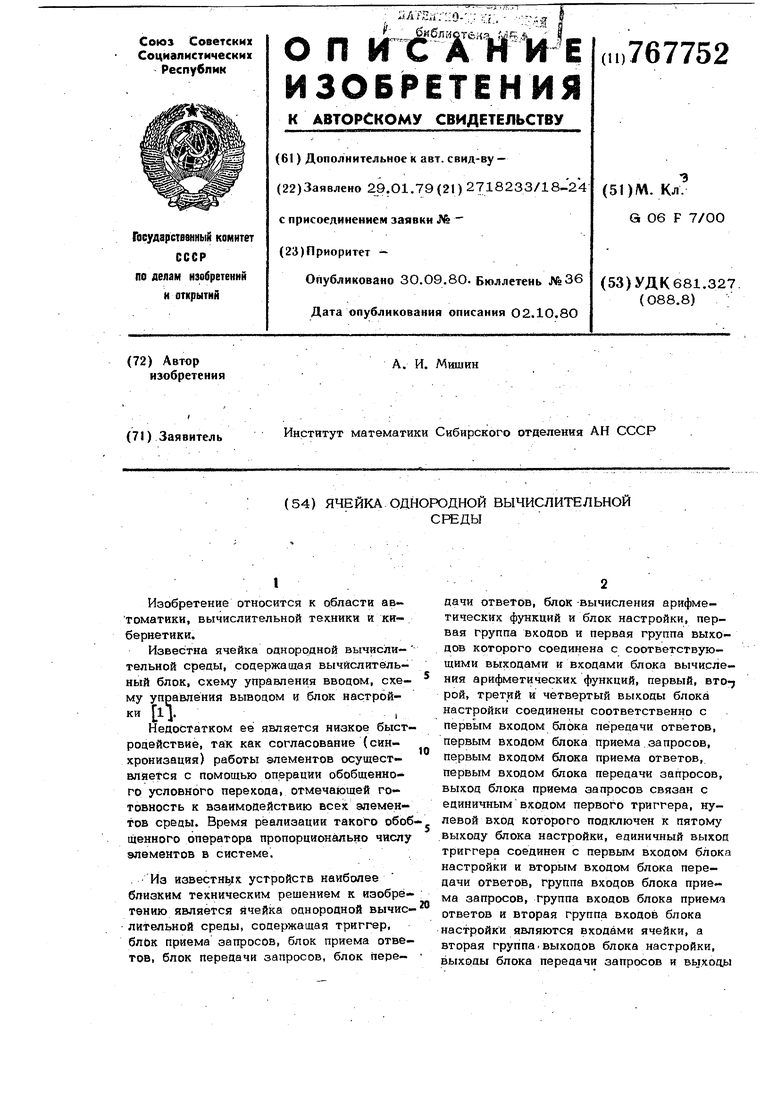

Схема устройства представлена на фиг. 1; на фиг. 2 показан вариант вычислительной среды.

Устройство содержит (см. фиг. 1) блок 1 приема запросов, блок 2 передачи ответов, блок 3 приема ответов, блок 4 передачи запросов, формирователь 5

импульсов, первый триггер б, второй триггер 7, блок 8 вычисления арифметических функций, блок 9 настройки. Блок 9 содержит регистр 10 настройки, первый регистр 11, первый формирователь

12 импульсов, второй регистр 13, второй формирователь 14 импульсов, пер- вый коммутатор 15, второй коммутатор 16, элемент 17 запрета. Первый,.второй, третий, четвертый, пятый и шестой выходы блока настройки обозначены соответственно позициями 18, i9i 20, 21, 22, 23, первый и второй входы блока настройки - 24 и 25, выходы первой группы блока настройки - 26, 27,. 28,

входы первой группы блока настройки 29 - 32, вторая группа входов блока настройки - 33, вторая группа выходов блока настройки - 34, группа входов блока приема запросов - 35, группа выходов блока передачи запросов - 36 группа входов блока приема ответов - 37, группа выходов блока переда.чи ответов - 38.

Устройство работает следующим образом.

Блок 1 может быть настроен на прием сигналов как от одного или двух соседних устройств - при реализации одномерных вычислительных систем, так и от трех и более устройств - при объединении результатов, полученных при работе, например, одномерных вычислительных систем.

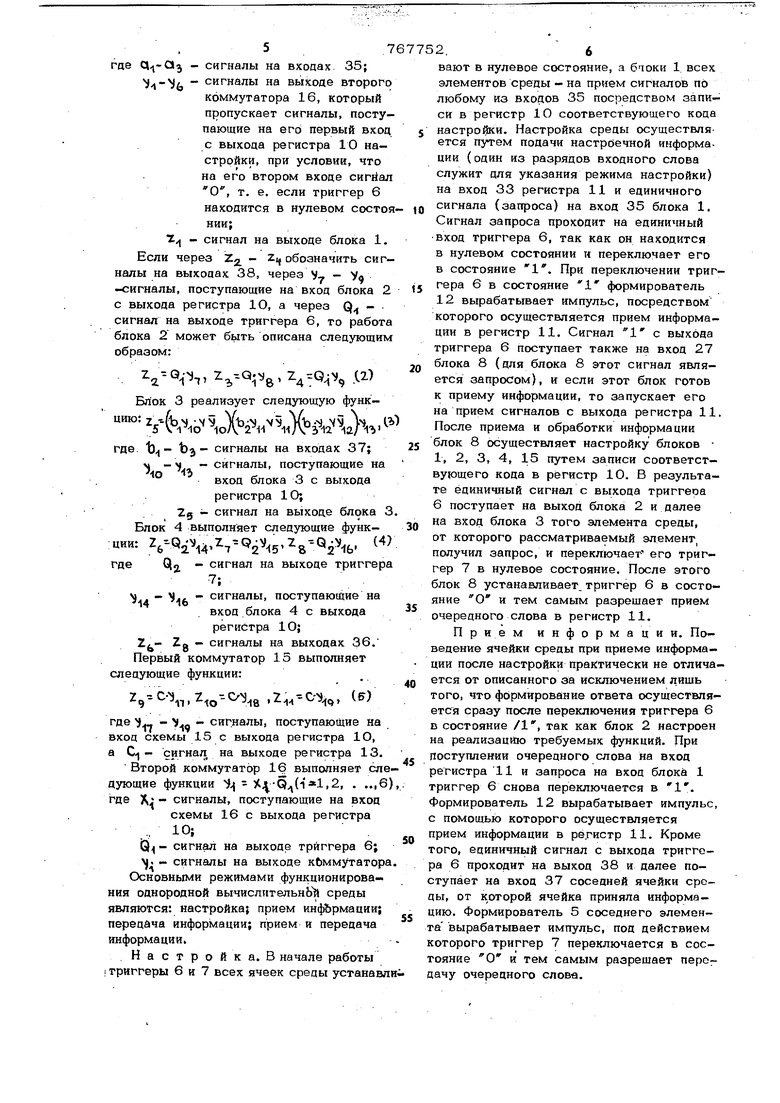

В качестве примера рассмотрим работу блоков 1-4 при реализации одномер-ных вычислительных систем, например -кольцевой системы (см. фиг. 2). В этом режиме работа блока 1 описывается следующим выражением.

z,--Q Va2V« 3 S°a4

,,,, C-IT где сигналы на входах 35; нз выходе второго коммутатора 16, который пропускает сигналы, посту пающие на его первый вход с выхода регистра 10 настройки, при условии, что на его втором входе сигйал О, т. е. если триггер 6 находится в нулевом состо нии; 1 - сигнал на выходе блока 1, Если через Zg - Zi, обозначить сиг налы на выходах 38, через Vy - Va -сигналы, поступающие на вход блока 2 с выхода регистра 1О, а через Q сигнал на йыходе триггера 6, то работ блока 2 может быть описана следующим образом: --QIT - i e A -iБлок 3 реализует следующую функцию: 7 trbs -V Yh-N v5 V5 W t 5 ,V v 1 Д з12W где Ъ - сигналы на входах 37; м - - сигналы, поступающие на °вход блока 3 с выхода регистра 1О; 2д - сигнал на выходе блока Блок 4 выполняет следующие функ. ции: Qg - сигнал на выходе триггер - . - сигналы, поступающие на вход блока 4 с выхода регистра 10; - сигналы на выходах 36. 8 Первый коммутатор 15 выполняет следующие функции: i2 -C5t Q, где - ) - сигналы, поступающие на вход схемы 15с выхода регистра 1О, а Ц- сигнал на выходе регистра 13. Второй коммутатор 16 выполняет сл дующие функции j - )-0(,26 где 5 - сигналы, поступающие на вход схемы 16 с выхода регистра .... loj iS); - сигнал на выходе триггера 6; j. - сигналы на выходе кЬммутатор Основными режимами функционирования однородной вычислительной среды являются: настройка; прием инфЬрмации; передача информации; прием и передача информации. , Настройка. В начале работы триггеры 6 и 7 всех ячеек среды устанав вают в нулевое состояние, а бчоки 1 всех элементов среды - на прием сигналов по любому из входов 35 посредством записи в регистр 10 соответствующего кода настройки. Настройка среды осуществляется путем подачи настроечной информации (один из разрядов входного слова служит для указания режима настройки) на вход 33 регистра 11 и единичного сигнала (запроса) на вход 35 блока 1. Сигнал запроса проходит на единичный вход триггера 6, так как он находится в нулевом состоянии и переключает его в состояние 1. При переключении триггера 6 в состояние формирователь 12 вырабатывает импульс, посредством которого осуществляется прием информации в регистр 11. Сигнал с выхода триггера 6 поступает также на вход 27 блока 8 (для блока 8 этот сигнал является запросом), и если этот блок готов к приему информации, то запускает его на прием сигналов с выхода регистра 11. После приема и обработки информации блок 8 осуществляет настройку блоков 1, 2, 3, 4, 15 путем записи соответствурщего кода в регистр 10. В результате единичный сигнал с выхода триггера 6 поступает на выход блока 2 и далее на вход блока 3 того элемента среды, от которого рассматриваемый элемент, получил запрос, и переключает его триггер 7 в нулевое состояние. После этого блок 8 устанавливает, триггер 6 в состояние О и тем самым разрешает прием очередного слова в регистр 11. Прием информации. Поведение ячейки среды при приеме информации после настройки практически не отличается от описанного за исключением лишь того, что формирование ответа осуществляется сразу после переключения триггера 6 в состояние /1, так как блок 2 настроен на реализацию требуемых функций. При поступлении очередного слова на вход регистра 11 и запроса на вход блока 1 триггер 6 снова переключается в 1. Формирователь 12 вырабатывает импульс, с помощью которого осуществляется прием информации в регистр 11. Кроме того, единичный сигнал с выхода триггера 6 проходит на выход 38 и далее поступает на вход 37 соседней ячейки среды, от к оторой ячейка приняла информацию. Формирователь 5 соседнего элемента вырабатывает импульс, под действием которого триггер 7 переключается в состояние О и тем самым разрешает перодачу очередного слова.

Передача информации зменение сигнала с 1 на О на входе 28 указывает блоку 8, что информация с регистра 13 принята в регистр 11 соседней ячейки и среца может начать передачу оче- редкого слова. Для этого блок 8 выстав-, ляет очередное слово на выход 32 и едич ничный сигнал на выход 31, под действием которого элемент 17 запрета вырабатывает сигнал 1 и триггер 7 переключается в состояние 1. После переключения триггера в 1 блокируется прохождение сигнала 1 на выход схемы 17 запрета. Единичный сигнал с выхоДа триггера 7 .поступает на вход блока 4, : а с его выхода - на вход блока 1 сосед-: ней ячейки среды и если ее триггер 6 находится в состоянии О, т, е. если предыдущее .слово принято блоком 8, то переключает его в 1. В результате

очередное слово записывается в регистр 11 принимающей ячейки, а блок 2 этой ячейки вырабатывает сигнал 1, который поступает на вход блока 3 передающей ячейки и переключает триггер 7 в состояние О. Изменение сигнала с 1 на О на входе 28 указывает блоку 8, что ячейка может начать передачу следующего слова.

Прием и переда ч-а ин- формации. С помощью этого режима работы осуществляется параллельный обмен информацией между соседними ячейками, например, кольцевой системы (см. фиг. 2, где кольцевая система показана пунктирной линией). Блок 8 принимает информацию в регистр 11, поступающую по информационному входу 33 d-информационного выхода 34 соседней ячейки, передает информацию с регистра 13, поступающего в него- по входу 32. Передача информации из блока 8 осуществляется по сигналу О на выходе 28, появляющемуся после установки в О триггера 7 сигна,лом по входу 37, аналогично описанному в . .режиме передачи .информации.

Приём информации блоком 8 осуществляется по сигналу 1 на выходе 27, появляющемуся при подаче на вход 35 сигнала 1, аналог ично описанному в

режиме приема информации.

Таким образом, в среде возможен па- раллельный обмен информацией по схеме каждая ячейка среды - своей соседней ячейке, что увеличивает эффективность

вычислительной среды. Формула изобретения

1. Ячейка однородной вычислительной. среды, содержащая триггер, блок приема

запросов, блок приема ответов, блок передачи запросов, блок передачи ответов,

; блок вычисления арифметических функций и блок настройки, первая группа входов и первая группа выходов которого соединена соответственно с первой группой выходов и первой группой входов блока вычисления арифметических функций, первый, второй, третий и четвертый выходы блока настройки соединены соответственно с первым входом блока передачи ответов, первым входом блока приема запросив, первым входом блока приема ответов, первым входом блока передачи запросов, вы-ход блока приема зэпросов соединен с единичньш входом первого триггера, нулевой вход которого подключён к пятому выходу блока настройки, единичный выход первого триггера .соединен с первым входом блока настройки и вторым входом блока передачи ответов, группа входов блока приема запросов, группа входов блока приема ответов и вторая группа входов блока настройки являются входами ячейки, а эторая группа выходов блока настройки, выходы блока передачи запросов и выходы блока передачи ответов являются выходами ячейки, отличающаяся тем, что с целью повышения быстродействия, в ячейку введен второй триггер, единичный выход которого соединен со вторым входом блока передачи запросов и вторым входом блока настройки, единичный вход второго триггера подключен к шестому выходу блока настройки, а нулевой вход подсоединен через формирователь импульсов к выходу блока приема ответов.

2. Ячейка по п. 1, отличающаяся тем, что блок настройки содержит первый и второй регистры, формирователи импульсов, коммутаторы, элемент запрета, регистр настройки, первый, второй и третий выходы которого являкЗтся соответственно первым, третьим и четвертым выходами блока настройки, четвертый выход регистра настройки соединен с первым входом первого коммутатора, а пятый выход - с первым входом второго коммутатора, выход которого является вторым выходом блока настройки, второй вход второго коммутатора соединен со входим пе звого формирователя импульсов и с первым входом блока насгройки, управляющие входы первого и второго регистров соединены соот 0ветственно с выходами первого и вторе

TO формирователей импульсов, информационные вкоды первого регистра являются второй группой входов блока настройки, выходы первого коммутатора являются второй группой выкодов блока настройки, а второй вкод первого коммутатора подключен к выходу второго регистра, вход второго формирователя импульсов соединён со входом запрета элемента запрета и подключен ко второму входу блока настройки, выход элемента запрета соединен с шестым выходом блока настройки, вход регистра настройки, информационный вход элемента запрета, пятый выход блока настройки и информационный вход второго регистра являются первой

группой входов блока настройки, а выход первого регистра, первый и второй входы блока настройки являются первой группой выходов блока настройки.

..;.:

Источники информации, принятые во внимание при экспертизе

1.Евреинов Э. В. и Косарев Ю. Г. Однородные универсальные вычислитель-

ные системы высокой производительности. Наука, Новосибирск, 1966, стр 117127, рис. 28, 29., 30, 31.

2.Авторское свидетельство СССР о заявке № 2503997/18-24/

/О98763, кл. G 06 f:7/00, 04.07.77 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительных машин | 1980 |

|

SU922714A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Модуль однородной вычислительной среды | 1988 |

|

SU1583933A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для сопряжения источников и приемников с магистралью | 1986 |

|

SU1363227A2 |

| Устройство многоуровневого прерывания | 1985 |

|

SU1287158A1 |

Авторы

Даты

1980-09-30—Публикация

1979-01-29—Подача