(5) УСТРОЙСТВО для ГЕНЕРАЦИИ ВЕКТОРОВ НА ИНДИКАТОРЕ С РАСТРОВОЙ РАЗВЕРТКОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для генерации векторов на индикаторе с черезстрочной разверткой | 1980 |

|

SU922718A1 |

| Устройство для формирования символов | 1983 |

|

SU1088060A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1989 |

|

SU1689983A1 |

| Устройство для отображения информации | 1978 |

|

SU746629A1 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Устройство для отображения информации | 1987 |

|

SU1513439A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

| Устройство для ввода информации | 1990 |

|

SU1702382A1 |

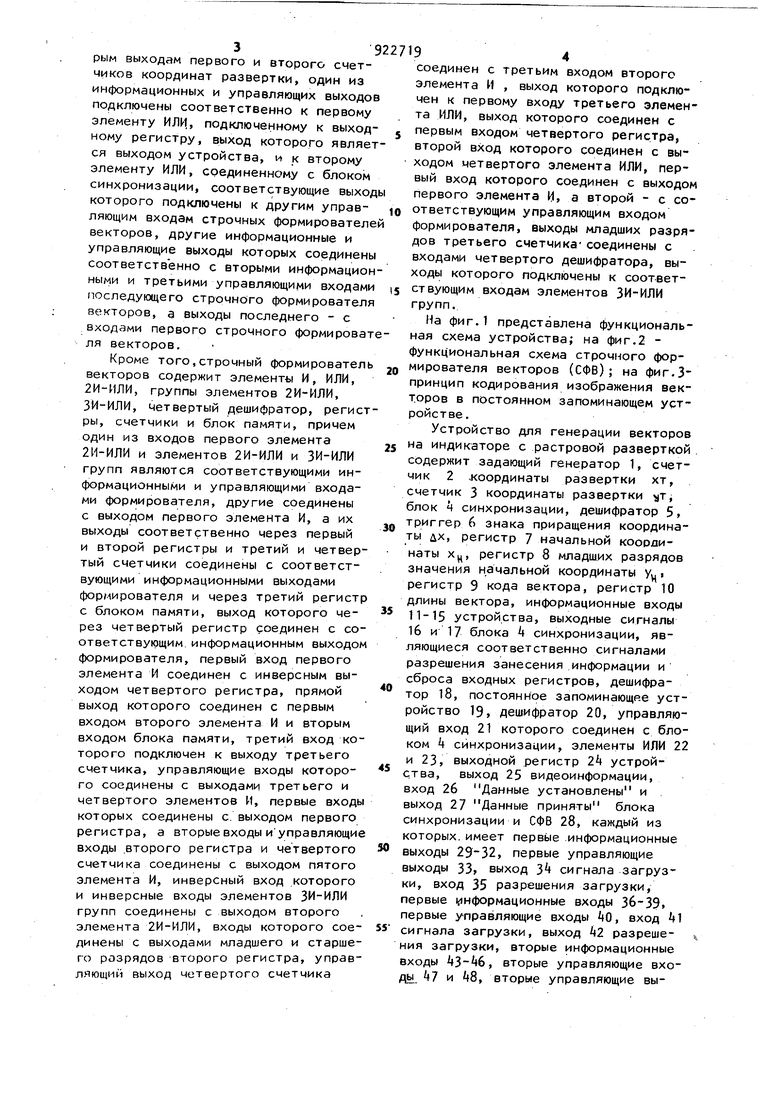

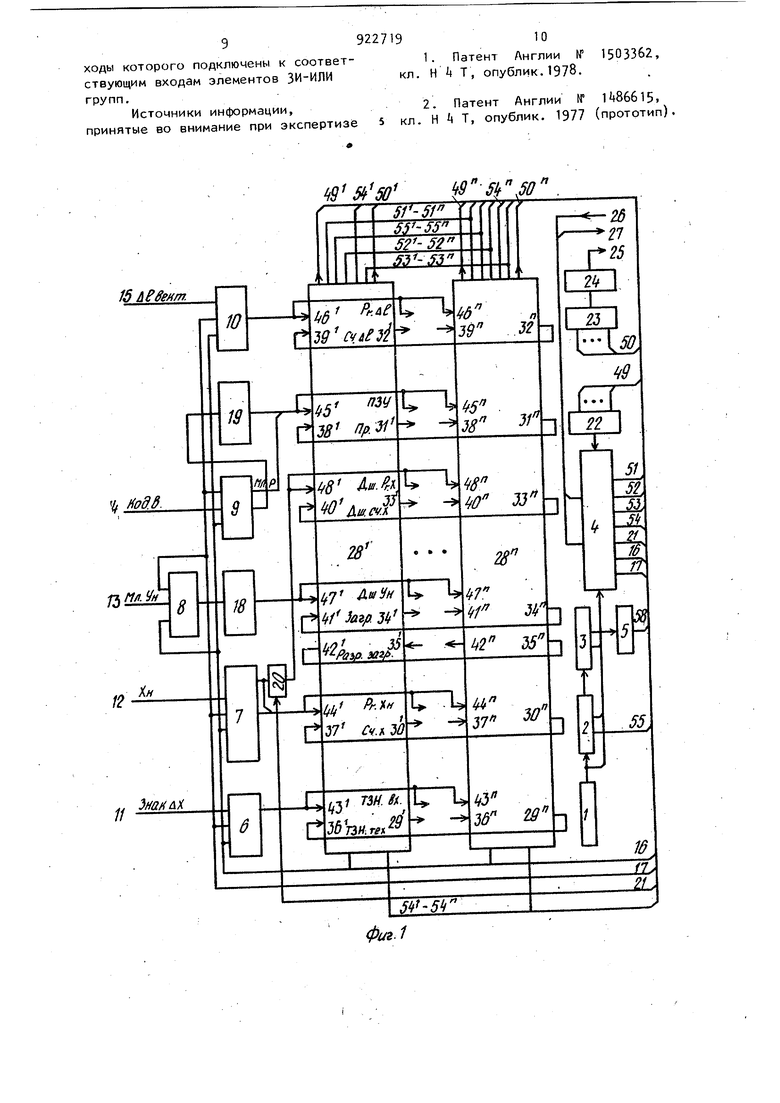

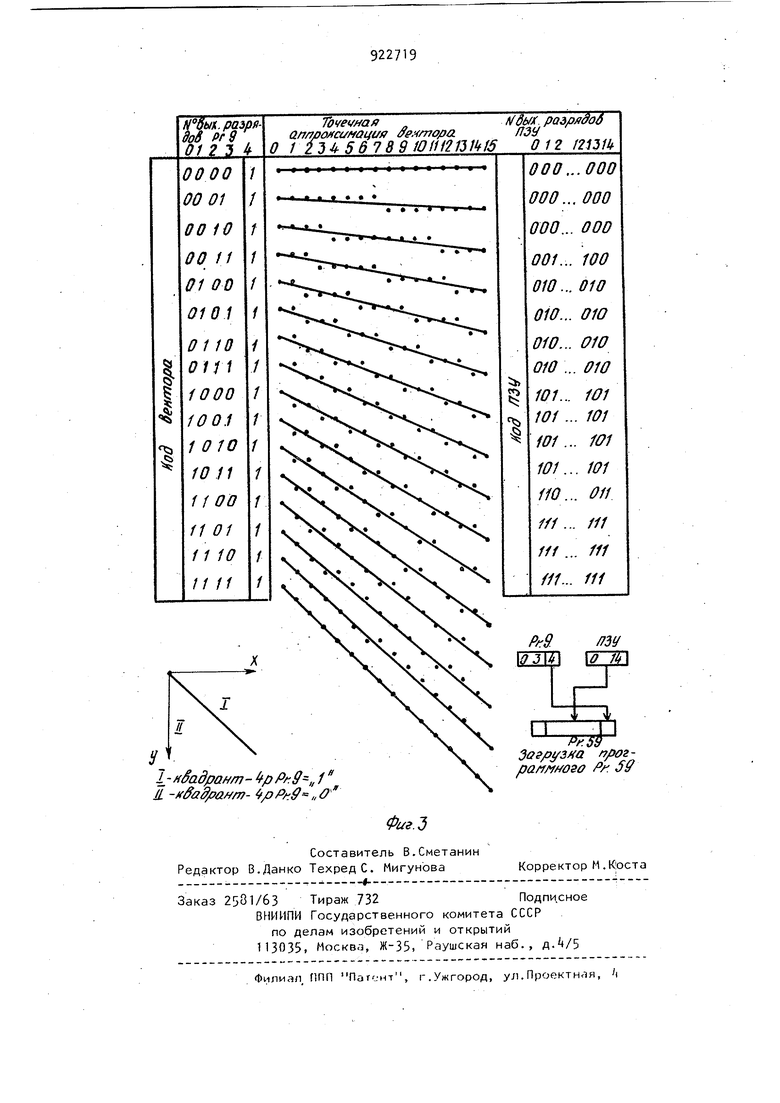

Изобретение.относится к вычислительной технике и может быть использовано в устройствах отрбражения графической информации, в которых оконечным устройством является индикатор с растровой разверткой. Известно устройство для генерации векторов на индикаторе с растровой разверткой, содержащее два блока сло жения, пять регистров, четыре сметчи ка, одиннадцать мультиплексоров, бло ки памяти на две телевизионные строк и средства управления СО. Недостатком этого устройства явля ется, то что оно позволяет вычислять точки пересечения векторов только с одной телевизионной строкой и имеет большой объем оборудования. Наиболее близким техническим ре шением к изобретению является устрой ство, содержащее восемь регистров, четыре постоянных запоминающих устройства, мультиплексор, двенадцать блоков памяти и :общее устройство управления С 2 . Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что а устройство для генерации векторов на индикаторе с растровой разверткой введены дополнительные элементы ИЛИ п-строчных формирователей векторов, где п - число CTpoiT растра пересекающих знакомест, у каждого из которых одни из информационных вхрдов подключены к выходам триггера знака, первого регистра начальных координат,- регистра длины вектора, блока постоянной памяти и выходу младшего разряда регистра кода вектора, одни из управляющих входов Соединены соответственно через первый и второй дешифраторы к первому и второму регистрам начальных координат, одни из адресных входов непосредственно, а другие через третий дешифратор подключены к вторым выходам первого и второго счетчиков координат развертки, один из информационных и управляющих выходо подключены соответственно к первому элементу ИЛИ, подключенному к выход ному регистру, выход которого являе ся выходом устройства, и к второму элементу ИЛИ, соединенному с блоком синхронизации, соответствующие выхо которого подключены к другим управляющим входам строчных формировател векторов, другие информационные и управляющие выходы которых соединен соответственно с вторыми информацио ными и третьими управляющими входам последующего строчного формировател векторов, а выходы последнего - с входами первого строчного формирова ля векторов. Кроме того,строчный формировател векторов содержит элементы И, ИЛИ, 2И-ИЛИ, группы элементов 2И-ИЛИ, ЗИ-ИЛИ, Четвертый дешифратор, регист ры, счетчики и блок памяти, причем один из входов первого элемента 2И-ИЛИ и элементов 2И-ИЛИ и ЗИ-ИЛИ групп являются соответствующими информационными и управляющими входами формирователя, другие соединены с выходом первого элемента И, а их выходы соответственно через первый и второй регистры и третий и четвертый счетчики соединены с соответствующими информационными выходами формирователя и через третий регистр с блоком памяти, выход которого через четвертый регистр соединен с соответствующим, информационным выходом формирователя, первый вход первого элемента И соединен с инверсным выходом четвертого регистра, прямой выход которого соединен с первым входом второго элемента И и вторым входом блока памяти, третий вход которого подключен к выходу третьего счетчика, управляющие входы которого соединены с выходами третьего и четвертого элементов И, первые входы которых соединены с. выходом первого регистра, а вторые входы исправляющие входы второго регистра и четвертого счетчика соединены с выходом пятого элемента И, инверсный вход которого и инверсные входы элементов ЗИ-ИЛИ групп соединены с выходом второго элемента 2И-ИЛИ, входы которого соединены с выходами младшего и старшего разрядов второго регистра, управляющий выход четвертого счетчика соединен с третьим входом второго элемента И , выход которого подключен к первому входу третьего элемен та ИЛИ, выход которого соединен с первым входом четвертого регистра, второй вход которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй - с соответствующим управляющим входом формирователя, выходы младших разрядов третьего счетчика- соединены с входами четвертого дешифратора, выходы которого подключены к соответствующим входам элементов ЗИ-ИЛИ групп. На фиг.1 представлена функциональная схема устройства; на фиг.2 функциональная схема строчного формирователя векторов (СФВ); на фиг.Зпринцип кодирования изображения векторов в постоянном запоминающем устройстве. Устройство для генерации векторов на индикаторе с растровой разверткой . содержит задающий генератор 1, счетчик 2 -координаты развертки хт, счетчик 3 координаты развертки -цг, блок 4 синхронизации, дешифратор 5, триггер 6 знака приращения координаты дх, регистр 7 начальной координаты Хц, регистр 8 младш.их разрядов значения начальной координаты Уц i регистр 9 кода вектора, регистр 10 длины вектора, информационные входы 11-15 устройства, выходные сигналы 16 и 17 блока 4 синхронизации, являющиеся соответственно сигналами разрешения занесения информации и сброса входных регистров, дешифратор 18, постоянное запоминающее устройство 19, дешифратор 20, управляющий вход 21 которого соединен с блоком 4 синхронизации, элементы ИЛИ 22 и 23, выходной регистр 24 устройства, выход 25 видеоинформации, вход 26 Данные установлены и выход 27 Данные приняты блока синхронизации и СФВ 28, каждый из которых, имеет первые .информационные выходы , первые управляющие выходы 33, выход 34 сигнала загрузки, вход 35 разрешения загрузки, первые 1(1Нформационные входы 36-39 первые управляющие входы 40, вход 41 сигнала загрузки, выход 42 разрешения загрузки, вторые информационные входы 43-46, вторые управляющие входы 47 и 48, вторые управляющие выходы Si вторые информационные выходы 50, третьи, четвертые, пятые и шестые управляющие входы , первые и вторые адресные входы 5 и 55, триггер 56 знака приращения координаты, счетчик 57 координаты х, третий адресный вход 58, регистр 59 сдвига, счетчик 60 длины вектора, регистр 61 памяти, дешифратор 62, элементы ИЛИ , элементы И 66-6 элементы 2И-ИЛИ 70 и 71, группы эле ментов 2И-ИЛИ 72-7, группу элементов ЗИ-ИЛИ 75, блок 76 постоянной памяти, выходной регистр 77 СФВ и триггер 78 занятости СФВ. Устройство работает следующим образом. Когда на информационных входах 11-15 устройства установлены реальные данные, на вход 2б поступает сигнал Данные установлены, и если до этого поступил в блок t синхронизации с выхода элемента 22 сигнал Входные регистры свободны, то блок k синхронизации вырабатывает п линии 17 сигнал Разрешение занесения информации. При этом информация на входах: 11 - знак дх - 1 бит 12- значение х - К бит 13- младшие разряды бит И - код вектора - ( -1 ) бит 15 - значение длины вектора,- (2 -1) бит (в конкретной реализации устройст ва ) загружается соответственно в триггер 6, регистры 7-10. Эта информация посредством дешиф ратора 18 направляется в СФВ, номер которого задается регистром 8, одна ко загрузка выбраного СФВ происходи только тогда, когда выбираемый СФВ свободен, т.е. на инверсном выходе триггера 78 занятости СФВ устанавли вается уровень логической 1. При этом информация с выходов триггера 6, регистра 7, постоянного запомина ющего устройства 19 совместно с выходом младшего разряда регистра 9 кода вектора, регистра 10 через эле мент 2И-ИЛИ 70 и группы элементов 2И-ИЛИ 72, 7 и 73 загружается соот ветственно в триггер 5б, счетчик 57 регистр 59 сдвига и счетчик 60 длин вектора, одновременно с этим произво дится загрузка регистра 61 памяти, количество разрядов которого равно числу модулей памяти в блоке 76 постоянной памяти, от дешифратора 20 96 младших разрядов регистра 7 через группу элементов ЗИ-ИЛИ 75. Далее производится запись начальной точки вектора в блок 76 постоянной памяти, при этом номер модуля памяти задается соответствующим ему триггером регистра 61 памяти, адрес - старшими разрядами счетчика 57, а управляющим сигналом служит сигнал по входу 52 из блока k синхронизации. Через время, необходимое для записи информации в блок 76 памяти, блок k синхронизации вырабатывает по входу 51 стробит рующий сигнал, который поступает на элемент ИЛИ б и сбрасывает регистр 61 памяти, а через элемент И 68 производит вычитание единицы из содержимого счетчика 60 длины вектора, производит сдвиг влево на один бит регистра 59, увеличивает или уменьшает значение счетчика 57 в зависимости от состояния триггера 56 знака дх, при этом, если с выхода отрицательного переполнения счетчика 60 длины вектора не поступил сигнал окончания построения вектора, а выход элемента 2И-ИЛИ 71 находится в состоянии логической 1,что указывает на окончание построения вектора в данной телевизионной строке, и регистр памяти обнулен, а также имеется разрешающий уровень сигнала разрешения загрузки информации по входу 35 от следующего СФВ, с выхода элемента И 69 данного СФВ поступает в следующий СФВ сигнал загрузки; Данные с выходов триггера 5б знака дх, счетчика 57, регистра 59, счетчика 60 .длины вектора и дешифратора 62 по выходам 29-33 поступают в следующий СФВ, где отработка вектора продолжается. Если же выход элемента 2И-ИЛИ 71 находится в состоянии логического О, то. отработка вектора продолжается в данном СФВ. Записанные в блоке памяти СФВ данные считываются под управлением счетчиков 2 и 3 XT и ут, а также дешифратора 5 младших разрядов счетчика 3 т, при этом дешифратор 5 выбирает СФВ, из которого затем считываются данные, и выходы старших разрядов счетчика 2 хт задают значение адреса в блок 76 постоянной памяти. Считанные данные пост упают через выходной регистр 77 СФВ, через элемент ИЛИ 23 и выходной регистр 2 устройства на выход 25 видеоинформации устройства. Сравнение предлагаемого устройства с известным при , где п число СФВ, показывает увеличение быстродействия устройства в k-S раз, что позволяет использовать его в высокопроизводительных системах отображения графической информации. Формула изобретения 1. Устройство для генерации векторов на индикаторе с растровой разверткой, содержащее последовательно соединенные задающий генератор, первый и второй счетчики координат развертки, подключенные к блоку синхронизации, триггер знака, регистры начальных координат, кода и длины вектора, первые входы которых являются информационными входами устройства, а вторые подключены к блоку синхронизации, который соединен с управляющими входами устройства, блок постоянной памяти, вход которого соеди нен с разрядными выходами регистра кода вектора,, и дешифраторы, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элементы ИЛИ п-строчных формирователей векторов, где п - число строк растра пересекающих знакомест, у каждого из которых .одни из информационных входов подклю чены к выходам триггера знака, первого регистра начальных координат, регистра длины вектора, блока постоянной памяти и выходу младшего разряда регистра кода вектора, одни из управляющих входов соединены соответ ственно через первый и второй дешифраторы к первому и второму регистрам начальных координат, один из адресны входов непосредственно, а другие через третий дешифратор подключены к вторым выходам первого -и второго счетчиков координат развертки, одни из информационных и управляющих выхо дов подключены соответственно к пер вому элементу ИЛИ, подключенному к выходному регистру, выход которого является выходом устройства, и к вто рому элементу ИЛИ, соединенному с блоком синхронизации, соответствующи выходы которого подключены к другим управляющим входам строчных формиро вателей векторов, другие информацион ные и управляющие выходы которых соединены соответственно с вторыми 9 8 информационнымии третьими управляю-, щими входами последующего строчного формирователя .векторов, а выходы последнего - с входами первого строчного формирователя векторов. 2. Устройство по п.1, о т л и ч аю щ е е с я тем, что строчный формирователь векторов содержит элементы И, ИЛИ, 2И-ИЛИ, группы элементов 2И-ИЛИ, ЗИ-ИЛИ, четвертый дешифратор, регистры, счетчики и блок памяти, причем одни из входов первого элемента 2И-ИЛИ и элементов 2И-ИЛИ и ЗИ-ИЛИ групп являются соответствующими информационными и управляющими входами формирователя, другие соединены с выходом первого элемента И, а их выходы соответственно через первый и второй регистры и третий и четвертый счетчики соединены с соответствующими информационными выходами формирователя и через третий регистр с блоком памяти, выход которого через чeтЁeptый регистр соединен с соответствующим информационным выходом формирователя, первый вход первого Элемента И соединен с инверсным выходом четвертрго регистра, прямой выход которого соединен с первым входом второго элемента И и вторым входом блока памяти, третий вход которого подключен к выходу третьего счетчика, управляющие входы которого соединены с выходами третьего и четвертого элементов И, первые входы которых соединены с выходом первого регистра, а вторые входы и управляющие входы второго регистра и четвертого счетчика соединены с выходом пятого элемента И, инверсный вход которого и инверсные входы элементов ЗИ-ИЛИ групп соединены с выходом второго элемента 2И-ИЛИ, входы которого соединены с выходами младшего и старшего разрядов второго регистра, управляющий выход четвертого счетчика соединен с третьим входом второго элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого соединен с первым входом четвертого региcтpaJ второй вход которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй - с соответствующим управляющим входом формирователя,.выходы младших разрядов третьего счетчика соединены с входами четвертого дешифратора, выходы которого подключены к соответствующим входам элементов ЗИ-ИЛИ групп. Источники информации, принятые во внимание при экспертизе 5

15 йВвеит

oi

Ю

гя счлп.

if5

38 Пр.

/%

1/8 Aia.f.Ji

If Ml

ОАШС : Dn 7 АшУн -(/Лгг J« N заг 37 Сч.к ЪО . ГМЪм«Х

ei п СП

4g VitS

77

52

1 2it

С 1

гю

39 J

- -5

Л50

PL

1 ПЗУ

3f

5/

8

I/O JJ

-

M i; с Pf.%H h ; 73Я Л.

Фиг 1 1. Патент Англии № 1503362, кл. НЧ Т, опублик.1978. 2. Патент Англии № Т вббТЗ, кл. Н А Т, опублик. 1977 (прототип) J it2 Ъ5 ц -.пП yjn W -э 3d Id C. 2П

Авторы

Даты

1982-04-23—Публикация

1980-03-21—Подача