четвертый выход второй группы выходов блока памяти микрокоманд соединен с прямым входом второго элемент И-НР;; второго блока формирования управляющих сигналов, пятый, шестой и седьмой выходы второй группы выходов блока памяти микрокоманд соединены соответственно с первыми, вторыми и третьими управляющими входами первого, второго и третьего муль типлексоров, восьмой выход второй группы выходов блока памяти микрокоманд соединен с первым прямым входом элемента 2И-ИЛИ второго блок формирования управлякщих сигналов и с первыми информационнь ми входами второго и третьего мультиплексоров, первый выход первой группы выхдов блока памяти микрокоманд соединен с первым входом второго элемента И первого блока формирования управляющих сигналов, счетный вход счетчика соединен с выходом элемента И-ИЛИ, вход записи счетчика соединен с выходом второго элемента 2И-ИЛИ-НЕ, выход переполнения счетчика соединен с информационным входом третьего триггера первого блока

формирования управлякнцих сигналов, группа информационных выходов счетчика соединена с первой группой адресных выходов устройства, первая группа выходов блока памяти микрокоманд соединена с группой входов блока дешифраторов, первый выход которого соединен с входом разрешения данных операционного блока, с первым инверсным входом третьего элемента И второго блока формирования управляющих сигналов, с выходом разрешения обращения к внешней памяти устройства и с вторым входом второго элемента И первого блока формирования управляющих сигналов, второй и третий выходы блока дешифраторов соединены соответственно с первым входом второго элемента И второго блока формирования управляющих сигналов и с вторым инверным входом третьего элемента И второго блока формирования управляюш х сигналов, четвертый выход блока дешифраторов соединен с третьим инверсным входом третьего элемента И второго блока фop fflpoвaния упр-авляю1цих сигналов и с первым инверсным входом элемента 2И-ИЛ второго блока формирования управляюш 1х сигналов, пятьй выход блока дешифраторов соединен с прямым входом третьего элемента И первого блока формирования управляющих сигналов, шестой выход блока дешифраторов соединен с управляющим входом четвертого мультиплексора и с первым входом элемента И-НЕ первого блока формирования управляющих сигналов, вход Запуска устройства соединен с инверсными входами первого и второго элементов 2И-Ш1И-НЕ, с инверсным входом первого элемейта ИЛИ-НЕ, с входом установки в О четвертого триггера первого блока формирования управляющих,сигналов, с входом установки в 1 первого триггера первого блока формирования управляющих сигналов и с вторым инверсным входом первого элемента ИЛИ первого блока формирования управляющих сигналов, тактовьй вход устройства соединен с прямым входом первого элемента ИЛИ первого блока формирования управляющих сигналов, вход синхронизации операционного блока соединен с выходом первого элемента ИЛИ первого блока формирования управляющих сигналов,с входом синхронизации Tpetbero триггера первого блока формирования управляющих сигнаЛС1В, с инверсными входами третьего и четвертого элементов И первого блока формирования управляющих сигналов, с первым инверсным входом первого элемента И первого блока формирования управляющих сигналов, с третьим входом второго элемента И первого блока формирования управляющих сигналов, с вторым инверсным входом первого элемента И второго блока формирования управляющих сигналов, с инверсными входами первого и второго элементов И-НЕ второго блока формирования управляющих сигналов и с входами синхронизации первого, второго, и третьего триггеров, второго блока формирования управляющих сигналов, выход управления записью во внешнюю память устройства сперлнен с выходом третьего элемента И первого блока формирования управляющих сигналов, выход управления чтением из внешней памяти устройства соединен с выходом элемента И-НЕ первого блока формирования управляющих сигналов и с входом синхронизации первого

триггера первого блока формирования управляюгщх сигналов, вход сдвига вправо операционного блока соединен с выходом первого мультиплексора, с прямым входом третьего элемента И второго блока формирования управляющих сигналов с вторым входом второго элемента И второго блока формирования управляющих сигналов и с инверсным и пятым прямым входами элемента ЗИ-ИЛИ, вход пе.реноса операционного блока соединен с выходом элемента 2И-ИЛИ второго блока формирования управляющих сигналов, вход маскирующей шины операционного блока соединен с выходом третьего элемента И второго блока формирования управляющих сигналов, вход разрешения адреса операционного блока подключен к шине нулевого потенциала, первый информационный вход группы информационны входов операционного блока соединен с выходом второго мультиплексора с первым информационным входом первой группы информационных входов четвертого мультиплексора и с первы йыходом знаковых разрядов координат круговой развертки устройства, второй информационный вход группы информационных входов операционного блока соединен с выходом третьего мультиплексора, с первым информационным входом второй группы информационных входов четвертого мультиплексора и с вторым выходом знаковых разрядов координат круговой развертки устройства, остальные информационные входы группы информационных входов операционного блока соединены с информационными входами устройства, входы внешней шины операционного блока соединены с адресными выходами операционного блока и с адресными выходами устройства, выход переноса и выход сдвига вправо операционного блока соединены с информационным входом первого триггера второго блока формирования управляющих сигналов, первый информационный выход группы операционного блок соединен с. информационным входом второго триггера второго блока формирования управляющих сигналов и с первым выходом знаковых разрядов операнда устройства, второй информационный выход группы информационных входов операционного блока соединен с информационным входом

третьего триггера второго блока формирования управляющих сигналов и с BTopbLM выходом знаковых разрядов операнда устройства, остальные информационные выходы операционного блока соединены с информационными выходами устройства, первьш прямой выход дешифратора соединен с информационным входом второго триггера первого блока формирования управляющих сигналов с первый и вторым прямыми входами первого элемента 2И-ИЛИ-НЕ, с первым входом первого элемента ИЛИ первого блока формирования управляющих сигналов, с инверсным входом элемента 2И-ИЛИ первого блока формирования управляющих сигналов и с первым прямым входом второго элемента 2И-ИЛИНЕ, второй прямой выход дешифратора соединен с прямым входом первого элемента И второго блока формирования управляющих сигналов, прямой вход первого элемента ИЛИ-НЕ соединен с третьим прямым входом первого элемента 2И-ИЛИ-НЕ, с первым входом элемента И-ИЛИ, с вторым и третьим прямыми входами второго элемента 2И-ИПИ-НЕ, с выходом четвертого элемента И первого блока формирования управляющих сигналов, с первым входом элемента И-РШИ-НЕ и с вторым входом элемента И-НЕ первого блока формирования управляющих сигналов, выход второго триггера первого блока формирования управляющих сигналов соединен с вторым входом второго элемента ИЛИ-НЕ, с первым прямым входом элемента 2И-ИЛИ первого блока формирования управляющих сигналов и с первым входом второго элемента ИЛИ первого блока формирования управляющих сигналов, четвертый прямой вход первого элемента 2И-ИЛИ-НЕ соединен с выходом пятого элемента И первого блока формирования управляющих сигналов и с вторым входом элемента И-ИЛ И-НЕ выход второго элемента ИЛИ-НЕ соединен с вторым прямым входом пятого элемента И первого блока формирования управляюш 1х сигналов, с вторым прямым входом элемента 2И-ИЛИ первого блока фор-, мирования управляющих сигналов и

прямым входом шестого элемента И первого блока формирования управляющих сигналов, третий прямой вход элемента 2И-И.ПИ первого блока формирования управляющих сигналов соедийен с выходом четвертого триггера первого блока формирования управляющих сигналов, с инверсным входом шестого элемента И первого блока формирования управляющих сигналов и с третьим входом элемента И-ИЛИ-НЕ выход которого соединен с входом синхронизаш1и четвертого трип ра первого блока формирования управляющих сигналов, информационный вход которого соединен с выходом шестого элемента И первого блока формирования управлякицих сигналов и с вторым

входом элемента И-ИЛИ, третий вход которого соединен с выходом второго элемента И. первого блока формирования управляющих сигналов, выход элемента 2И-ИЛИ первого блока формирования управляющих сигналов соедиНей с. инверсным входом пятого элемента И. первого блока формирования, управлякнцих сигналов, с четвертым прямым входом, второго элемента 2И-ИЛИ-НЕ и с вторым входом второго элемента ИЛИ первого блока формирования управляющих сигналов, выход которого соединен с третьим входом элемента И-НЕ первого блока формирования управляющих сигналов, выход, третьего триггера первого блока формирования управля1ащ1х сигналов, выход элемента ЗИ-ИЛИ соединен с вторым инверсным входом первого элемента И первого блока формировани управляющих сигналов и с прямым входом четвертого элемента И первого блока формирования управляюпщх сигналов, выход первого элемента И- , второго блока формирования управляющих сигналов соединен с первыми входами четвертого и пятого элемен тов И второго блока формирования управляющих сигналов, второй вход , четвертого элемента И второго блока формирования управляющих сигналов соединен с выходом первого триггера второго блока формирования управляющих сигналов и с вторым информационным входом второй группы четвертого мультиплексора, первьй выход которого сое.динен с информационным входом четв,ертого триггера второго блока формирования управляющих сигналов, вход синхронизации которого соединен с выходом первого элемента И-НЕ второго блока формирования управляющих сигналов и с входом синхронизации пятого триггера второго блока формирования управляющих сигналов.

информационный вход которого соединен с вторым выходом четвертого муль типлексора, второй информационный вход первой группы которого соединен с первыми прямым и инверсным информационными входами первого муль типлексора, с вторым информационным входом второго мультиплексора, с выходом второго триггера второго блока формирования управляющих сигналов и с информационным входом шестого триггера второго блока формирования управляющих сигналов, входсинхронизации которого .(оединен с выходом второго элемента И-НЕ второго блока, формирования управляющих сигналов и с вход.ом синхронизации седьмого триггера второго блока формирования управляющих сигналов, информационный вход которого соединен с выходом третьего триггера второго блока формирования управляющих сигналов и с вторым информационным входом третьего .мультиплексора, третий и четвертый информационные входы которого соединены с третьим информационным входом второго мультиплексора и с выходом элемента ИСКЛЮЧАЮЩЕ ИЛИ, первый вход которого соединен с вькодом шестого триггера второго блока формирования управляющих сигналов, с четвертым, пятым и шестым информационными входами второго мультиплексора, с пятым информационным входом третьего мультиплексора и с первым входом элемента ИЛИ второго блока формирования управляющих сигналов, второй вход которого соединен с выходом седьмого триггера второго блока формирования управляющих сигналов, с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с седьмым и восьмы информационными входами второго мультиплексора, выход элемента ИЛИ второго блока формирования управляющих сигналов соединен с шестым информационным входом третьего мультплексора, седьмой и восьмой информационные входы которого подключены к шине нулевого потенциала, выход пятого триггера второго блока формирования упр вляющих сигналов соединен с вторыми прямым и инверсным информационными входами первого мультиплексора и с вторым прямым входом элемента 2И.ПИ-НЕ второго блока формирования управляющих сигналов, третий прямой и второй инверсный входы которого соединены с

выходом второго элемента И второго блока формирования управляющих сиг налов, выход четвертого триггера второго блока формирования управляющих сигналов соединен с вторым входом пятого элемента И второго блока формирования управляклцих сигналов и с третьими прямьм и инверсным информационными входами первого мультиплексора, четвертые

104523

прямой и инверсный информационные входы которого подключены к шине нулевого потенциала, выходы четвертого и пятого элементов И второго блока формирования управляющих сигналов являются соответственно выходом числоимпульсного кода X , -круговой развертки устройства и выходом числоимпульсного кода Y круго1 вой развертки устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

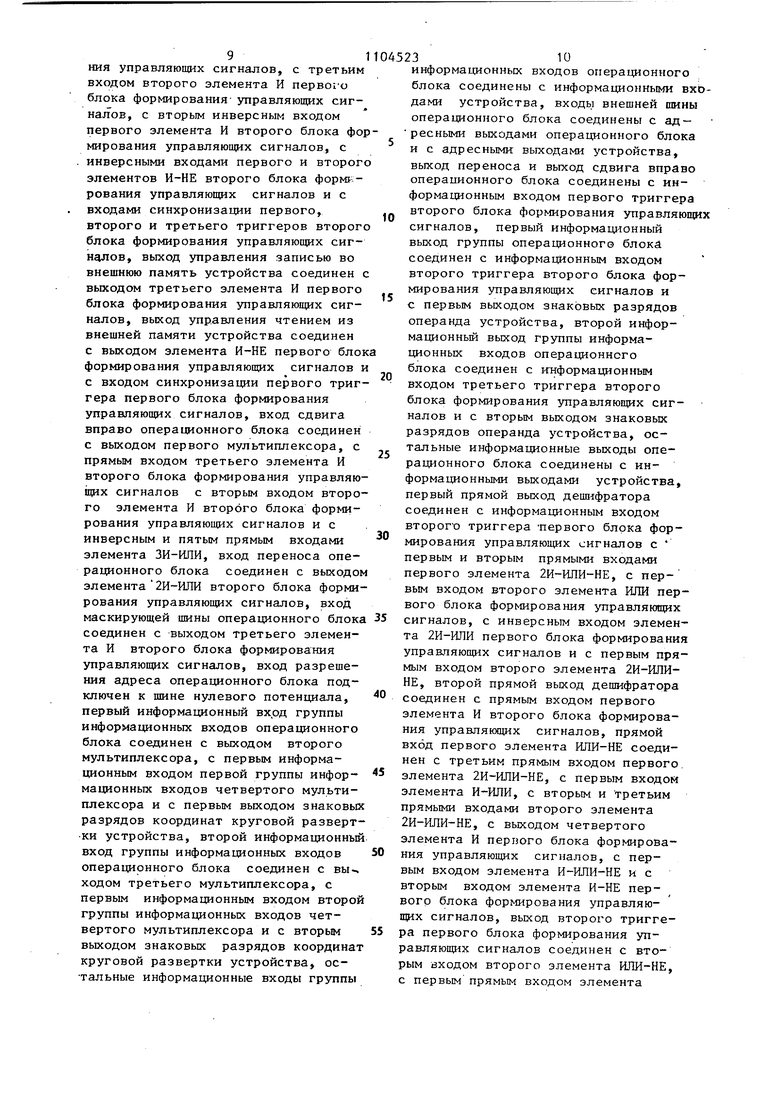

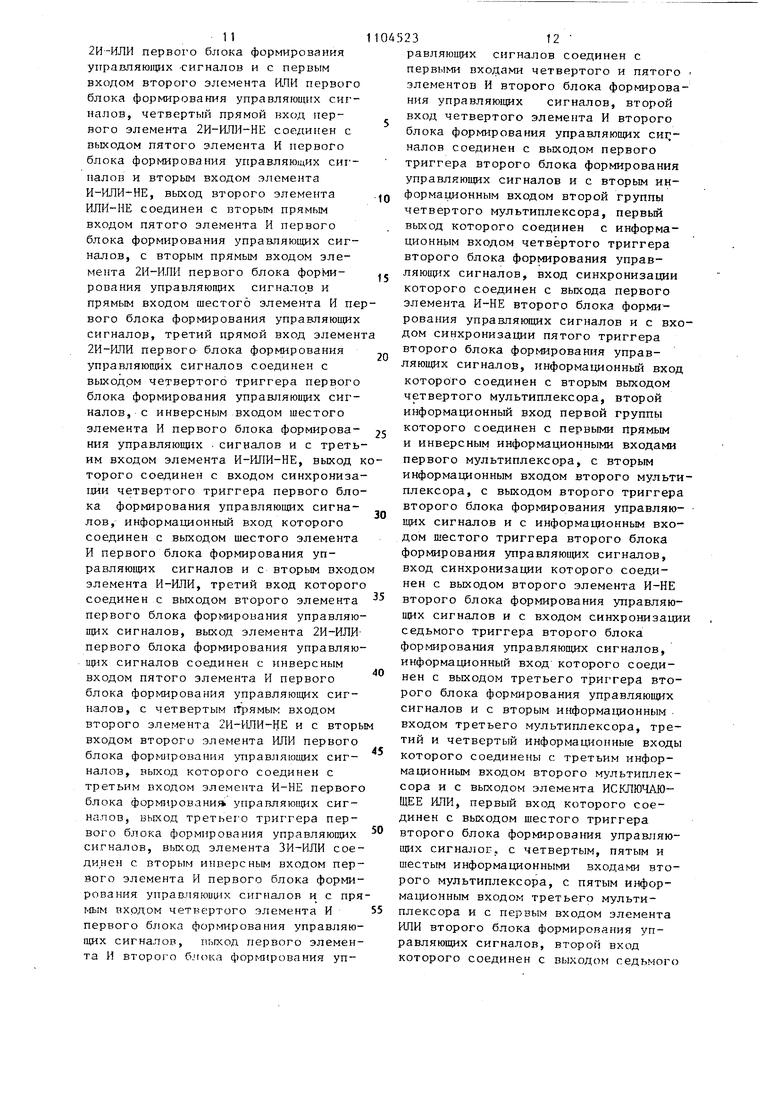

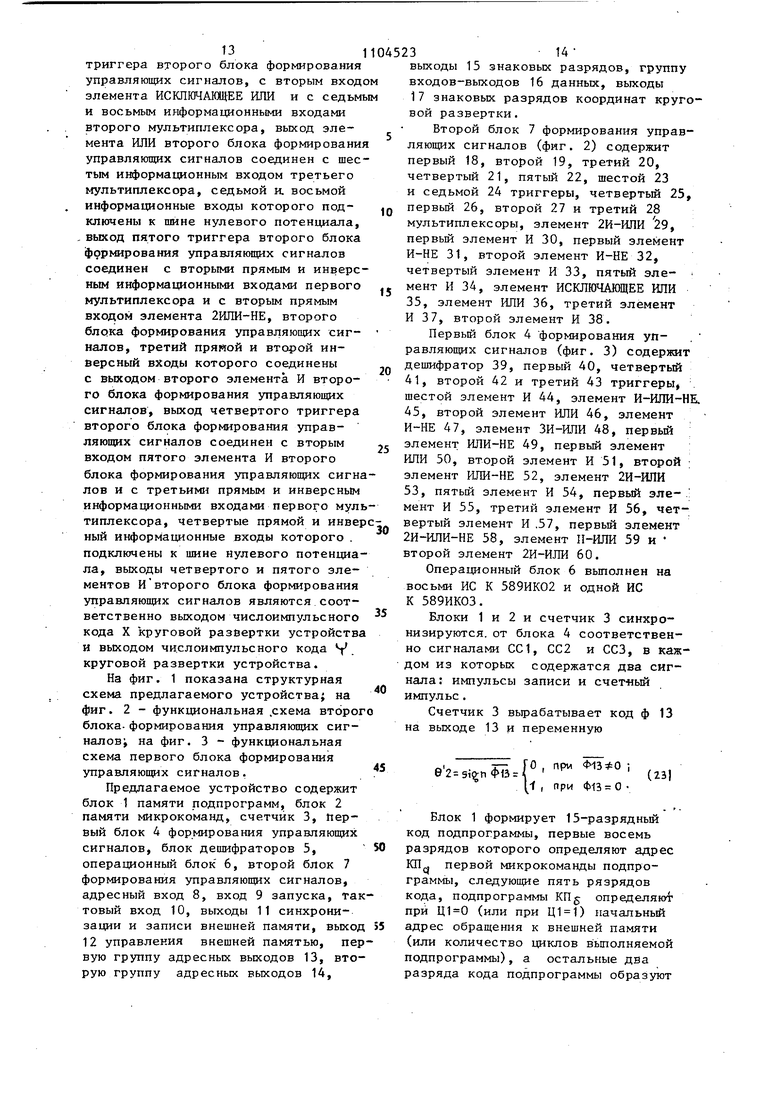

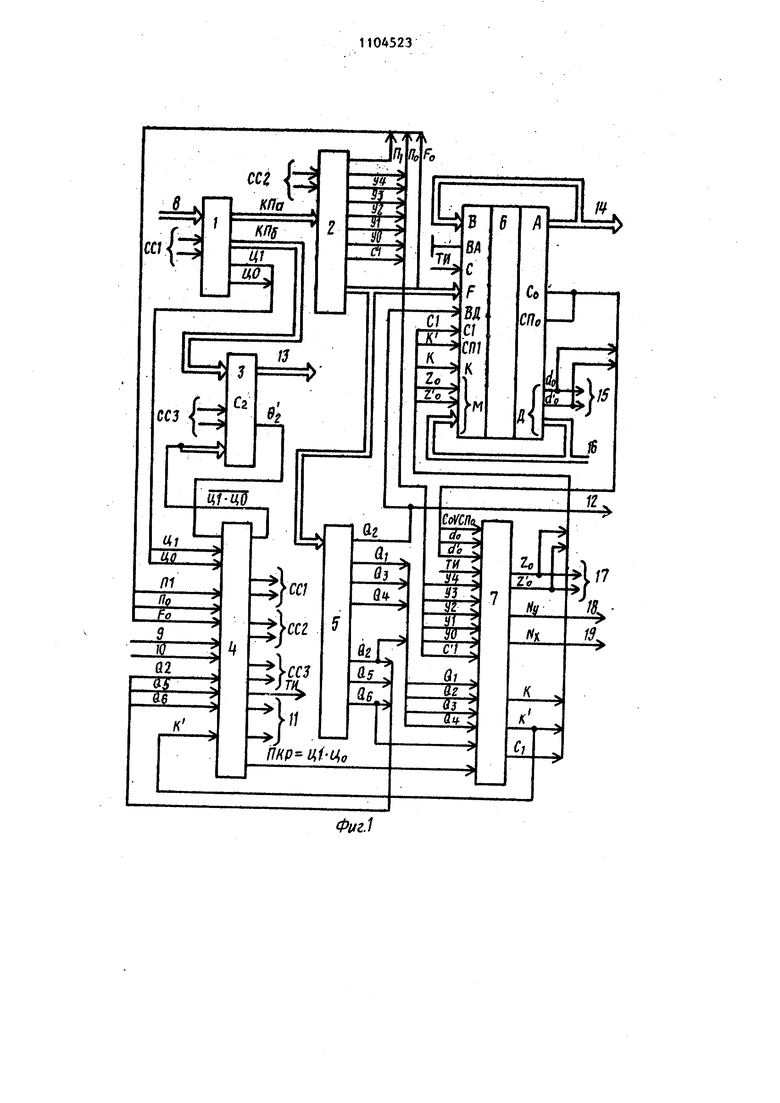

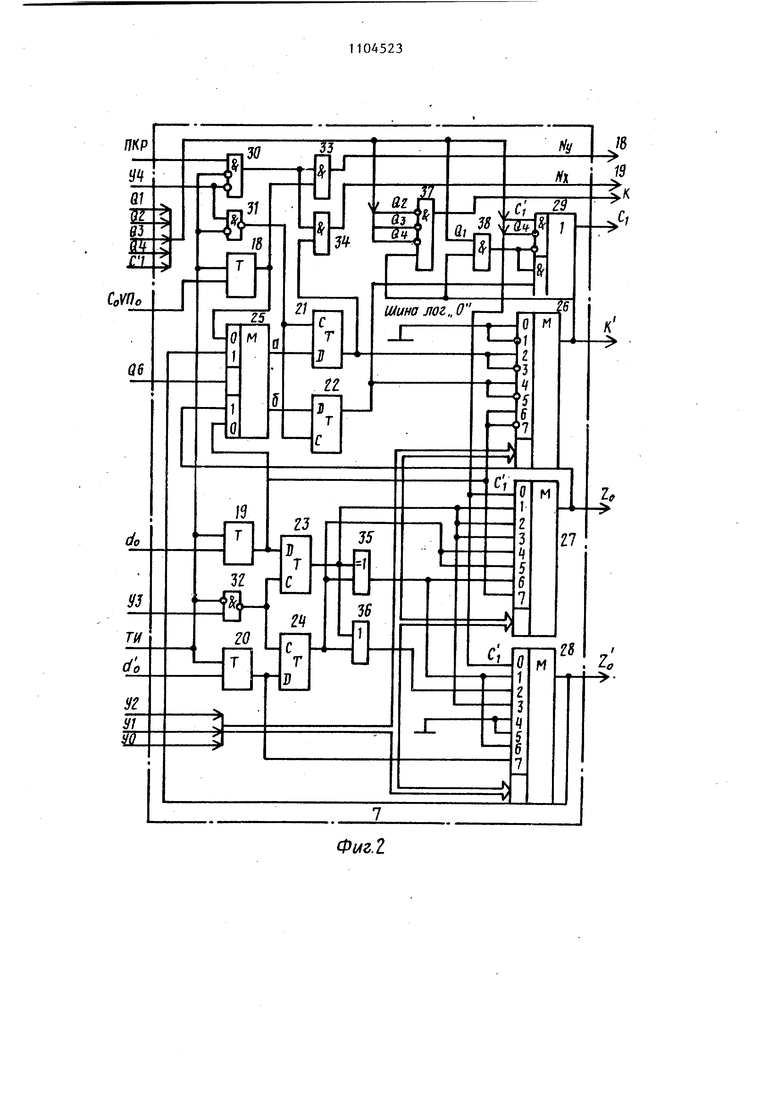

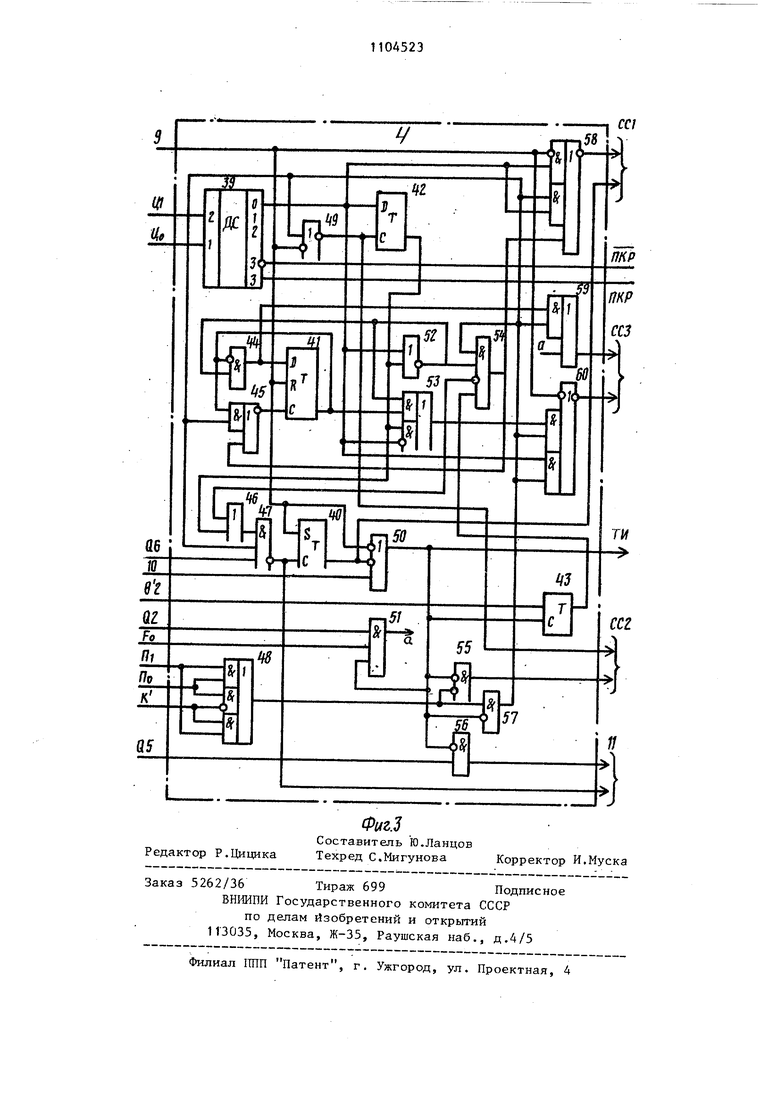

МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО ДЛЯ 1ЩФРОВОГО ПРЕОБРАЗОВАНИЯ КООРДИНАТ, содержащее операционный блок и блок памяти шкpoкoмaнд, первая группа выходов которого соединена с группой входов кода операции операционного блока, отличающееся тем, что, с целью .повышения быстродействия, оно дополнительно содержит блок памяти подпрограмм, счетчик, блок дешифраторов, первый блок формирования управляющих сигналов, содержащей дешифратор, четьре триггера, два элемента ИЛИ-НЕ, два элемента ИЛИ, шесть элементов И, элемент И-НЕ, элемент И-ИЛИ, два элемента 2И-ИЛИ-НЕ, элемент 2И-ИЛИ, элемент И-ИЛИ-НЕ и элемент ЗИ-ИЛИ, и второй блок формирования управляющих сигналов, содержащий четьфе мультиплексора, семь триггеров, пять элементов И, два элемента И-НЕ, элемент ИЛИ, элемент 2И-ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем адресньй вход устройства соединен с адресным входом блока памяти подпрограмм, вход разрешения чтения которого соединен с выходом первого триггера первого блока формирования управляюеИБЛЮГЕКД щих сигналов и с первым инверсным входом первого элемента ИЛИ первого блока формирования управляющих сигналов, тактовый вход блока памяти подпрограмм соединен с вькодом первого элемента 2И-ИЛИ-НЕ, первая и вторая группы информационных выходов блока памяти подпрограмм- соединены соответственно с группой адресных входов блока памяти микрокоманд и с группой информационных входов младших разрядов Счетчика, информационные входы старших разрядов которого соединены с инверсным выходом дешифратора, первьй и второй инфора (5 маи онные выходы блока памяти подпрограмм соединены соответственно (Л с первым и вторым входами дешифратора, вход разрешения чтения блока памяти микрокоманд соединен с выходом первого элемента ИЛИ-НЕ первого блока формирования управляющих сигналов и с входом синхронизации второго триггера, тактовьй вход блока памяти о j микрокоманд соединен с выходом первого элемента И первого блока форСП IsD мирования управляющих сигналов, первый выход второй группы выходов СО блока памяти микрокоманд соединен с первым и вторым входами элемента ЗИ-ИПИ, второй выход второй группы выходов блока памяти микрокомагад соединен с третьим и четвертым входами элемента ЗИ-ИЛИ, третий выход второй группы выходов блока памяти микрокоманд соединен с первым ин- , версным входом первого элемента И второго блока формирования управляющих сигналов и с прямым входом первого элемента И-НЕ второго блока формирования управляющих сигналов.

.

Изобретение относится к вычислительной технике и предназначено для использования в цифровом преобразователе координат (ЦПК) устройства отображения информации (УОИ) метеорологической радиолокационной станции (МРЛ) и может быть использовано при построении специализированных цифровых вычислителей с программируемой обработкой инфорнации, nporpaMNfti вычислительных алгоритмов которых реализуются в дроб ной двоичной арифметике на основе Программ арифметических операций умножения и деления и программ oneраций функциональных преобразований, вьшолняемьж с помощью обращения микропроцессорного устройства к внешней памяти.

Основными вычислительньми функциями Щ1К являются вьшолнение прямой и обратной операций преобразования координат. Выполнение прямой опера.ции заключается в преобразовании

(п+2)-разрядного кода J- и п-разрядного кода г в (п+1)-разрядные прямые коды у и X, а обратной операции - в Преобразовании прямых или дополнительных (п+1)-разрядных кодов И X в (п+2)-разрядньй код 3. и празрядный код г.

Связь между кодом ct и углом d моно определить выражениями

1-а-|(2.,.,.а,д, .

(Я

и oir, - разрядные цифры старщи

-- 1

разрядов кода d. ,

OL РР код приведенного угла

ot - разрядная цифра i-ro

разряда кода ot-np . При выполнении прямой операции разрядные цифры у.и х знаковых разрядов кодов у и X определяются старшими paзpядa я кода х

U1

, V i®r,t

а обратной операции разрядные цифры oij и ci f, определяются знаковыми разрядами кодов у и X

; ;

(3)

ЦПК МРЛ прямая операция- осуществляется или по обычному алгоритму

nRf5 no6|J;

(«-)

Ul npjcSsel|, или по алгоритму круговой развертки

5 ,

(Г)

,|c«so n,

выполняемому обычно на основе алгоритма типа

N,, ,

(И

,|c$s«if. П - функциональный оператор

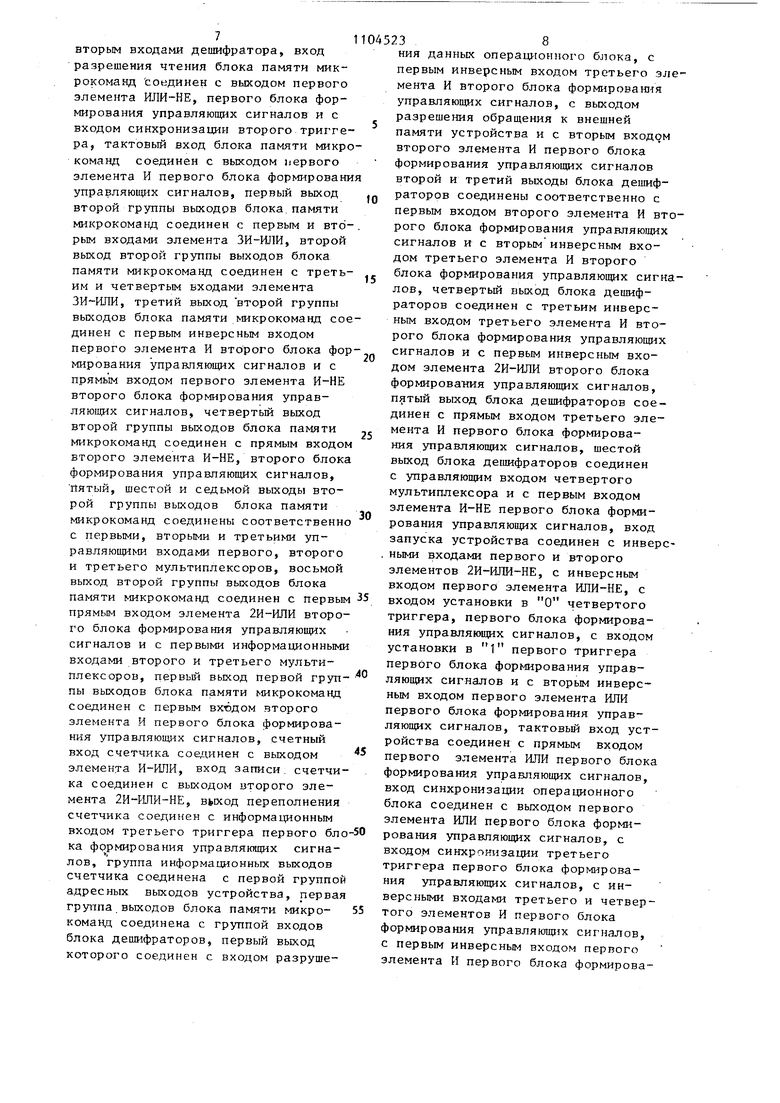

операции умножения, - параллельный двоичный ко е{г, (sin 3Ucos5j,(y),(x N7 - числоимпульсный.код , N,. N, Связь между кодом 2-2-1 2 Ir-t И КОДОМ Nj определяется выражение Z.N , ,, пл(7) Z I под первым из которых можно понимать операцию преобразования кода в код Z, а под вторым - операцию преобразования кода Z в код N представляющий собой последовател ность из N; импульсов, Каждая из операций (7) кыполняется за время Т ,(8) где t - период Частоты следования импульсов кода N . В ЦПК УОИ МРЛ дл тельность каждого периода формиро вания круговой развертки составляе Ztnat Z В ЦПК с программируемой обработ кой информации целесообразно выпол нять обратную операцию по алгоритв котором код А™ находится по му, формуле + (-1) arctg)fl(, ))j,(10 а код г - по формуле г Д (5. Ь , где Д функциональный оператор оп рации деления г на q в фо муле (10) и q на f в формуле (11). В формулах (10) и (11) коды р, f И- логическая перееденная 9/ находятся по формулам pi:9i v9i X ; -91 5 vei X ; , f 01 Stnct V@-|cOSoCi a.91 ©ct, , в которых логическая переменная в определяется выражением Го, при -, (i9l-ixi) И , ,|$| . 3 А Л Если обозначить через сс и исходные кдды операции деления в формуле (10) или (11), то в ЦПК с алгоритмом (10), (11) необходимо в (10) выполнять операцию деления по алгоритму типа 1(е2.|д(0,ё)|уе2 (1-2), (14) а в (11) - по алгоритму типа Д(Й,С)Уе 1 (1-2), (15) где al ив2 логические переменные определяемые выражениями А .-.со ,,и , при lahiif. и и е делимое и делитель у и V 01-t 9f.S V ei-t .. j Алгоритм типа (14) и (15) удобно записать обобщенным алгоритмом lc|-MA{0,)|ve{i-r)i, где 9 - логический переменная, при выполняется алгоритм гипа (t4), а при в 1 алгоритм типа (15). Известно арифметическое устройство (АУ), которое можно использовать в ЦПК УОИ МРЛ для выполнения прямой и обратной операций преобразования координат по параллельным кодам исходных координат 1. Однако такое АУ имеет низкое быстродействие при вьтолнении алгоритма круговой развертки, поскольку в нем каждый такт формирования развертки определяется длительностью цикла вьшолнения прямой операции по параллельным кодам с2. и Р . Наиболее близким по технической сущности к изобретению является микропроцессорное устройство структурной схемы неконвгйерной организации процессора, содержащее блок микропрограммного управления, блок памяти микрокоманд и операционный блок, вход кода операции которого соединен с первым выходом блока памяти микрокоманд, второй выход которого соединен с входом управления адресом следующей микрокоманды бло микропрограммного управления, адресный выход которого соединен с адресным входом блока памяти микро команд, вход и выход переноса и сдвига вправо операционного блока соединен соответственно с выходом и входом признака блока микропрограммного управления 21. Период частоты следования такто вых импульсов обработки информаци в известном устройстве составляет t t(,-t- t(o, 250 НС, длительность сигнала Т, тактового импульса, в течение которой в операцион ном блоке осуществляется вьшолнение микрооперации} Ь(о1 /33нг- длительность сигнала тактового импульса, по от цательному .фронту которог осуществляется занесение результата микрооперации память операционного блок Число микрокоманд, требуемое с учетом микрокоманд подпрограммы оп рации усечения с округлением разрядного кода в п-разрядный код в известном микропроцессорном устрой стве для вьшолнения программы умно жения или деления, составляет примерно 50. Поэтому в этом устройств для t 250 НС, m 14 (m - разрядность модуля произведения Или частного перед выполнением подпрограммы усечения с округлением) и п 10 (п - разрядность модуля результата выполнения программы операции умножения или деления).Максимальная длительность вьшолнения программы операции умножения оцен вается величиной ) 6-14)30,25 МКС 32 МКС а операции деления - величиной t Ar7poT(50-12)+12.14-0,25 мкм 51,25 МКС. С помощью известного микропроцессорного устройства алгоритм круговой развертки (5) можно реали зовать на основе выполнения алгоритма типа (4), что обеспечивает частоту следования импульсов кода N. с периодом 64 МКС. прот .про 3 Недостатком известного микропроцессорного, устройства является низкое быстродействие, обусловленное тем, что функции БМУ недостаточно полно реализуют функциональные возможност операционного блока при . выполнении в ЦПК УОй МРЛ, например, программы алгоритма круговой развертки, программы алгоритма операции умножения и программы обобщенного алгоритма (18) операции деления. Цель изобретения - повышение быст.. родействия устройства. Поставленная цель достигается тем, что в микропроцессорное уст- . ройство для цифрового преобразования координату содержащее операционный блок и блок памяти микрокоманд первая группа выходов которого соединена с группой входов кода операции операционного блока, введены блок памяти подпрограмм, счетчик, блок дешифраторов, первый блок- формирования управляющих сигналов, содержащий дешифратор четыре триггера, два элемента ИЛИ-НЕ, два элемента ИЛИ, щесть .элементов И, элемент И-НЕ, элемент И-ИЛИ, два элемента 2И-ИЛИ-НЕ, элемент 2И-ИЛИ, элемент И-ИПИ-НЕ и элемент ЗИ-Ш1И, и второй блок формирования управляющих сигналов, содержадай четыре мультиплексора, семь триггеров, пять элементов И, два элемента И-НЕ, элемент ИЛИ, элемент 2И-ШШ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем адресный вход устройства соединен с адресным входом блока подпрограмм, вход разрешения чтения которого соединен с выходом первого триггера первого блока формирования управляющих сигналов и с первым инверсным входом первого элемента ИЛИ первого блока формирования управляющих сигналов, тактовый вход блока памяти подпрограмм соединен с выходом первого элемента 2И-Ш1И-НЕ, первая и вторая группы информационных выходов блока памяти подпрограмм соединены соответственно с группой адресных входов блока памяти микрокоманд и с группой информационных входов младших разрядов счетчика, информационные входы старших разрядов которого соединены с инверсным выходом дешифратора, первый и второй информационные выходы блока памяти подпрограмм соединены соответственно с первым и вторым входами дешифратора, вход разрешения чтения блока памяти микрокоманд соединен с выходом первого элемента Ш1И-НЕ, первого блока формирования управляющих сигналов и с входом синхронизации второго триггера, тактовый вход блока памяти микро команд соединен с выходом первого элемента И первого блока фopм ipoвaни управляющих сигналов, первый выход второй группы вькодов блока памяти микрокоманд соединен с первым и вторым входами элемента ЗИ-ИЛИ, второй вькод второй группы выходов блока памяти микрокоманд соединен с третьим и четвертым входами элемента ЗИ-ИЛИ, третий выход второй группы выходов блока памяти микрокоманд сое динен с первым инверсным входом первого элемента И второго блока фор мирования управляющих сигналов и с прямьм входом первого элемента И-НЕ второго блока формирования управляющих сигналов, четвертый выход второй группы выходов блока памяти микрокоманд соединен с прямым входом второго элемента И-НЕ, второго блока формирования управляющих сигналов, Пятый, шестой и седьмой выходы второй группы выходов блока памяти микрокоманд соединены соответственно с первыми, вторыми и третьими управляющими входами первого, второго и третьего мультиплексоров, восьмой выход второй группы выходов блока памяти микрокоманд соединен с первым прямым вхрдом элемента 2И-ИЛИ второго блока формирования управляюш х сигналов и с первыми информационными входами второго и третьего мультиплексоров, первъв1 выход первой группы выходов блока памяти микрокоманд соединен с первым входом второго элемента И первого блока формирования управляющих сигналов, счетный вход счетчика соединен с выходом элемента И-ИЛИ, вход записи, счетчи ка соединен с выходом второго элемента 2И-ИЛИ-НЕ, выход переполнения счетчика соединен с информационным входом третьего триггера первого бл ка формирования управляющих сигналов, группа информационных выходов счетчика соединена с первой группой адресных выходов устройства, первая группа.выходов блока памяти микрокоманд соединена с группой входов блока дешифраторов, первый выход которого соединен с входом разруше38ния данных операционного блока, с первым инверсным входом третьего элемента И второго блока формирова1шя управляющих сигналов, с выходом разрешения обращения к внешней памяти устройства и с вторым входом второго элемента И первого блока формирования управляющих сигналов второй и третий выходы блока дешифраторов соединены соответственно с первым входом второго элемента И второго блока формирования управляющих сигналов и с вторым инверсным входом третьего элемента И второго блока формирования управляющих сигналов, четвертый выход блока дешифраторов соединен с третьим инверсным входом третьего элемента И второго блока формирования управляющих сигналов и с первым инверсным входом элемента 2И-ИЛИ второго блока формирования управляюш 1х сигналов, пдтый выход блока дешифраторов соединен с прямым входом третьего элемента И первого блока формирования управляющих сигналов, шестой выход блока дешифраторов соединен с управляющим входом четвертого мультиплексора и с первым входом элемента И-НЕ первого блока формирования управляюпщх сигналов, вход запуска устройства соединен с инверсными входами первого и второго элементов 2И-ИЛИ-НЕ, с инверсным входом первого элемента ИЛИ-НЕ, с входом установки в О четвертого триггера, первого блока формирования управляющих сигналов, с входом установки в 1 первого триггера первого блока форьдарования управляющих сигналов и с вторым инверсным входом первого элемента ИЛИ первого блока формирования управляющих сигналов, тактовый вход устройства соединен с прямым входом первого элемента ИЛИ первого блока формирования управляющих сигналов, вход синхронизации операционного блока соединен с выходом первого элемента ИЛИ первого блока формирования управляющих сигналов, с входом синхронизации третьего триггера первого блока формирования управляющих сигналов, с инверсными входами третьего и четвертого элементов И первого блока ормирования управляющих сигналов, с первым инверсным входом первого элемента И первого блока формирования управляющих сигналов, с третьим входом второго элемента И первого блока формирования управляющих сигналов, с вторым инверсным входом первого элемента И второго блока фо мирования управляющих сигналов, с инверсными входами первого и второг элементов И-НЕ второго блока формк.рования управляющих сигналов и с входами синхронизации первого, второго и третьего триггеров второг блока формирования управляющих сиг- , выход управления записью во внешнюю память устройства соединен выходом третьего элемента И первого блока формирования управляющих сигналов, выход управления чтением из внешней памяти устройства соединен с выходом элемента И-НЕ первого бло формирования управляющих сигналов с входом синхронизации первого триг гера первого блока формирования управляющих сигналов, вход сдвига вправо операционного блока соединен с выходом первого мультиплексора, с прямым входом третьего элемента И второго блока формирования управляю щих сигналов с вторым входом второ го элемента И второго блока формирования управляющих сигналов и с инверсным и пятым прямым входами элемента ЗИ-ИЛИ, вход переноса операционного блока соединен с выходо элемента2И-ИЛИ второго блока форми рования управляющих сигналов, вход маскирующей шины операционного блок соединен с выходом третьего элемента И второго блока формирования управляющих сигналов, вход разрешения адреса операционного блока подключен к шине нулевого потенциала, первый информационный вход группы информационных входов операционного блока соединен с выходом второго мультиплексора, с первым информационным входом первой группы информационных входов четвертого мультиплексора и с первым выходом знаковы разрядов координат круговой разверт ки устройства, второй информационны вход группы информационных входов операционного блока соединен с выходом третьего мультиплексора, с первым информационным входом второ группы информационных входов четвертого мультиплексора и с вторьм выходом знаковых разрядов координа круговой развертки устройства, остальные информационные входы группы информационных входов операционного блока соединены с информационными входами устройства, входы внешней шины операционного блока соединены с ад - ресными выходами операционного блока и с адресными выходами устройства, выход переноса и выход сдвига вправо операционного блока соединены с информационным входом первого триггера второго блока формирования управляющих сигналов, первый информационный выход группы операционного блоки соединен с информационным входом второго триггера второго блока формирования управляющих сигналов и с первым выходом знаковых разрядов операнда устройства, второй информациоиньш выход группы информационных входов операционного блока соединен с информационным входом третьего триггера второго блока формирования управляющих сигналов и с вторым выходом знаковых разрядов операнда устройства, остальные информационные выходы операционного блока соединены с информационными выходами устройства, первый прямой выход дешифратора соединен с информационным входом второго триггера первого блока формирования управляющих сигналов с первым и вторым прямыми входами первого элемента 2И-ИЛИ-НЕ, с первым входом второго элемента ИЛИ первого блока формирования управляющих сигналов, с инверсным входом элемента 2И-ИЛИ первого блока формирования управляющих сигналов и с первым прямым входом второго элемента 2И-ИЛИНЕ, второй прямой выход дешифратора соединен с прямым входом первого элемента И второго блока формирования управляющих сигналов, прямой вход первого элемента ИЛИ-НЕ соединен с третьим прямым входом первого. элемента 2И-ИЛИ-НЕ, с первым входом элемента И-ИПИ, с вторым и третьим прямыми входами второго элемента 2И-ИЛИ-НЕ, с выходом четвертого элемента И nepiioro блока формирования управляющих сигналов, с первым входом элемента И-ИЛИ-НЕ и с вторым входом элемента И-НЕ первого блока формирования управляющих сигналов, выход второго триггера первого блока формирования управляющих сигналов соединен с вторым входом второго элемента ИЛИ-НЕ, с первым прямым входом элемента 2И-ИЛИ первого блока формирования У1травляю1цнх -сигналов и с первым входом второго элемента ИЛИ первого блока формирования управляющ1тх сигналов, четвертый прямой вход первого элемента 2И-ИЛИ-НЕ соединен с выходом пятого элемента И ттервого блока формирования управляющих ситналов и вторым входом элемента И-ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с вторым прямым входом пятого элемента И первого блока формирования управляющтих сигналов, с вторым прямым входом элемента 2И-ИЛИ первого блока формирования управляющих сигналов и прямым входом шестого элемента И пер вого блока формирования управляющих сигналов, третий прямой вход элемент 2И-ИПИ первого блока формирования управляющих сигнапов соединен с выходом четвертого триггера первого блока формирования управляюищх сигналов, с инверсным входом шестого элемента И первого блока формирования управляющих . сигналов и с третьим входом элемента И-ИЛИ-НЕ, выход к торого соединен с входом синхронизапии четвертого триггера первого блока формирования управляющих сигналов, информационный вход которого соединен с выходом шестого элемента И первого блока формирования управляющих сигналов и с вторым вх-одо элемента И-ИЛИ, третий вход которого соединен с выходом второго элемента первого блока формирования управляющих сигналов, вьсход элемента 2И-ИЛИ первого блока формирования управляю щих сигналов соединен с инверсным входом пятого элемента И первого блока формирования управляющих сигналов, с четвертым входом второго элемента 2И-ИПИ-НЕ и с вторы входом второго элемента ИЛИ первого блока формирования управляючщх сигналов, выход которого соединен с третьим входом элемента И-НЕ первого блока формирования управляющих сигналов, выход третьего триггера первого блока формирования управляющих сигналов, выход элемента ЗИ-ИЛИ соеди,нен с вторым инверсным входом первого элемента И первого блока формирования у1травляющих сигналов и с пря мь;м входом четвертого элемента И первого блока формирования управляющих сигналов, пьгход первого элемен та И второго б:г( формирования управляющих сигналов соединен с первыми входами четвертого и пятого элементов И второго блока формирования управляющих сигналов, второй вход четвертого элемента И второго блока формирования управляющих сигналов соединен с выходом первого триггера второго блока формирования управляющих сигналов и с вторым информационным входом второй группы четвертого мультиплексора, первый выход которого соединен с информационнь1м входом четвертого триггера второго блока формирования управляющих сигналов, вход синхронизации которого соединен с выхода первого элемента И-НЕ второго блока формирования управляющих сигналов и с входом синхронизации пятого триггера второго блока формирования управляющих сигналов, информационный вход которого соединен с вторым выходом четвертого мультиплексора, второй информационный вход первой группы которого соединен с первыми прямым и инверсным информационными входами первого мультиплексора, с вторым информационным входом второго мультиплексора, с выходом второго триггера второго блока формирования управляющих сигналов и с информационным входом шестого триггера второго блока формирования управляюш 1х сигналов, вход синхронизации которого соединен с выходом второго элемента И-НЕ второго блока формирования управляющих сигналов и с входом синхронизации седьмого триггера второго блока формирования управляющих сигналов, информационный вход которого соединен с выходом третьего триггера второго блока формирования управляющих сигналов и с вторым информационным входом третьего мультиплексора, третий и четвертый информационные входы которого соединены с третьим информационным входом второго мультиплексора и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом шестого триггера второго блока формирования управляющих сигналор, с четвертым, пятым и шестым информационными входами второго мультиплексора, с пятым информационным входом третьего мультиплексора и с первым входом элемента ИЛИ второго блока формирования управляющих сигналов, второй вход которого соединен с выходом седьмого триггера второго блока формирования управляющих сигналов, с вторым входо элемента ИСКПЮЧАЮД-ЕЕ ИЛИ и с седьмы и восьмым и1-1формационнь ми входами второго мультиплексора, выход элемента ИЛИ второго блока формирования управляющих сигналов соединен с шестым информационным входом третьего мультиплексора, седьмой а восьмой информационные входы которого подключены к шине нулевого потенциала, выход пятого триггера второго блока формирования управляющих сигналов соединен с вторыми прямым и инверсным информационными входами первого мультиплексора и с вторым прямым входом элемента 2ИЛИ-НЕ, второго блока формирования управляющих сигналов, третий прямой и второй инверсный входы которого соединены с выходом второго элемента И второго блока формирования управляющих сигналов, выход четвертого триггера второго блока формирования управляющих сигналов соединен с вторым входом пятого элемента И второго блока формирования управляющих сигна лов и с третьими прямым и инверсным информационными входами первого муль типлексора, четвертые прямой и инвер ный информационные входы которого . подключены к шине нулевого потенциала, выходы четвертого и пятого элементов Ивторого блока формирования управляюш 1х сигналов являются соответственно выходом числоимпульсного кода X круговой развертки устройства и выходом числоимпульсного кода V. круговой развертки устройства. На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 - функциональная .схема второг блока, формирования управляющих сигналов j на фиг. 3 - функциональная схема первого блока формирования управляюш;их сигналов. Предлагаемое устройство содержит блок 1 памяти подпрограмм, блок 2 памяти микрокоманд, счетчик 3, первый блок 4 формирования управляюш 1х сигналов, блок дешифраторов 5, операционный блок 6, второй блок 7 формирования управляющих сигналов, адресный вход 8, вход 9 запуска, так товый вход 10, выходы 11 синхронизации и записи внешней памяти, выход 12 управления внешней памятью, пер вую группу адресных выходов 13, вторую группу адресных выходов 14, 1 3 выходы 15 знаковых разрядов, группу входов-выходов 16 данных, выходы 17 знаковых разрядов координат круговой развертки. Второй блок 7 формирования управляющих сигналов (фиг. 2) содержит первый 18, второй 19, третий 20, четвертый 21, пятый 22, шестой 23 и седьмой 24 триггеры, четвертый 25, первый 26, второй 27 и третий 28 мультиплексоры, элемент 2И-ИЛИ 29, первьй элемент И 30, первый элемент И-НЕ 31, второй элемент И-НЕ 32, четвертый элемент И 33, пятый эле- мент И 34, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 35, элемент ИЛИ 36, третий элемент И 37, второй элемент И 38. Первый блок 4 формирования уп- . равляющих сигналов (фиг. 3) содержит дешифратор 39, первый 40, четвертый 41, второй 42 и третий 43 триггеры, шестой элемент И 44, элемент И-ИЛИ-НЕ. 45, второй элемент ИЛИ 46, элемент И-НЕ 47, элемент ЗИ-ИЛИ 48, первый элемент ИЛИ-НЕ 49, первый элемент ИЛИ 50, второй элемент И 51, второй ; элемент ИЛИ-НЕ 52, элемент 2И-ИЛИ 53, пятый элемент И 54, первый эле-. мент И 55, третий элемент И 56, четвертый элемент И ,57, первый элемент 2И-ИЛИ-НЕ 58, элемент И-ИЛИ 59 и второй элемент 2И-ИЛИ 60. Операционный блок 6 выполнен на восьми ИС К 589ИК02 и одной ИС К 589ИКОЗ. Блоки 1 и 2 и счетчик 3 синхронизируются, от блока 4 соответственно сигналами СС1, СС2 и ССЗ, в каждом из которых содержатся два сигнала: импульсы записи и счет-ный импульс. Счетчик 3 вырабатывает код ф 13 на выходе 13 н переменную прм 1 при Блок 1 формирует 15-разрядный код подпрограммы, первые восемь разрядов которого определяют адрес КП первой микрокоманды подпрограммы, следующие пять рязрядов кода, подпрограммы КП определяют при (или при ) начальный адрес обращения к внешней памяти (или количество циклов выполняемой подпрограммы), а остальные два разряда кода подпрограммы образуют 15 код , определяющий тип подпрограммы так, что при выполняется простая подпрограмма, при Ц 2 - циклическая подпрограмма типа алгоритма операции умножения или деления с количеством циклов от двух до 33, а при Ц 3 - циклическая подпрограмма формирования круговой развертки с количеством циклов 1024. Блок 2 вырабатывает 15-разрядный код микрокоманды. Первые семь разрядов этого кода образуют код F F6 F5 F4 F3 F2 F1 FO микрооперации, восьмой разряд представляет сигнал Cl, следующие пять разрядов образуют код уЗ у2 yVyO управления флажковой логикой формирователя 7, а два последних разряда образуют код признака конца подпрограммы. . Блок дешифраторов 5 по коду F формирует сигналы Q1 F6-F5-H-F3-F2-F -F-O; Q2 T6-F5-F4-F3-F2-FT; Q3 F6-F5-F4-F3-F2-F1; Q4 F6-F5-F4-F3- 2-F1; Q5 F6-F5-F4-F3-F2-Fl - FO; F5-F4 - F3 F2 - FT-FO. В операционном блоке 6 (как и в ИС К589ИК02) можно функционально вьщелить дешифратор микрооперации, два мультиплексора кодов, арифмети ко-логическое устройство,одиннадцат регистров (RO, R1,...,R9,T) общего назначения, аккумулятор (АС) регист адреса (РА) и две буферные схемы с тремя ост6яниями для вьщачи кода от АС на шину Д при и кода от РА на шину А при . Операционны блок 6 имеет входные шины В и М данных, маскирующий вход К, адресну шину А, шину Д (с шины Д при снимается.код от АС, а при код от внешней памяти), шину кода F микрооперации, вход С1 переноса, вх cm сдвига вправо, выход Со переноса, выход СПо сдвига вправо и вход синхронизации. По входным сигналам и кодам опер ционный блок 6 реализует функции, предстаатенные в табл. 1-3. У блока 6 выходы СО и СПо объединены, поскольку при (при Q3 1) разрешен выход Со (выход СПо), 316 a выход СПо(Со) находится в третьем СОСТОЯНИЕ . На блок 7 поступает код Y , сигнал dg и сЗ знаковых разрядов в модифицированном коде (прямом, обратном или дополнительном), сигнады С1, Covcno, е 1, .. ., 94, 66, признак круговой развертки (ПКР Ц1-Цо) i и тактовые импульсы. По .входным сигналам блок 7 вьфабатывает маскирующий сигнал К, сигнал переноса С1, сигнал к СП1 сдвига вправо знаковые разряды z -z. (T-Q- знаковый разряд, - дополнительный знаковый разряд модифищ рованного кода), а при генерирует импульсы числоимпульсных, кодов N круговой развертки. В блоке 7 флажки Ф 18 - Ф 24 вырабатываются триггерами 18-24, функции управления флажками осуществляются в соответствии с табл. 4, сигналу К ZP и 2о вырабатьтают мультиплексоры 26-28 согласно табл. 5 , мультиплексор 25 вырабатывает флажкиФ25ч аь-ф18 vQfe-Zp Ф255 01-Ф19 VQ6-Z элементы 35 и 36 - флажки ФЭ5-Ф25 ® Ф24 Ф36 Ф2Э V ф24 а элементы 37 и 29 - сигналы К кЧа2 VQ5VQ4 ) ci c4-a4-Qi-Ki V Фг2-й-г к На блок 4 поступают коды Ц и П, сигналы Q2, ТО, Q2, Q5, Q6, К,тактовые импульсы ТИ 10 с входа 10 и импульс запуска , совпадаюпщй во времени с одним из сигналов ТИ 10 О, имеющим длительность ,e(33 НС, 50 не) . По входным сигналам в блоке 4 дешифр атор 39 вырабатывает сигналы Ц1-ЦО, Ц1-Цо ПКР, Ц1-По ПКР, триггеры Т40 - Т 43 - сигналы 40 43, элементы 44, 46, 48, 52, 53 сигналы -Э52, V Э53, Э48 П1По vnO-КV П1-К Э52 ЦТ. ЦоГут42, Э53 Т41-352 vT42iTTUo, а элементы 45,47, 49, 50, 51, 54 60 - при Т40 1 импульсы И45 О, И47 0,И49 О, , И51 },. , , , , , , Ибо 0 (равенство импульса логического О означает импульсы отрицательной полярности, а гавенст во импульса логической 1 означает импульсы положительной полярности) . При этом лпя и отсутствии И9 (при Т40 О ) ТИ10, а каждый из остальных импуль сов вырабатывается в соответствующи моменты времени по сигналу Кроме того, И49 и И60 вырабатывают ся по И9, по которому при Ц1 Цо 1 вырабатывается И58. Запись информации в триггер-защелку 43 блока 4 и в триггеры-защелки 18-20 блока 7 осуществляется фиксировано в течение (в течение ТИ О триггеры-защелки помня информацию, записанную в них в тече ние ТИ 1) запись информации в D-триггеры 41 и 42 блока 4. в тригг ры 21 - 24 блока 7 осуществляется в некоторые моменты времени после окончания положительных фронтов импульсов, действующих на синхронизирующих входах этих триггеров, Запись результата микрооперации в память операционного блока 6 осуществляется в некоторый момент времени после окончания отрицательного фрон та импульса ТИ. При 33 НС :i(o) SOHC период частоты следования тактовых импульсов ТИ10 оценивается величиной t 250 НС , t,,+ t tj где i длительность задержки установления сигналов на вы ходах блока 2, отсчитываемая от отрицательного фронт импульса tf 70 НС длител1гность задер ки установления сигналов на выхода блока дешифраторов 5; t3, 20 НС задержка распространения сигнала через элемент 37j t., 50 НС время установления сигнала на маскирующем входе операционного блока 6. Каждая программа, выполняемая в устройстве, может состоять из одной или нескольких подпрограмм, каждая из которых может состоять из одной или нескольких микрокоманд. Переход к первой микрокоманде любой подпрограммы производится по И49 О, а переход от текущей микрокоманды к последующей микрокоманде подпрограммы осуществляется по положительному фронту И55 1. Каждый переход от текущей подпрограммы к следующей производится согласно табл. 6. так, что в последней микрокоманде каждой подпрограммы вьфабатывается сигнал Э48 1 и импульс И57 1 конца текущей н начала последующей программы. В предлагаемом устройстве шесть микрокоманд для определенных Rимеют специфическое назначение, что отражено в табл. 7. Перед вьтолнением любой из программ устройство находится в режиме ожидания: в блоке 2, счетчике 3, операционном блоке 6 и блоке 7 содержится информация, обусловленная предисторией работы устройства. Блок 4 вырабатывает сигнал ТИ 1 и сигнал Т40 О, осуществляющий фиксированную запись программного кода Ф 8 с входа 8 в блок 1, который вырабатьшает коды КП первои подпрограммы программы, данной кодом Ф8. Запуск устройства производится по И9 О, по которому устанавливаются сигналы Т40 1, Т41 О,и вырабатываются установочные импульсы И49 О и Ибо 0. После окончания И9 вырабатываются ТИ ТИ10 в течение всего цикла вьпполнеиия программы. При Ц1 Цо 1 выполняется обычная подпрограмма, в начале которой вырабатываются импульсы И49, И58 Ибо или по И9, или по И57, а при Ц1 Цо О - циклическая подпрограмма В конце простой подпрограммы или в конце каждого цикла циклической подпрограммы вьфабатываются И49 и И57. При выполнении циклической подпрограммы в начале первого цикла вырабатывается 60 по И9 или по И57, а в конце предпоследнего цикла выра батывается И58 по И54, которьш генерируется по И57 при и Э53 0. Количество циклов циклической подпрограммы определяется выражениемразрядный коэффициент де разряда кода Л (кол Л деляется кодом KTlg и сиг налом Ц1Цо), занесенного в счетчик 3 по И60 в нача первого цикла. При выполнении микрокоманды с FO Q2 1 генерируется И59 по И и микрокоманды с генерируется И56, по положительному фронту которого осуществляется запись во внешнем ОЗУ кода, снимаемого с входов-выходов 16 и 17. В конце последней микрокоманды последней подпрограммы выполняется микрокоманда с 96 1 (табл. 6 и 7 в конце которой генерируется им- пульс конца программы И47, после окончания которого триггер 40 уста навливается в О и сигналом Т40 переводит работу устройства в.режи ожидания. Следующая программа начинается -с приходом очередного И9 через время , где N - натуральное число. Рассмотрим вьшолнение программы алгоритма круговой развертки, программы алгоритма операции умножения и программы обобщенного алгоритма (18) операции деления. Программа выполнения алгоритма (6) круговой развертки (табл.8) состоит из циклической подпрограммы 1 с количеством циклов 1024 и подпрограммы 2 конца программы. Перед началом выполнения программы 1 в памяти блока 6 содержат ся коды (R6) (Т) 0,5 (АС) Isinc l , (РА) Icosctf, триггеры 23 и 24 блока 7 находятся в состояниях Т23 о.и Т24 с(р, соответственно. В течение подпрограммы 1 (ПКР 1) производится на основе алгоритма цифрового интегратора с параллельным переносом кода числа из регистра подинтегральной функции выполнение алгорит 1а круговой разверткиN,,eni(s1ho6|-N2 a N eni jcoso |-N -foi , где ent означает операцию вьщел ния целой части числа, заключенного в скобках При выполнении программы 1 блок 6 выработает в модулях 16 разрядных кодов, причем старший разряд каждого из его регистров R6, Т, АС, DA имеет вес 0,5, знаковые разряды кодов N, и N вьфабатываются по содержимому триггеров 23 и 24 элементом 35 и мультиплексорами 27 и 28 согласно формулам (2), т.е. ,, Z Хд, а очередные импульсы кодов N и N вырабатываются по импульсу конца каждой второй микрокоманды полупрограммы 1; Это обеспечивает частоту следования импульсов кода N с периодом 0,5 МКС Программа операции умножения (табл. 9) модифицированных прямых кодов S и t осуществляется по алгоритму Горнера с анализом младшего разряда множителя и сдвигам вправо суммы частичных произведений и множителя. Программа содержит подпрограмму 1 ввода множимого а и множителя b , подпрограмму 2 подготовки, циклическую подпрограмму 3 умножения, подпрограмму 4 усечения с округлением и устранением переполнения, заключающуюся в получении из ич 14-разрядного кода 10-разрядного кода 0. I С U 1-2, и подпрогра:мму 5 конца программы. Программа операции деления по обобщенному алгоритму типа (18). В машинной арифметике для выполнения операции деления наибольшее распространение получил алгоритм деления со сдвигом остатка и его автоматическим восстановлением. Этот алгоритм может выполняться или в модулях кодов или в дополнительных кодах, а в предлагаемом случае предпочтительно использовать такую модификацию известного алгоритма, которая позволила бы по дополнительным исходным кодам алгоритма (18) определить частное непосредственно в прямом коде. Если (18) выполнить точно, то получают частное 161 e-(i-z Из (33) при находят модуль делимого Iul (34) нулевой остаток |t hl |-lO| ) (35 и первый остаток (l-cV Из (36) определяют , при -iai-i:c. ,при . .Hi%i5 i-i i i«t-(i-c -f-c;;2) где разрядная цифра знакового разряда первого остатка Согласно (36) и (37) второй остаток в подобен первому. Это позволяет методом математической индукции легко доказать, что определение каждой разрядной цифры Сможно представить в виде рекуррент ной формулы ., gTu (-j)f-i. Hgi; г - i 0 вычисления no которой завязываются с нулевой разности (35), т.е. Cj 1, при Со 0. Программа операции деления (табл. 10) выполняется с использо ванием алгоритма (38) и содержит подпрограмму 1 ввода кодов м и Ъ в модифицированном дополнительном коде, подпрограмму 2 подготовки, циклическую подпрограмму 3 алгорит ма (38), подпрограмму 4 усечения с округлением, подпрограмму 5 (или 5) устранения переполнения для б 0 (или для 0 1) и подпрограмму 6 конца программы. В результате выполнения подпрограммы 2 в блоке 6 содержится (Т) 2 , (RT) (PA) -|gl, (R8) (АС)0, R6 61 92... (где 61 и 02 определяются согласно форму лы (16)), а триггеры 22 - 24 форми рователя находятся в состояниях Ф22 О С, Ф23 OQ, ,. Вьтолнение подпрограммы 4 и 5 (или 5) заключается в получении из tTi 14-разрядного кода, образованног старшими разрядами кода 10-разрядного кода - С,-2 . 1 1 Подпрограмма 5 программы операции умножения (табл. 9) подобна Подпрограмма 6 (табл. 10) программы операции деления. В первой микрокоманде подпрограммы 6 операции деления с выходов мультиплексоров 27 и 28 в знаковые разряды АС заносится разрядная цифра С zo ZQ знакового разряда частного С, а во второй микрокоманде формируется импульс И47 конца программыИз изложенного следует, что предлагаемое АУ позволяет пыполнить программу операции умножения за время t,,- 56t 14 МКС, (39) а программу операции деления за время 35 -t ЗЗД31 МКС .. Сравнивая выражения (22) (20) и (21) с выражениями (32), (39) и (40) получаем Чпрот It 128,1 м прот I-VM г(41) дел прот (-дел J Изтабл. 9 и 10 видно, что объем программируемой памяти блоков 1 и 2 для вьшолнения, программ операций умножения и деления составляет С 15-71 бит. Для выполнения программ операций умножения и деления в известном устройстве примерно требуется программировать объем памяти с -71 бит . (43) Сравнивая (42) и (43), получают Spor/C-2. что объем программируемой памяти в известном устройстве примерно в два раза больше, чем в предлагаемом. В связи с отмеченным фактом заключают, что программировать предлагаемое устройство примерно в два раза проще, чем известное. Технико-экономическая эффективность изобретения заключается в большем быстродействии и простоте программирования за счет уменьшения объема программируемой памяти.

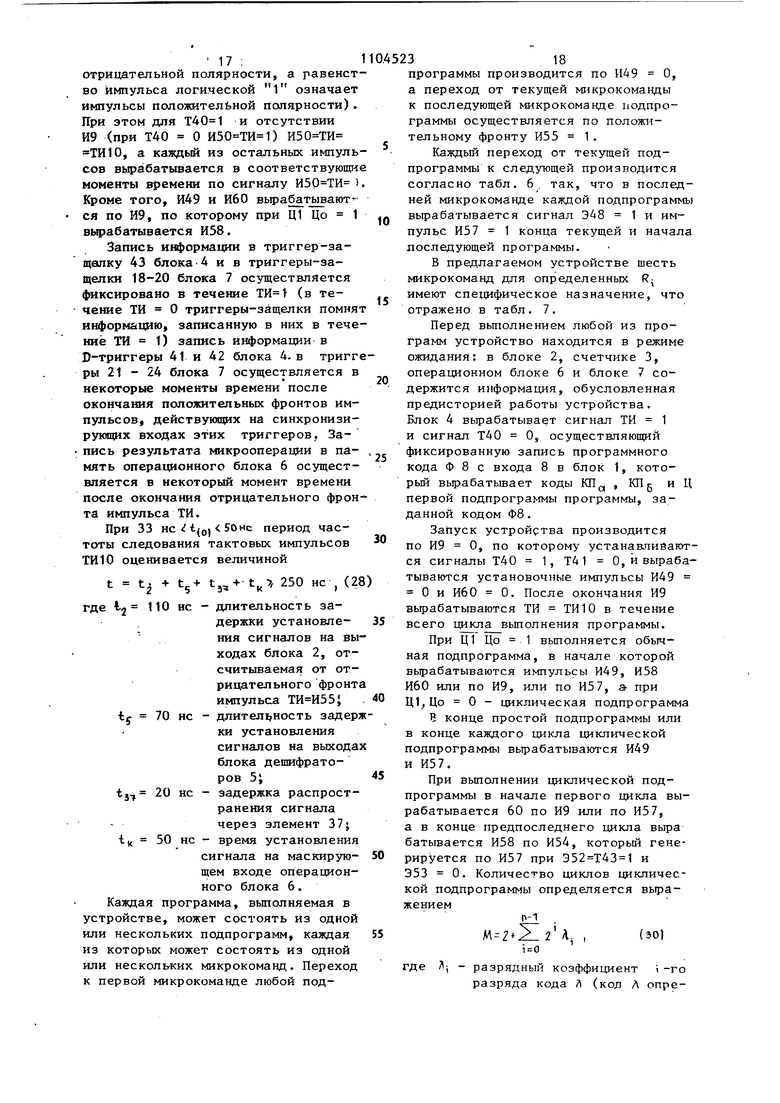

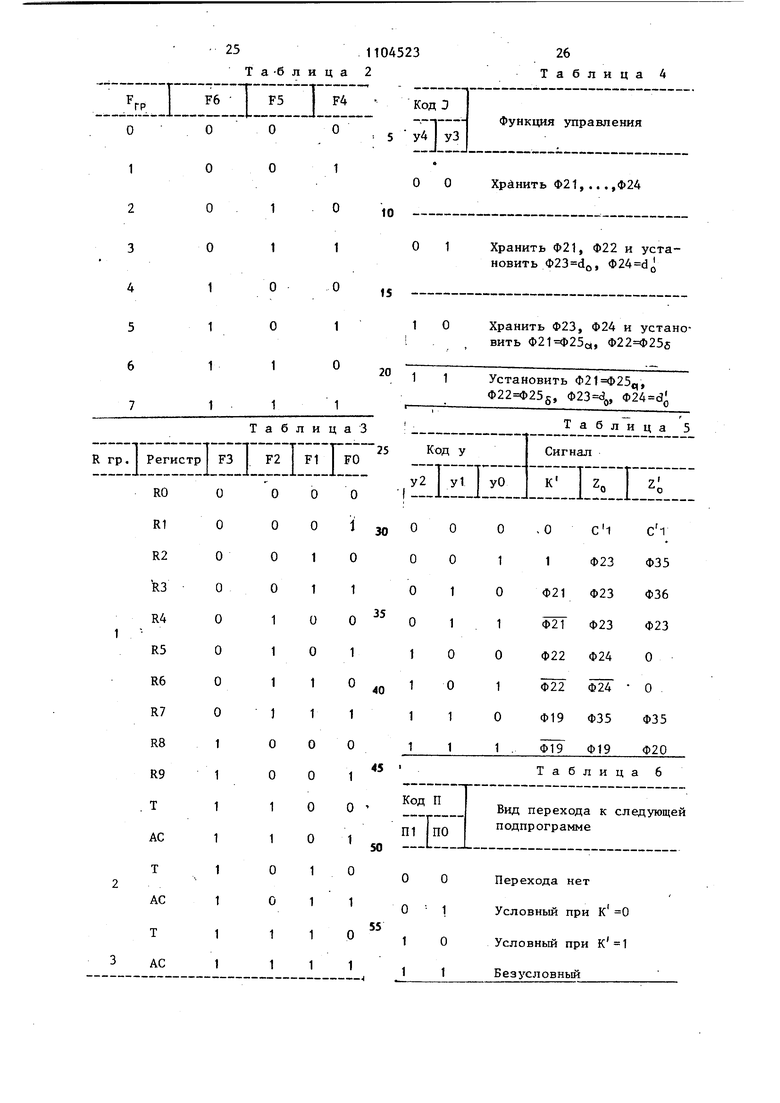

Таблица 1

251104523

Т а -б л и ц а 2

1 о 1 о 1 о

о

О О О

1

1

о

1

о

1

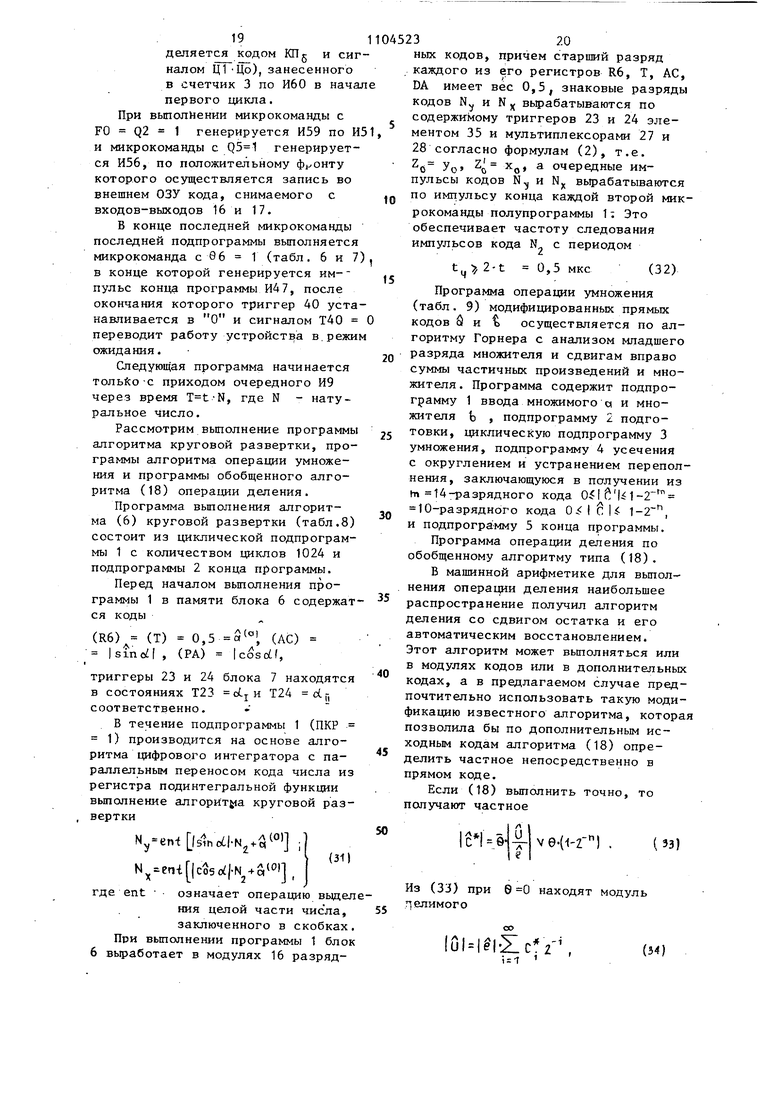

Таблица 3

26 Таблица 4

Хрйнить Ф21,...,Ф24

О О

Хранить Ф21, Ф22 и установить , ,

1о

Хранить Ф23, Ф24 и установить ,

Установить ,

1 1

ч

, , ,

Таблица 5

Таблица 6

Код П

Вид перехода к следующей подпрограмме П1 ПО

ООПерехода нет

0 1Условный при к 0

1ОУсловньш при

11Безусловный

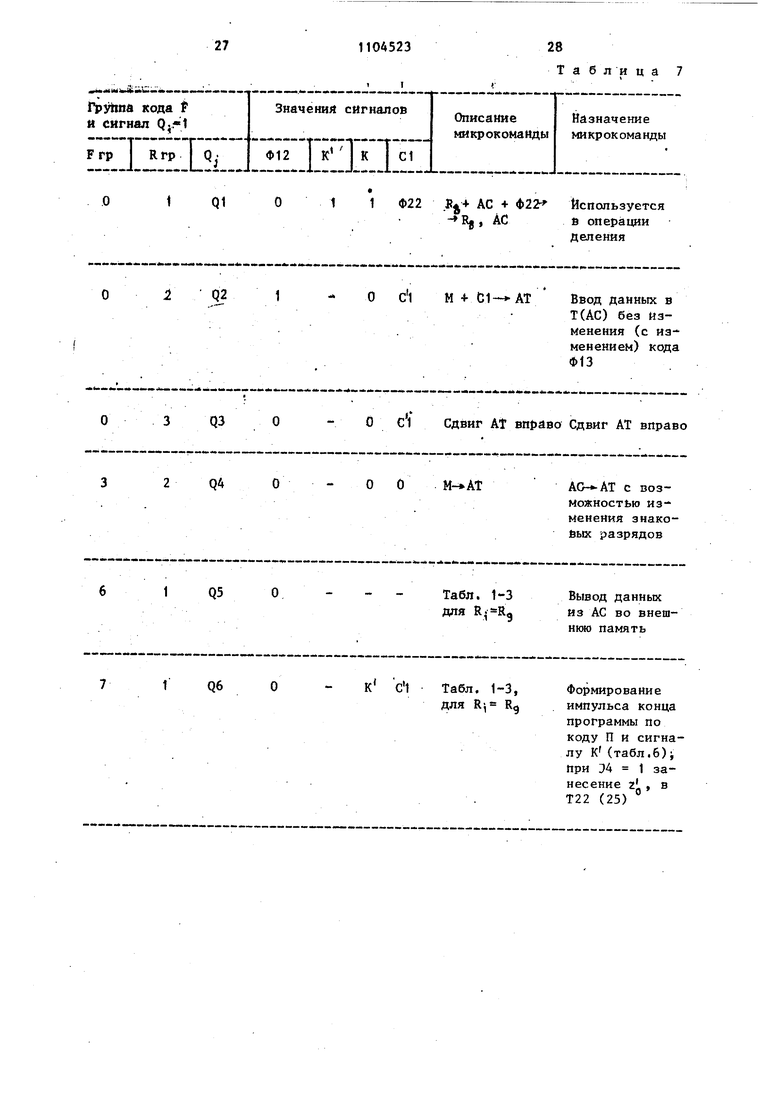

Q101 1 Ф22 3 AC + Ф22 Используется

Q2

Таблица 7

, АСfi операции

деления

М +

Ввод данных в Т(АС) без изменения (с изменением) кода Ф13

программы по коду П и сигналу к (табл.6); при 1 занесение 2 , в Т22 (25)

29

3 3

3

1

1104523

30

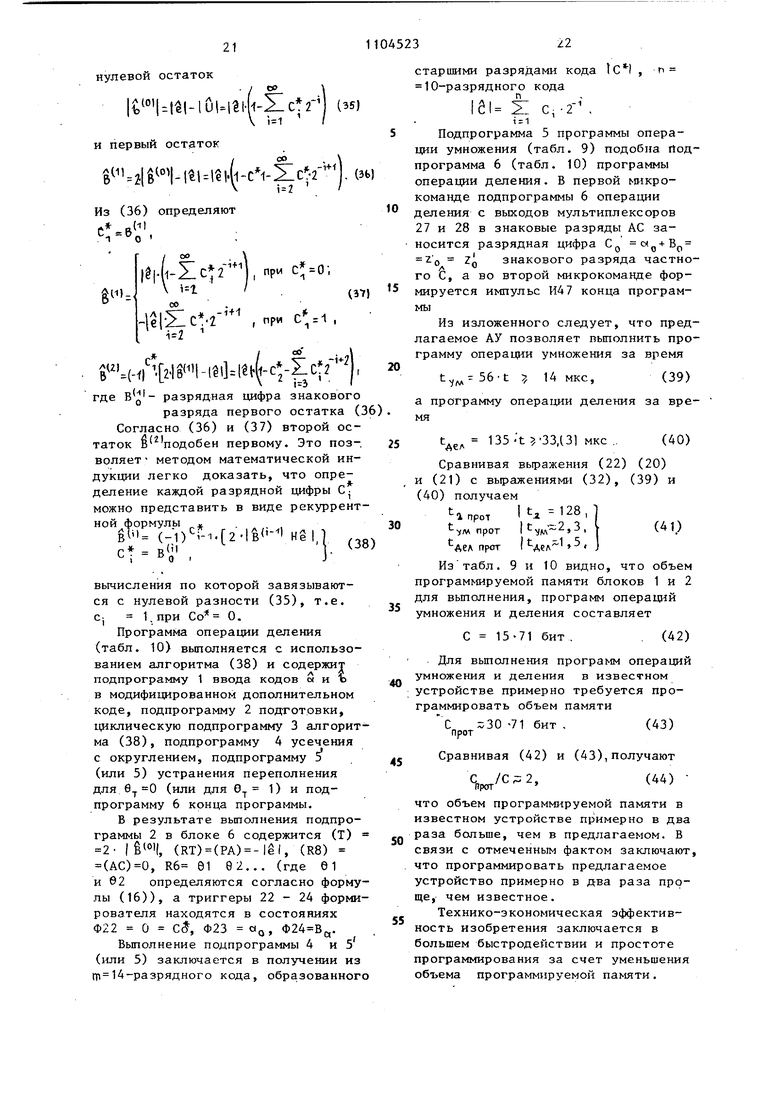

Таблица 8

0о

о о

1 о

11

1 1

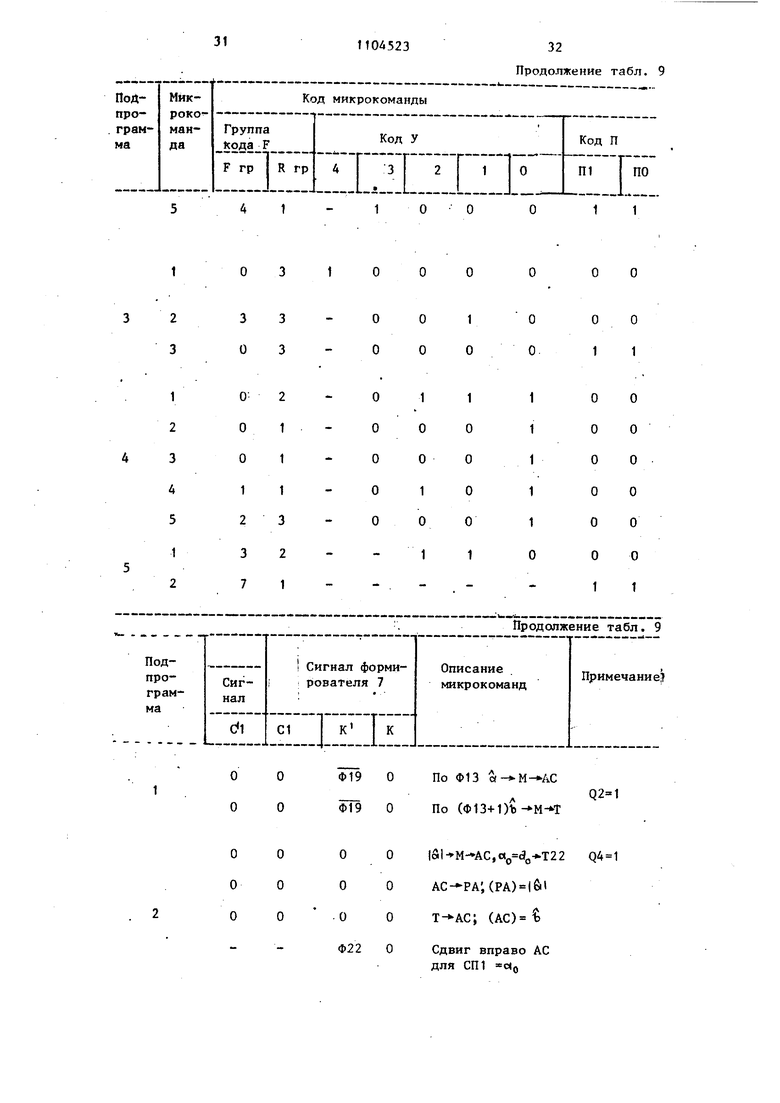

Таблица 9

31

О 3

1

3 3

2 3 О 3

2 1 1 1 3 2 1

О О О 1 2 3 7

1 2

3 4 5

1

2

Сигнал формирователя 7

Сигнал

di

C1

0Ф19 О

0ФТ9 О

О

О

О

Ф22

П04523

32 Продолжение табл. 9

о

о 1

о 1

о о

1 о

0.

1 1 1 1 1 о

о о о о о о 1

о о о о о о 1

1

1

о о о о 1

о о 1 о 1

Продолжение табл. 9

Описание

Примечание микрокоманд

По Ф13 с(

По (Ф13+1)

,

О О О

О О О О

(РА)|6 (Ас)

Сдвиг вправо АС для СП1

33

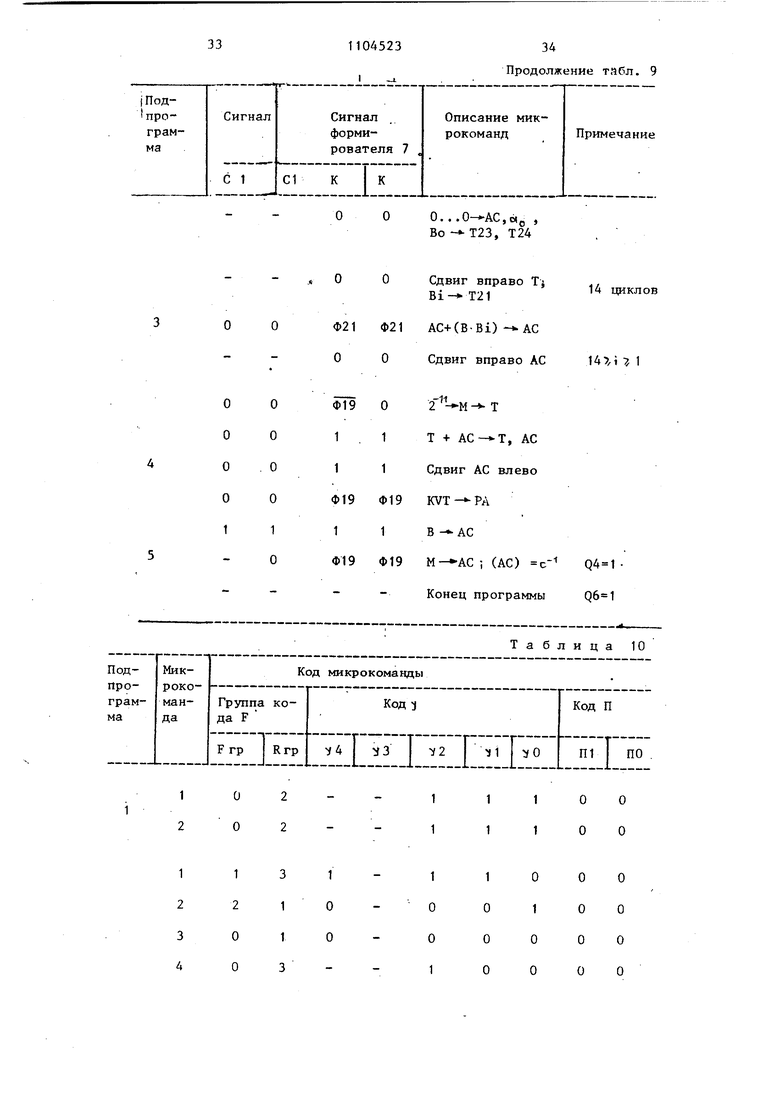

О

34

1104523 Продолжение тябл. 9

0...,«о , Во -«- Т23, Т24

Сдвиг вправо Tj

14 циклов Bi- Т21

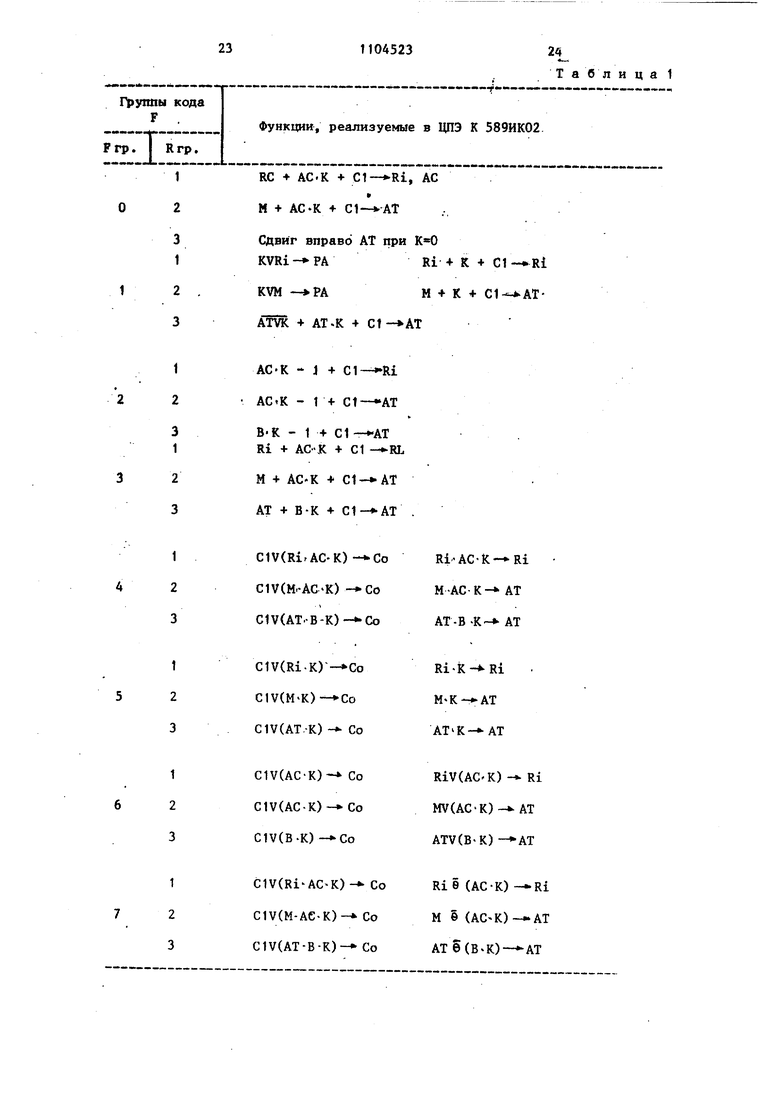

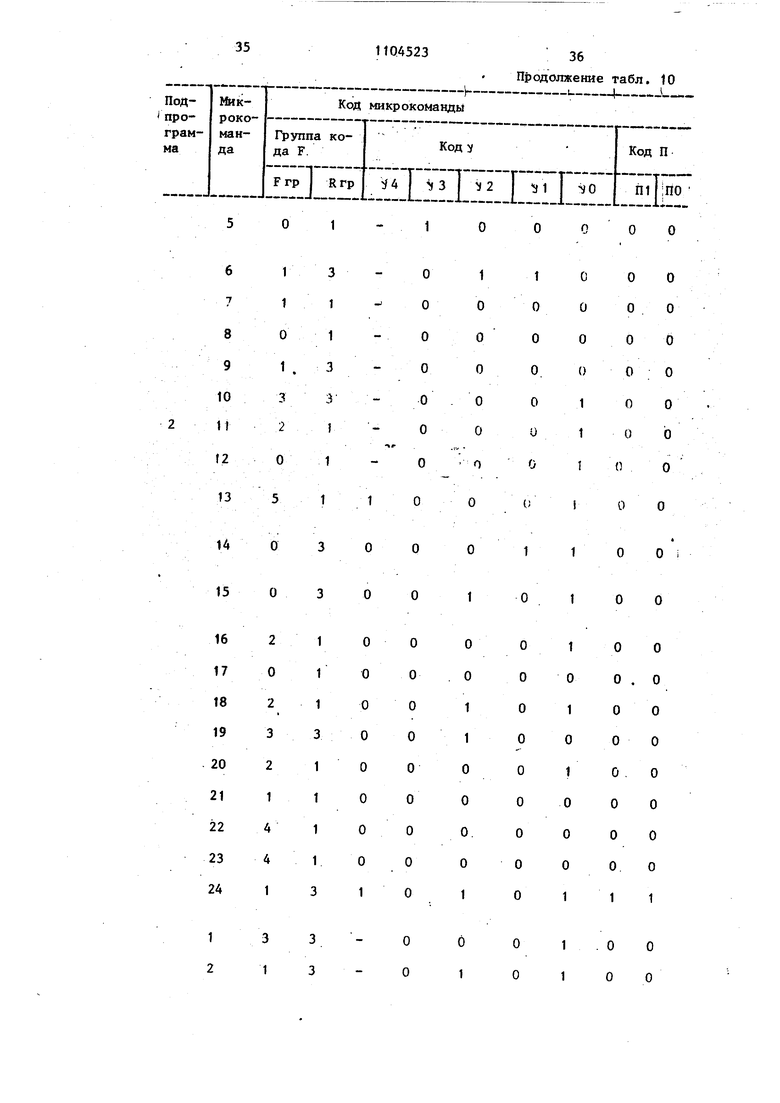

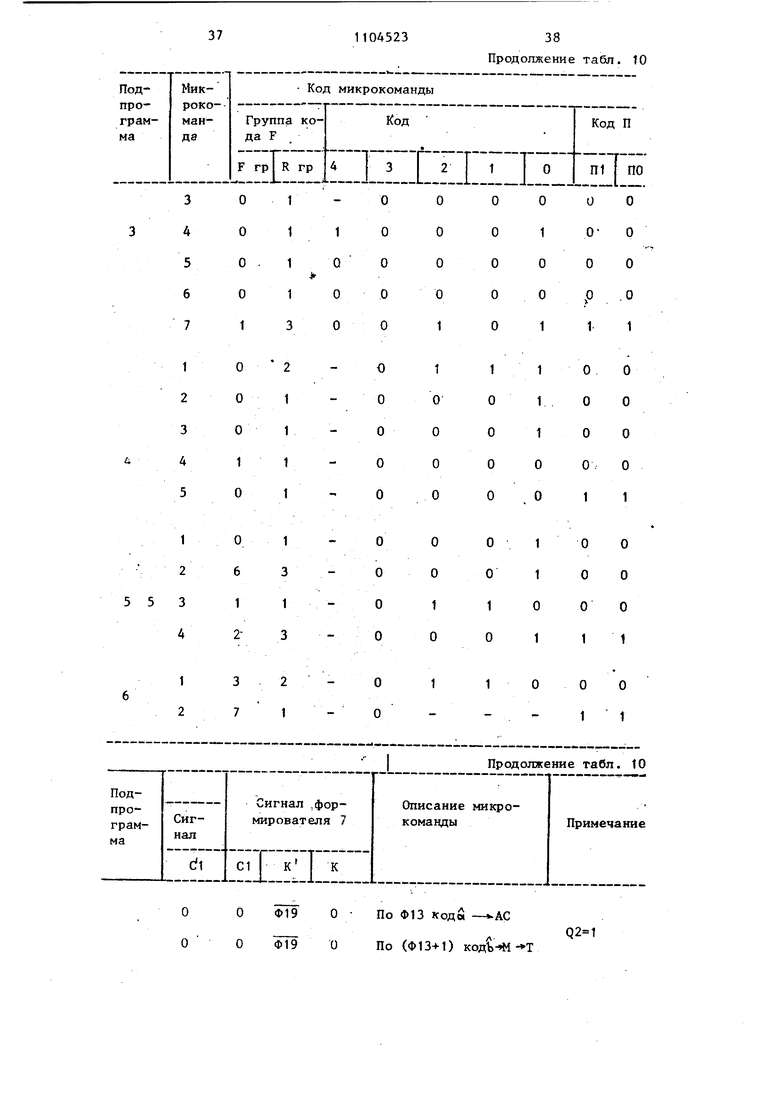

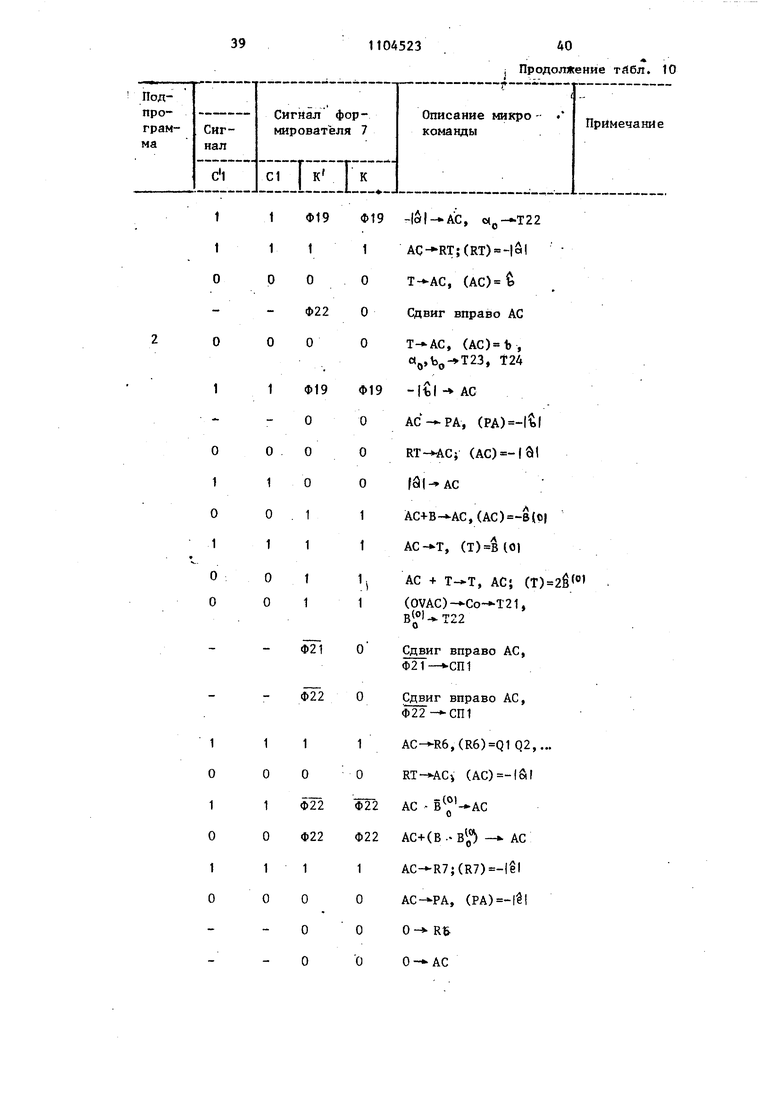

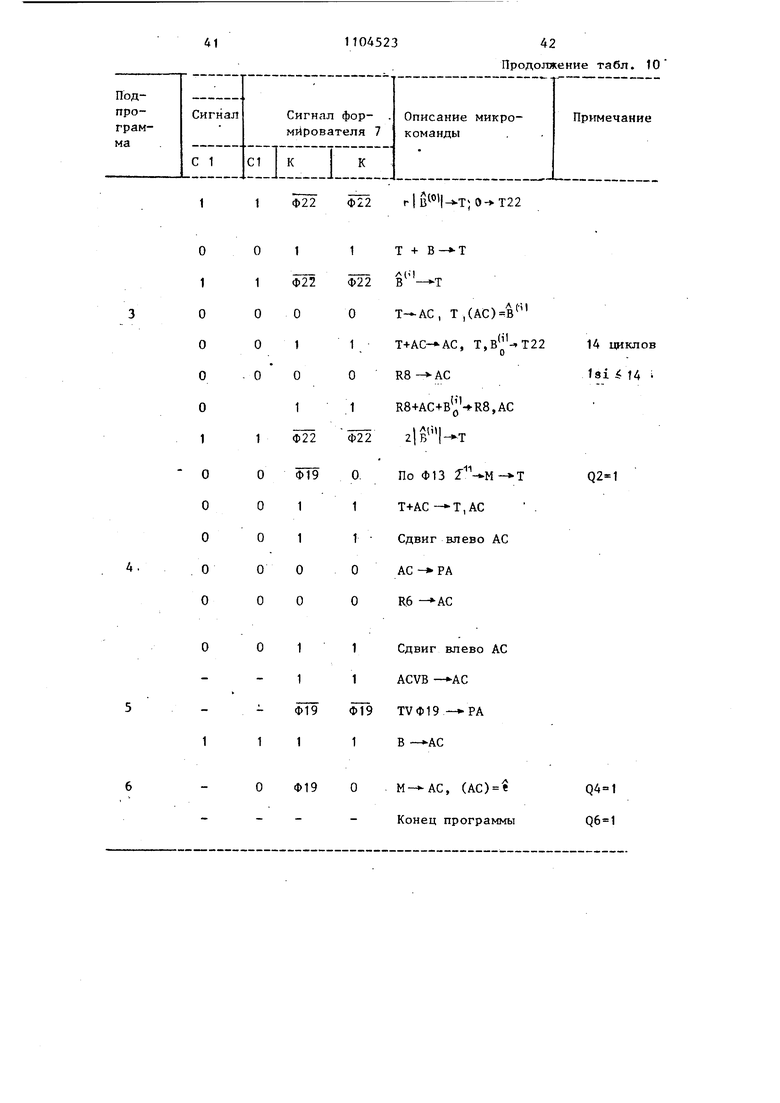

Таблица 10

35

11Q4523

36 Продолжение табл. 10

39

АО

1104523

Продолжение тйбл. 10

1 Ф22 Ф22

Ф19

г1в Ч- -Т;0- Т22

, (АС) е

Конец программы

СС {l|

К Па

А

140,

1J

3 а

ссз

ЦГи

(41 U.O

т

ее/

По То

-9 СС2

10

Iff аг/Л

-

:} //

к

HKP Ht-Цо

з

7Пу

По

в 6/1 с

tr

F

Со СПо

и

С1

;

К

fl/

k}

.{

а

М

/г

МСПц 5П

П

Zt,

4

/7

W 7Г S3

4

Щ

JL /Vx

и

/.

С/

QI

W W ТПГ

о

.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1975 |

|

SU547765A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| Микропроцессорные комплекты повышенного быстродействия | |||

| М., Радио и связь, 1981, с | |||

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1984-07-23—Публикация

1982-09-22—Подача