,

Изобретение относится к автоматй кеси вычислительной технике и может быть использовано при создании спе- j циализированных аналоговых и комбинированных вычислительных устройств.

Аналоговое запоминающее устройство (АЗУ ) предназначено для запоминания и хранения определенное время мгновенных значений входного запоминаемого напряжения. Запоминаемое напряжение подают через ключ к накопительному конденсатору, который заряжается до мгновенного значения этого напряжения. При размыкании ключа накопительный конденсатор запоминает .значение напряжения, которое было на нем в момент размыкания ключа.

Известно АЗУ, обеспечивающее запоминание и хранение мгновенных зна чений напряжения 1 ,

Недостатком этих устройств является невысокая точность запоминания при коммутации импульсными сигналаМИ малой длительности с большой скважностью, обусловленная следующими причинами.

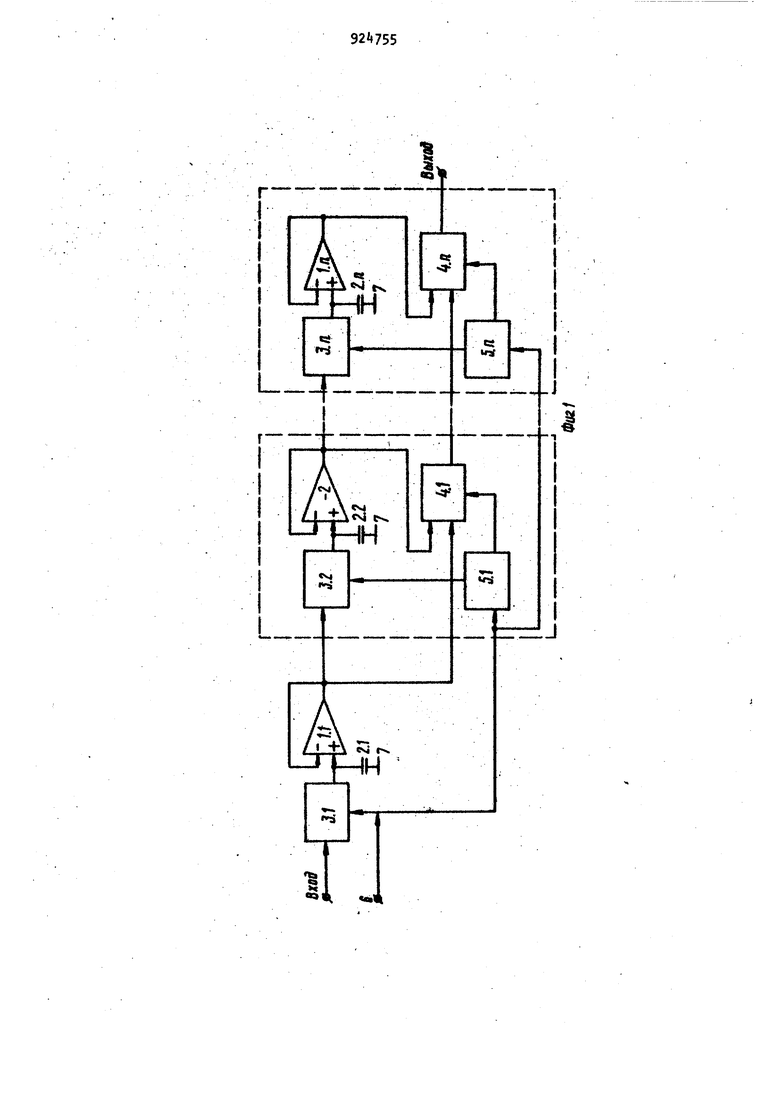

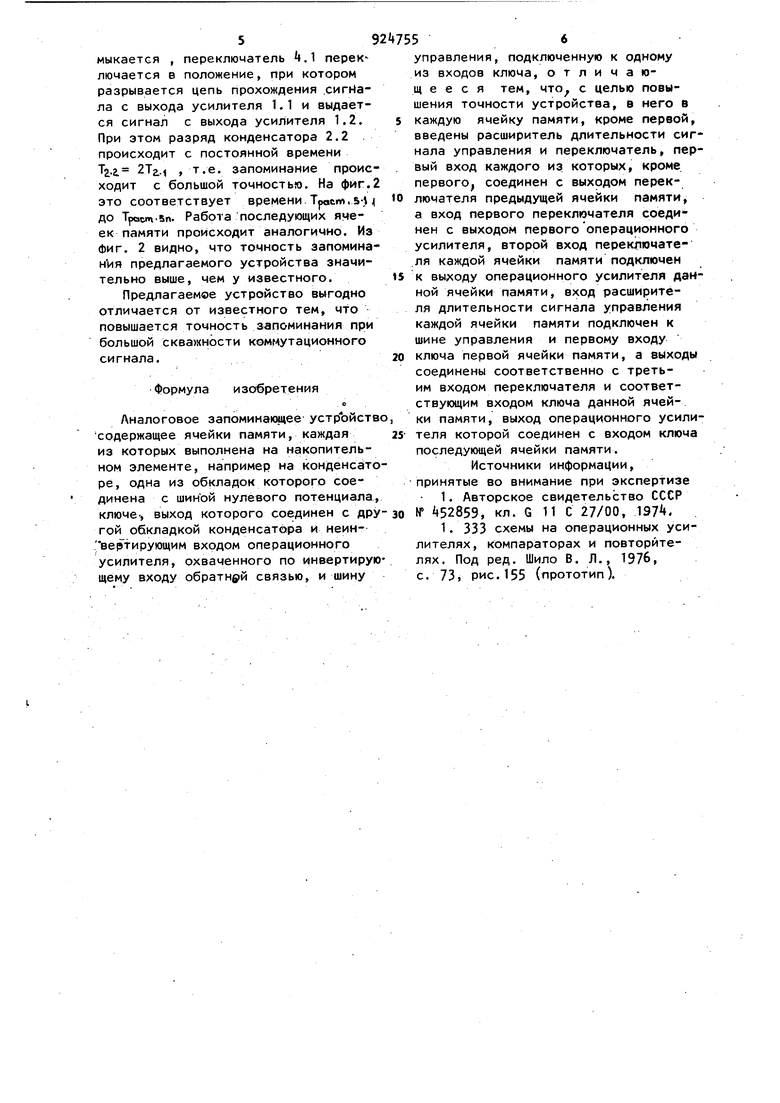

Для получения высокой точности запоминания необходимо выбирать большую постоянную времени разряда Траьб. накопительного элемента. Для этого приходится выбирать кроме определенной величины сопротивления разряда и большое значение емкости накопительного конденсатора , Это приводит к увеличению постоянной времени заряда емкости Т.ар при замкнутом ключе, которая примерно равна ЗР к тому, что за время открытого состояния ключа, определяемого временем действия коммутационного импульса, емкость не успевает зарядиться до амплитудного значения входного сигнала. Это вызывает ошибку в запоминании. Уменьшение запоминающей емкости для возможности заряда до амплитудного значения) приводит к уменьшению Трвър. и увеличению ошибки, за счет разряда емкости при разомкнутом ключе..Поэтому обеспечить высокую точность при небольших длительностях импульса коммутационного сигнала и при его большой скважности, не удается. Наиболее близкой к предлагаемой является схема выборки-хранения сигналов. Устройство содержит накопительный конденсатор-, одна обкладка которого соединена с общей шиной, а другая - с неинвертирующим входом операционного усилителя (ОУ),выход которого соединен с инвертирующи входом ОУ и выходом устройства,; и- че рез ключ, управляемый сигналом выбор ки, со входом устройства 2. Недостатком устройства является невысокая точность запоминания при коммутации импульсными сигналами малой длительности и большой скважности накопительного конденсатора (при размыкании ключа);, либо ошибкой за счет того, что конденсатор за время действия коммутирующего импульса при замкнутом ключе не успе вает зарядиться до амплитудного значения входного сигнала. Цель изобретения - повышение точности устройства. Поставленная цель достигается тем, что в аналоговом запоминающем устройстве, содержащем ячейки памяти, каждая из которых выполнена на накопительном элементе, например на конденсаторе, одна из обкладок которого соединена с шиной нул вого потенциала, ключе, выход которо го соединен с обкладкой конденсатора и неинвертирующим входом операционного усилителя, охваченного по инвертирующему входу обратной связью, и шину управления , подключенную к одному из входов ключа, в каждую ячейку памяти, кроме первой, введены расширитель длительности сигнала управления и переключатель,первый вход каждого из которых, кроме первого, соединен с выходом переключателя предыдущей ячейки памяти, а вход первого переключателя соеди нен с выходом первого операционного усилителя, второй вход переключателя каждой ячейки памяти подключен к выходу операционного усилителя данной ячейки памяти, вход расширителя длительности сигнала управления каждой ячейки памяти подключен к шине управления и первому входу кл ча первой ячейки памяти, а выходы соединены соответственно с третьим входом переключателя и соответствующим входом ключа данной ячейки памяти, выход операционного усилителя которой соединен с входом ключа последующей ячейки памяти. На фиг. 1 представлена функциональная схема устройства; на фиг. 2эпюры сигналов, поясняющие принцип работы предлагаемого устройства. Устройство (фиг. 1 ) содержит операционные усилители 1.1-1.П, накопительные элементы, например конденсаторы 2.1-2.П, ключи 3.1-З.п, переключатели 4.1-.п, расширители длительности сигнала управления 5.15.П , шина 6 управления, шина 7 нулевого потенциала и ячейки 8.V8.n памяти. Устройство работает следующим образом. При наличии сигнала управления срабатывает ключ 31, расширители длительности сигнала управления 5-1 5.iT одновременно с поступлением сигнала управления выдают напряжение, открывающее ключи 3.2-З.п и переключатели 4.1-4.П переходят в положение, при котором напряжение с выхода усилителя 1.1 проходит через переключатели 4.1-.п на выход устройства, а сигналы с усилителей 1.2-1.П на выход не проходят, т.е. на выход проходит только сигнал, соответствующий сигналу на конденсаторе 2,1. Накопительные конденсаторы 2.2-2.П начинают также заряжаться напряжением с выходов усилителей 1.2-1.п. Постоянная времени заряда и разряда (за счет увеличения номинального значения емкости ) каждой последующей ячейки памяти увеличивается в соответствии с увеличением длительности коммутационного сигна- . ла на выходе соответствующего расширителя. После окончания командного импульса сигнал с выхода усилителя 1 выдается на выход устройства, и одновременно в течение времени Траст.vi напряжение на конденсаторе 2.2 следит за напряк ением на выходе усилителя 1.1 практически без ошибки,т.е. .i так как .. г-г- После окончания действия сигнала с выхода расширителя 5.1 ключ 3.2 размыкается , переключатель ,1 перек яючается в положение, при котором разрывается цепь прохождения .сигНала с выхода усилителя 1.1 и выдается сигнал с выхода усилителя 1.2. При этом разряд конденсатора 2.2 происходит с постоянной времени Т2.г. 2J2.- , т.е. запоминание происходит с большой точностью. На фиг.2 это соответствует времени Трест.s-i до ТроыпВп. Работа последующих ячеек памяти происходит аналогично. Из фиг. 2 видно, что точность запоминания предлагаемого устройства значительно выше, чем у известного.

Предлагаемое устройство выгодно отличается от известного тем, что повышается точность запоминания при большой скважности коммутационного сигнала.

Формула изобретения

. о

Аналоговое запоминакидее устрЪйство содержащее ячейки памяти, каждая из которых выполнена на накопительном элементе, например на конденса1торе, одна из обкладок которого соединена с шиной нулевого потенциала, ключе-, выход которого соединен с другой обкладкой конденсатора и неинвертирующим входом операционного усилителя, охваченного по инвертирующему входу обратной связью, и шину

управления, подключенную к одному из входов ключа, отличающееся тем, что, с целью повышения точности устройства, в него в каждую ячейку памяти, кроме первой, введены расширитель длительности сигнала управления и переключатель, первый вход каждого из которых, кроме первого, соединен с выходом переключателя предыдущей ячейки памяти, а вход первого переключателя соединен с выходом первого операционного усилителя, второй вход переключателя каждой ячейки памяти подключен к выходу операционного усилителя данной ячейки памяти, вход расширителя длительности сигнала управления каждой ячейки памяти подключен к шине управления и первому входу ключа первой ячейки памяти, а выходы соединены соответственно с третьим входом переключателя и соответствующим входом ключа данной ячейки памяти, выход операционного усилителя которой соединен с входом ключа последующей ячейки памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № -452859, кл. G 11 С 27/00, 197.

1. 333 схемы на операционных усилителях, компараторах и повторителях. Под ред. Шило В. Л., 1976, с. 73, рис.155 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устрой-CTBO | 1979 |

|

SU803013A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU729642A1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

| АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2006970C1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU991513A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830583A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU957275A1 |

| Интегратор с запоминанием | 1978 |

|

SU698009A1 |

| Ячейка аналоговой памяти | 1978 |

|

SU729643A1 |

Авторы

Даты

1982-04-30—Публикация

1979-06-27—Подача