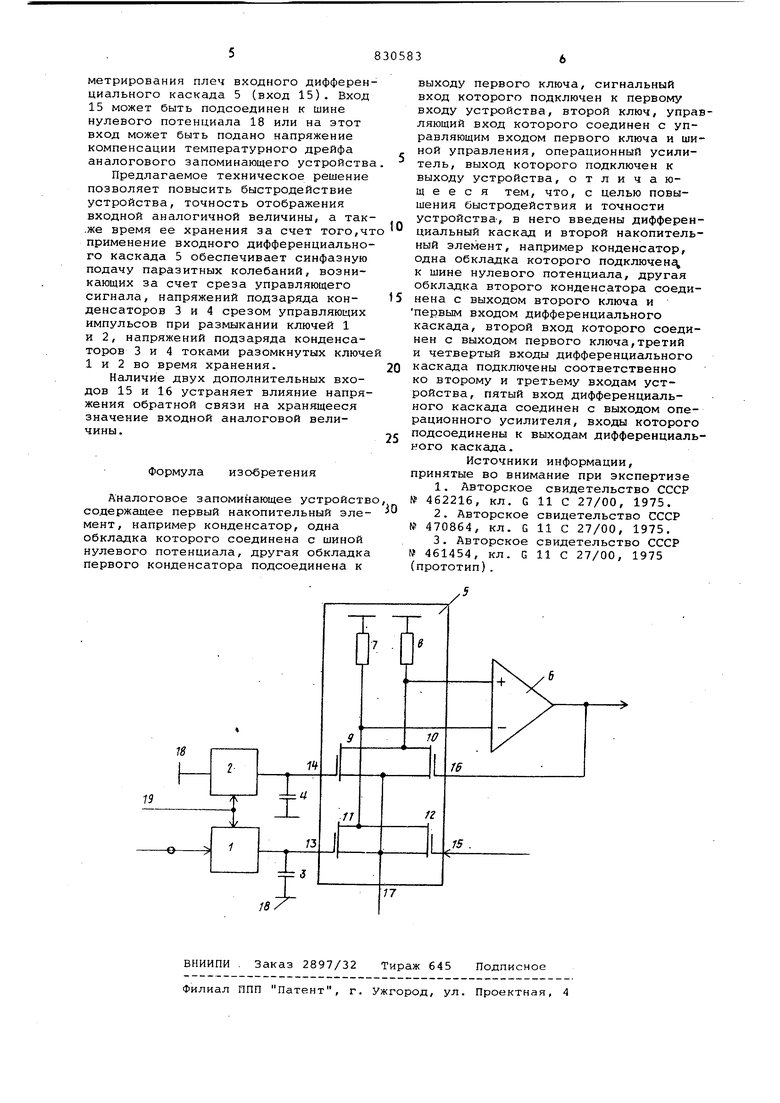

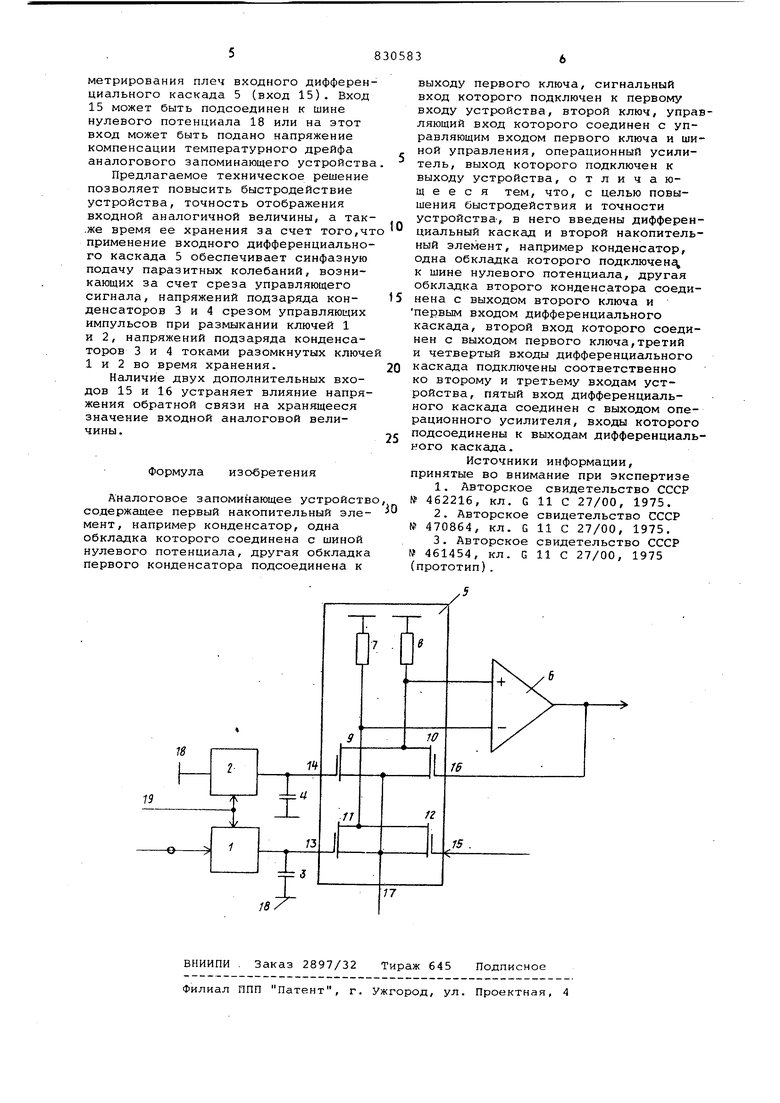

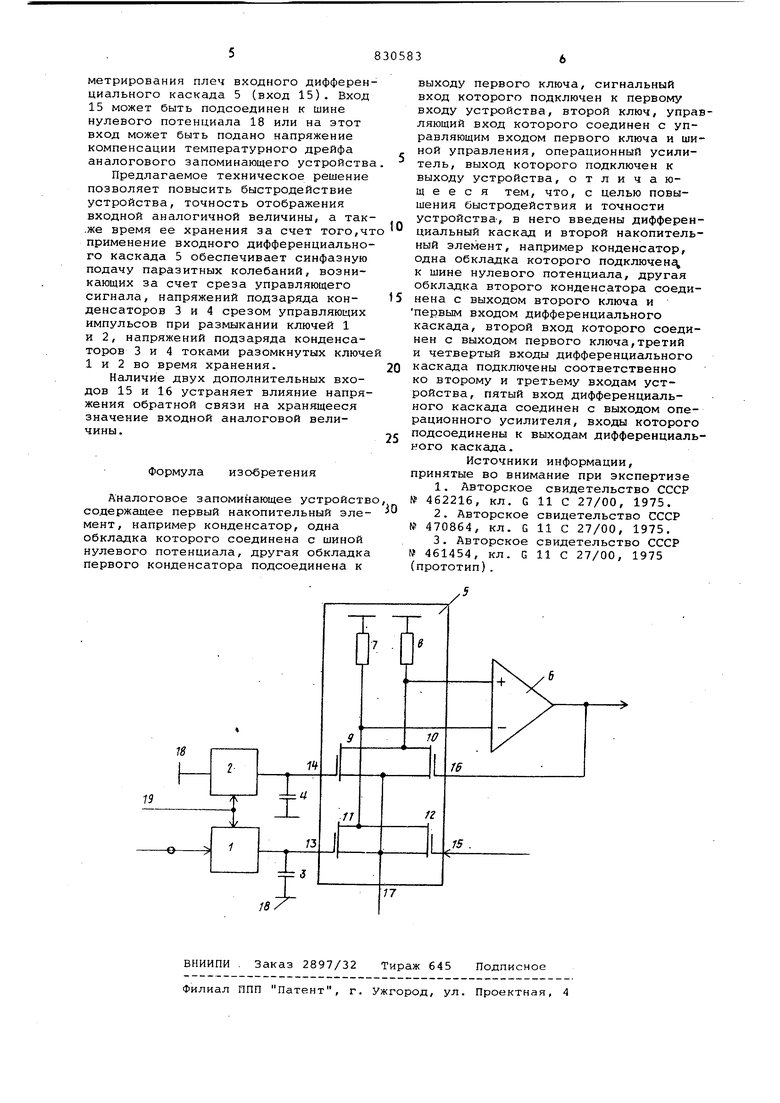

Изобретение относится к аналогоцифровой измерительной технике и может быть использовано в контрольн измерительных системах различного назначения. Известна ячейка аналоговой памят содержащая два ключа на МОП-транзис торах, запоминающий конденсатор и и вертор управляющих мпульсов, при этом шина управления соединена с затвором первого МОП-транзистора и через инвертор с затвором второго (дополнительного) МОП-транзистора, кроме того, исток первого МОП-транзистора подключен к источнику входного напряжения, а его сток соединен со стоком второго МОП-транзистора и подключен к ко-нденсатору 1 . Недостаток такого решения в том, что компенсация переходных процессов возникающих при воздействии управляю щего сигнала, происходит со сдвигом вносимым инвертором. Это приводит к необходимости увеличения длительности управляемого импульса и не исключает подзаряд запоминающего конденсатора фронтом управляющего импульса, что снижает быстродействие и точность. Известно также аналоговое запоминающее устройство, содержащее усилитель, ключ, первый элемент памяти, а также дополнительные усилитель,ключ и элемент памяти, при этом на первые входы усилителей подается входной сигнал, а выходы усилителей через ключи соединены со вторыми входами этих усилителей и подключены к элементу памяти и дополнительному элементу памяти соответственно,JcpoMe того, элементы памяти включены последовательно, а управляющий сигнал подается на управляющие входы ключей 2. Недостаток такого устройства в том, что после снятия управляющего воздействия размыкается цепь обратной связи и усилители входят в насыщение, что снижает быстродействие и точность устройства. Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство, которое содержит входной и выходной операционные (дифференциальные) усилители, запоминающую емкость (конденсатор), ключ и два дополнительных ключа, при этом выход входного дифференциального усилителя через второй дополнительный ключ и ключ соединен с конденсаторог/i и неиивертирующим входом выходного усилителя, выход которого является выходом устройства, а также соединен с инвертирующим входом этого усилителя и через первый дополнительный ключ с входом ключа ГЗ}. Однако данное устройство характеризуется следующими недостатками. В режиме размыкается цепь обратной связи входного усилителя, что приводит его в режим насыщения Поэтому при переходе в режим выборк резко увеличивается время установления выходного напряжения, что при водит к снижению быстродействия уст ройства. Компенсация переходных про цессов, которые возникают под воздействием на ключи управляющих сигналов, происходит на запоминающем конденсаторе со сдвигом во времени, равном суммарной вьщержке входного усилителя и второго дополнительного ключа, что приводит к снижению точности запоминания. Запоминающий конденсатор соединен с.двумя входам двух усилителей, -что примерно в два раза увеличивает скорость разряда конденсатора через паразитные емкос ти усилителей. Это приводит к сниже нию времени хранения аналоговой вел чины, а значит, и точности хранения Цель изобретения - повышение точ ности и быстродействия устройства. Поставленная цель достигается те что в аналоговое запоминающее устро ство, содержащее первый накопительный элемент, например конденсатор, одна обкладка которого соединена с шиной нулевого потенциала, другая обкладка первого конденсатора подсоединена к выходу первого ключа,си нальный вход которого подключен к первому входу устройства, второй ключ, управляющий вход которого сое динен с управляющим входом первого ключа и шиной управления,операционный усилитель, выход которого подключен к выходу устройства,введены дифференциальный каскад и второй накопительный элемент, например кон денсатор, одна обкладка которого по ключена к шине нулевого потенциала, другая обкладка второго конденсатор . соединена с выходом второго ключа первым входом дифференциального кас када, второй вход которого соединен выходом первого ключа, третий и чет вертый входы дифференциального каскада подключены соответственно ко второму и третьему входам устройств пятый вход дифференциального каскад соединен с выходом операционного усилителя, входы которого подсоединены к выходам дифференциального ка када. На чертеже представлена функцио нальная схема- предлагаемого ycTpoti ства. Устройство содержит ключи 1 и 2, акопительные элементы, например онденсаторы 3 и 4, дифференциальый каскад 5, операционный усилитель , причем дифференциальный каскад выполнен на резисторах 7 и 8 и ОП-транзисторах , дифференциальый каскад 5 имеет входы 13-17.Устойство содержит также шину 18 нулеого потенциала и шину 19 управления. Устройство работает следующим обазом. На вход первого ключа 1 подается аналоговый сигнал. При подаче на управляющие входы ключей 1 и 2 управляющего импульса они замыкаются.Конденсатор 3 заряжается до напряжения, равного входному аналоговому сигналу. Второй конденсатор 4 через замкнутый ключ 2 соединен с шиной 18 нулевого потенциала. По окончании управляющего импульса ключи 1 и 2 размыкаются. В момент размыкания ключей 1 и 2 за счет среза управляющего импульса на конденсаторах 3 и 4 возникает переколебательный процесс, обусловленный наличием паразитной емкости между управляющим входом и выходом ключей 1 и 2. За счет энергии переколебательного процесса происходит подзаряд конденсаторов 3 и 4. Напряжения на конденсаторах 3 и 4 равны соответственно S Ugy s i ncDt + Д и , U4 . s i ncot + Д и , и - мгновенное значение аналогового сигнала в момент размыкания ключа 1;, sinuyi - напряжение переколебательногопроцесса ; ди - напряжение подзаряда конденсаторов 3 и 4. Напряжение с конденсаторов 3 и 4 подается на входы 13 и 14 входного дифференциального каскада 5. Входной дифференциальный каскад 5 и операционный усилитель б образуют составной дифференциальный Усилитель. Так как напряжение с конденсаторов 3 и 4 подается на входы 13 и 14, то выходное напряжения усилителя 6 пропорционально разности входных tiaпряжений:ы. ) ки где К - коэффициент усиления составного дифференциального усилителя . Вторая пара входов 15 и 16 входного дифференциального каскада необходима для подачи напряжения обратной связи (вход 16), определяющего коэффициент усиления К,и для симметрирования плеч входного дифферен циального каскада 5 (вход 15). Вход 15 может быть подсоединен к шине нулевого потенциала 18 или на этот вход может быть подано напряжение компенсации температурного дрейфа аналогового запоминающего устройств Предлагаемое техническое решение позволяет повысить быстродействие устройства, точность отображения входной аналогичной величины, а так .же время ее хранения за счет того,ч применение входного дифференциально го каскада 5 обеспечивает синфазную подачу паразитных колебаний, возникающих за счет среза управляющего сигнала, напряжений подзаряда конденсаторов 3 и 4 срезом управляющих импульсов при размыкании ключей 1 и 2, напряжений подзаряда конденсаторов 3 и 4 токами разомкнутых ключе 1 и 2 во время хранения. Наличие двух дополнительных входов 15 и 16 устраняет влияние напряжения обратной связи на хранящееся значение входной аналоговой величины. Формула изобретения Аналоговое запоминающее устройств содержащее первый накопительный элемент, например конденсатор, одна обкладка которого соединена с шиной нулевого потенциала, другая обкладка первого конденсатора подсоединена к выходу первого ключа, сигнальный вход которого подключен к первому входу устройства, второй ключ, управляющий вход которого соединен с управляющим входом первого ключа и шиной управления, операционный усилитель, выход которого подключен к выходу устройства, отличающееся тем, что, с целью повышения быстродействия и точности устройства, в него введены дифференциальный каскад и второй накопительный элемент, например конденсатор, одна обкладка которого подключен к шине нулевого потенциала, другая обкладка второго конденсатора соединена с выходом второго ключа и первым входом дифференциального каскада, второй вход которого соединен с выходом первого ключа,третий и четвертый входы дифференциального каскада подключены соответственно ко второму и третьему входам устройства, пятый вход дифференциального каскада соединен с выходом операционного усилителя, входы которого подсоединены к выходам дифференциального каскада. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 462216, кл. G 11 С 27/00, 1975. 2.Авторское свидетельство СССР № 470864, кл. G 11 С 27/00, 1975. 3.Авторское свидетельство СССР № 461454, кл. G 11 С 27/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881869A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1164788A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU733032A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Аналоговое запоминающее устройство | 1974 |

|

SU510752A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU951404A1 |

11

Т

73

Т

10

w

fZ

Авторы

Даты

1981-05-15—Публикация

1979-07-23—Подача