(54) УСТРОЙСТВО ДЛЯ ВВОДА ДВОИЧНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для контроля ответов учащихся | 1984 |

|

SU1182565A2 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ИНФОРМАЦИИ ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 1994 |

|

RU2083411C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

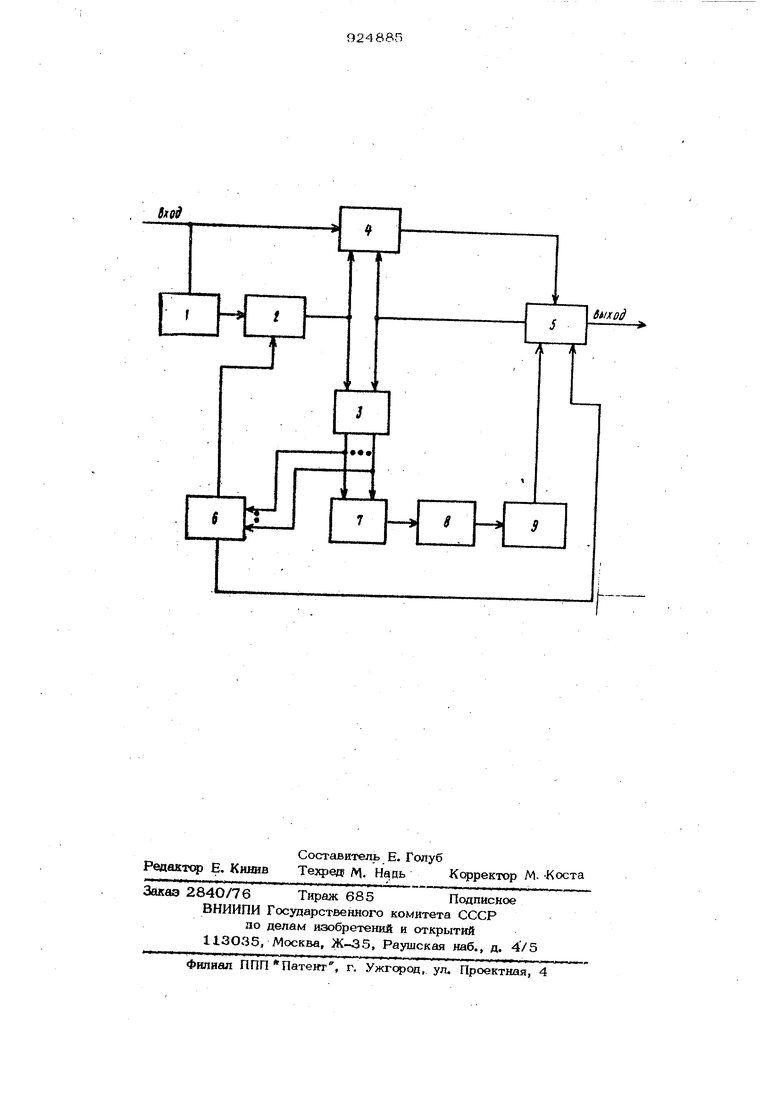

Изобретение относится к технике .пере дачи двоичной информации и может использоваться при сопряжении устройств обработки информации с каналами связи. Известно устройегво для ввода двоичной информации, содержащее анализатор отсутствия сигналов, блок формирования тактовых частот и регенерации, блок памяти, распределители записи и считывания, блок сравнения, дополнительный блок сравнения и анализатор фазового сдвига tl. Недостатком известного устройства является его. ненадежность и неспособность выдавать непрерывную информацию 1ри входной информации в виде отдельных посылок, что вызвано наличием аси хронных сбоев прк фаз1фовании момеиго записи и считывания. Кроме того, такая задача потребовала бы в известном устройстве применения большого объема пам ти. Наиболее близким техническим решением явпяется устройство для ввода дво ной информации, содержащее формирователь тактовой частоты, выход которого подключен к первому входу распределителя записи, выход которого соединен с первыми входами блока памяти и реверсивного счетчика., второй вход которого соединен с вторым входом блока памятии с выходом распределителя считыйания, Однако это устройство имеет низкук:) достоверность. Цель изобретения - повьвзиение достоверности. Для достижения указанной цели в устройство для ввода двоичной информации, содержащее фсрмирова ель тактовой частоты, выход которого подключен к первому входу распределителя записи, выход которого соединен с первыми входами памяти и реверсивного счетчика, втсрой вход которого соединен с вторым входом блока памяти и с выходом расгфеделителя считывания, введены формирователь управляющего сигнала, сук1магор, порогойый блок и управляемый генератор, вьц котороаго подключен к первому входу распределителя считывания, второй вход которого соединен с первым выходом ф мирователя у1фавляющего сигнала, вход KOTOjjoro соединены с выходами реверси ного счетчшса и с входами сумматора, выход которого через пороговый блок подютючен к входу управляемого генера тора, причем второй выход формировате ля управляющего сигнала соединен с вт рым входом распределителя записи, а вход формирователя тактовой частоты с динен с третьим входом блока памяти, выход которого подключен к третьему в ду распределителя считывания., На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство для ввода двоичной информации содержит формирователь 1 так товой частоты, распределитель 2 записи, реверсивный счетчик 3, блок 4 памяти, распределитель 5 считывания, форм1фователь 6 управлйющего сигнала, .сумматор 7, пороговый блок 8,управляемый генератор 9. Устройство работает следующим обра зом. На вход поступают отдельные информацисзнные бинарные посылки, состоящие из (где Д «N ) символов следующих с тактовой частот да F , причем возможны случаи, когда каждая i -я или (i +1 )-я посылка отсутствует, нащзимер, каждая 7-я или 8-я посылка. При этом закон чередования отсутствую щей посылки носит случайный характер. С выхода устройства снимается непрерывная информация с тактовой частотой считывания F (..„ « F, при этом за последним символом предыдущей посьшки сразу следует первый символ последующей посылки, задержка или нахлест символов недопустим Период следования входных посьшок Т N | Р а частоты F и F не кратны, поэтому за время Т число записанных и сосчитан ных символов неодинаково, и в блоке памяти 4 за каждый период Т будет возникать избыток или недостаток информации. Блок 4 состоит из отдельных Ti регистров оперативной памяти (не показанных), каждому из которых соответствует свой счетчик в реверсивном счет . нике 3. Перед началом работы содержиМое счетчиков равно нулю, при этом формирователь 6 через расщ еделитель 2 записи будет последовательно разрещать запись информации в первые п /2 регистров, а подачу тактовых импульсов с частотой FT - на счетные входы сложения первых п/2 счетчиков. Т.е. первая, пришедшая по каналу связи информационная посылка, запишется в первый регистр блока 4, прк этом число символов в посылке будет храниться в первом счетчике, вторая посылка запишется во второй регистр, а число символов во второй посылке - во второй счетчик и т.д. пока не заполняется п/2 регистров и соответственно, счетчиков. После этого формирователь 6 через распределитель считыв ания 5 подключает первый регистр к выходу устройства, а выход управляемого генератора 9, вырабатывающего тактоЖю импульсы считывания с частотой F ц - к входу первого блока 4 и счетному входу вычитания первого счетчика реверсивного счетчика 3. После считывания на выход последнего символа первой посьшки с первого регистра первый счетчик обнуляется и формирователь 6 подключает к выходу второй регистр, а импульсы считывания поступают на второй регистр и второй счетчик и т.д. Процесс считывания и выдачи информации идет непрерывно. При этом одновременно происходит запись приходящих информационных посылок в соответствующие свободные регистры блока 4 памяти. Процессом записи и считывания управляет формирователь 6, на вход которого поступают данные о состоянии каждого из счетчиков реверсивного счетчика 3. Считывание информации происходит строго в той же последовательности, что н запись. В процессе работы содержимое блока амяти будет изменяться: или колебатья около некоторого среднего значения, или с течением времени расти, или уме 1ьаться. Это содержимое постоянно оцеивается сумматором 7, который складыает содержимое всех счетчиков реверсивого счетчика 3 и вырабатывает код , оторый через пороговый блок 8 управяет частотой Fc.4 угфавляемого генераора 9. Если ZL не выходит за пределы выбранных порогов, то частота Р имеет номинальное значение. При превьшюшги еличиной S верхнего порога пороговый лок 8 изменяет код на входе управляймогх генератора 9 так, что частота возрастает, считывание информации npivисходит быстрое и содержимое блока памяти уменьшается. Наоборот, прк S меньшей нижнего порога, уменьшает ся и содержимое блока памяти растет. Величина максималь,ного отклонения частоты РСЧ от номинального значения не должна превышать допустимых для после дуюших устройств обработки значений. Таким образом, в предлагаемом устройстве принципиально не возникают асинхронные сбои, что повышает его надежность и оно решает задачу непрерывной вьщачи информации, что расширяет область его применения и позволяет более эффективно использовать канал связи. В то же время щэименение в гфед лагаемом устройстве следящего регулирования частоты существенно ограничивает объем памяти, Формула изобретения Устройство для ввода двоичной информации, содержащее формирователь тактовой частоты, выход которого подключен к первому входу распределителя .записи, выход которого соединен с первыми входами блока памяти и реверсивного счетчика, второй вход которого сое динен с вторым входом блока памяти и с выходом распределителя считыва1шя, отличающееся тем, что, с целью повышения достоверности, в него введены формщэователь утфа&ляюшего сигнала, сумматс, пороговый блок и ущэавляемый генератор, выход которого подключен к первому входу распределителя считывания, второй вход которого соединен с первым выходом фсрмирова- теля у15)авляющего сигнала, входы которого соединены с выходами реверсивного счетчика и с входами сумматора, выход которого через пороговый блок подключен к входу угфавляемого генератора, rtpa- чем второй выход формирователя у1фа&ляющего сигнала соединен с вторым входом распределителя записи, а вход фор- мирователя тактовой частотысоединен с третьим входом блока памяти, выход которого подключен к третьему входу распределителя считывания. Источники инф маяии, 1риняТые во внимание при экспертизе 1.Автсрское свидетельство СССР N 640432, кл. Н 04 J 3/06, 1978. 2.Авторское свидетельство СССР М 503369, кл. Н 04 J 3/06, 1.973 (щ)ототип).

Авторы

Даты

1982-04-30—Публикация

1980-06-02—Подача