Изобретение относится к автомати ке, вычислительной и измерительной технике, предназначено для перемножения величины, заданных частотой следования импульсов. По основному авт. св. № 278233 известно частотно-импульсное множительйо-делительное устройство, со-держащее счетчики, регистр, схемы запрета и устройство задержки-, в котором производится преобразование частот F , F, Fj в выходную частоту F. по формуле В этом устройстве первый вход устройства (пг/ которому поступают импульсы с частотой F ) соединен с информационнБми входами схем запре первой группы, управляющие входы которых соединены с разрядньами выходами первого счетчика, а выходы соединены с разрядными входами регистра, разрядные выходы регистра соединены с управляющими входами схем запрета второй группы, информационные, входы которых соединены с выходом второго счетчика, счетный -вход которого соединен со вторым входом устройства (по которому поступают импульсы с частотой Fi,) , а разрядные входы соединены с выходами схем запрета второй группы. Первый вход устройства через устройство задержки соединен с цепью сброса первого счетчика, на счетный вход, которого поступают импульсы с частотой F . Выход второго счетчика-яв-. ляется вьиходом устройства 1 . Недостатком известного устройства является малая выходная частота по сравнению с частотами сомножителей, которая приводит к низкому быстродействию устройства и большой динамической погрешности, возникающей в результате потери информации о периодах частоты первого сомножителя и делителя. Цель изобретения - уменьшение динамической погрешности и повышение быстродействия устройства. Поставленная цель достигается тем, что частотно-импульсное множителыТО -делительное устройство дополнительно содержит второй регистр, третий счетчик, третью и четвертую группы.схем запрета, второе устройство задержки и злемент ИЛИ, причем второй вход устройства соединек со

счетным входом третьего счетчика, разрядные выходы которого соединены с информационными входами схем запрета третьей группы,, управляющие входы которых соединены с разрядными выходами второго регистра, а выходы - со входами элеме.нта ИЛИ, выход которого соединен со счетньлм входом первого счетчика, разрядные выходы третьего счетчика соединены с управляющими входами схем запрета четвертой группы, выходы которых соединены с разрядными входами второго регистра, а информационные входы соединены с третьим входом устройства, который через второе устрой ствр задержки соединен с цепью сброса третьего счетчика.

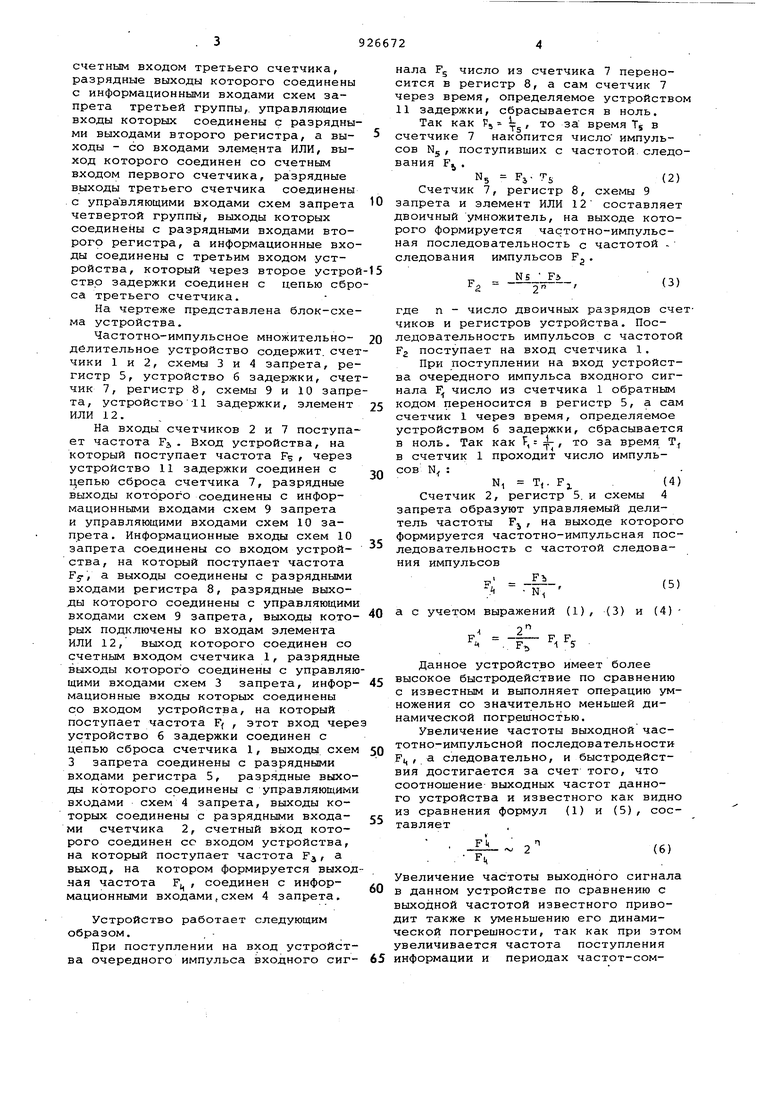

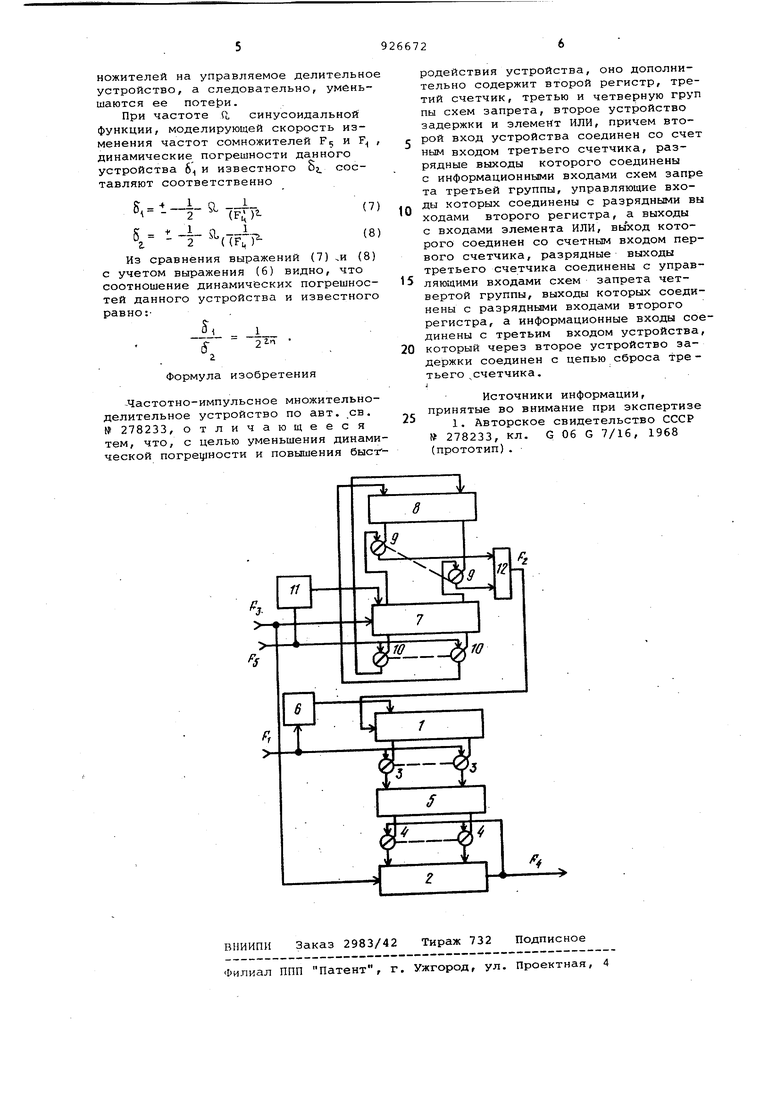

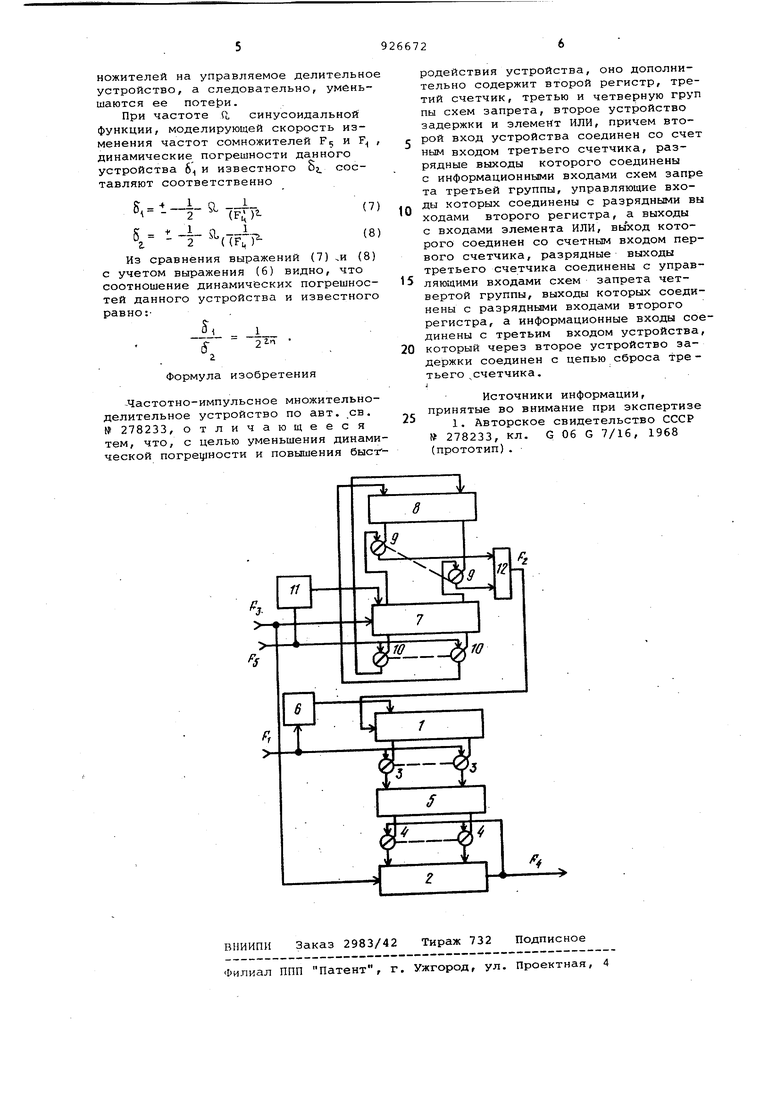

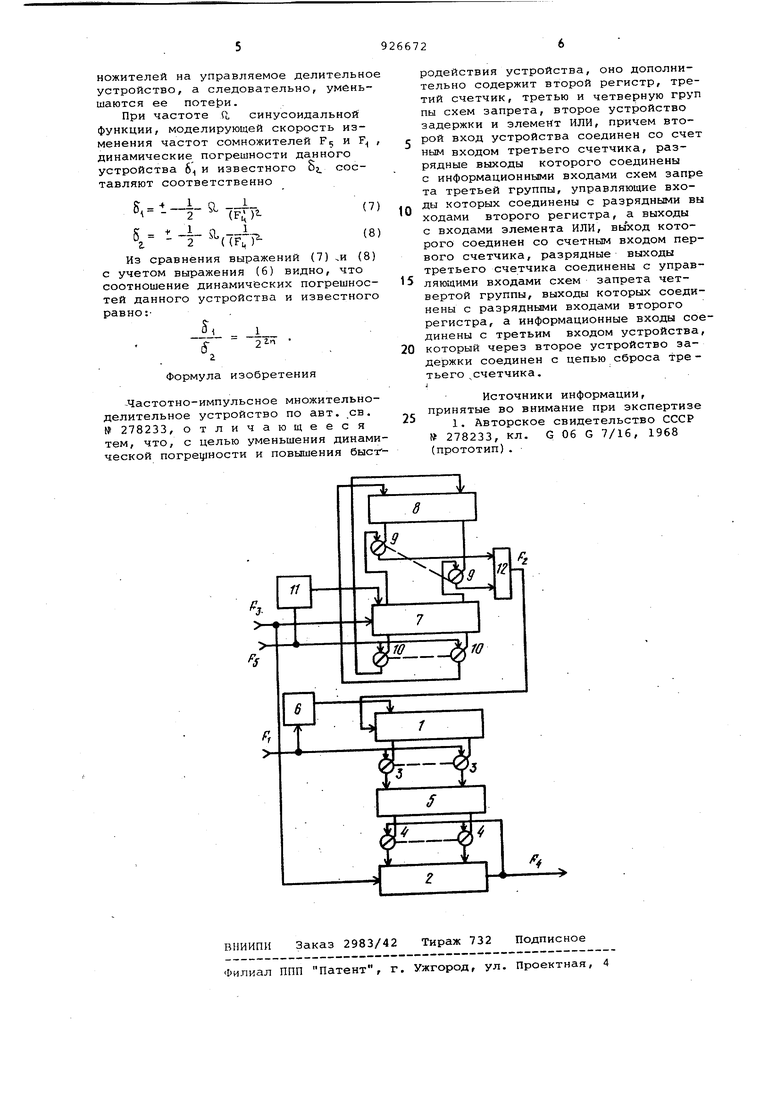

На чертеже представлена блок-схема устройства.

Частотно-импульсное множительноделительное устройство содержит, счетчики 1 и 2, схемы 3 и 4 запрета, регистр 5, устройство б задержки, счетчик 7, регистр 8, схемы 9 и 10 запрета, устройство 11 задержки, элемент ИЛИ 12.

На входы счетчиков 2 и 7 поступает частота F,, . Вход устройства, на который поступает частота FS, через устройство 11 задержки соединен с цепью сброса счетчика 7, разрядные выходы которого соединены с информационными входами схем 9 запрета и управляющими входами схем 10 запрета. Информационные входы схем 10 запрета соединены со входом устройства, на который поступает частота Fj-, а выходы соединены с разрядными входами регистра 8, разрядные выходы которого соединены с управляющими входами схем 9 запрета, выходы которых подключены ко входам элемента ИЛИ 12, выход которого соединен со счетным входом счетчика 1, разрядные выходы которого соединены с управляющими входами схем 3 запрета, информационные входы которых соединены со входом устройства, на который поступает частота F , этот вход чере устройство 6 задержки соединен с цепью сброса счетчика 1, выходы схем 3 запрета соединены с разрядными входами регистра 5, разрядные выходы которого соединены с управляющими входами схем 4 запрета, выходы которых соединены с разрядными входами счетчика 2, счетный вход которого соединен се входом устройства, на который поступает частота F, а выход, на котором формируется выходная частота Fц , соединен с информационными входами,схем 4 запрета.

Устройство работает следующим образом.

При поступлении на вход устройства очередного импульса входного сигнала Fg число из счетчика 7 переносится в регистр 8, а сам счетчик 7 через время, определяемое устройством 11 задержки, сбрасывается в ноль.

Так как PS Vs время Tg в счетчике 7 накопится число импульсов Ng, поступивших с частотой следования Fj .

N5 Fj. TS(2)

Счетчик 7, регистр 8, схемы 9 запрета и элемент ИЛИ 12 составляет двоичный умножитель, на выходе которого формируется частотно-импульсная последовательность с частотой следования импульсов F.

NsJJEl

(3)

F - 2

где n - число двоичных разрядов счечиков и регистров устройства. Последовательность импульсов с частотой Fg поступает на вход счетчика 1.

При поступлении на вход устройства очередного импульса входного сигнала F число из счетчика 1 обратным кодом переносится в регистр 5, а сам счетчик 1 через время, определяемое устройством 6 задержки, сбрасывается в ноль. Так как , fT время Т в счетчик 1 проходит число импульсов NY :

(4)

Nl Т,. F;

Счетчик 2, регистр 5. и схемы 4 запрета образуют управляемый делитель частоты FJ, на выходе которого формируется частотно-импульсная последовательность с частотой следования импульсов

- - 1ь

(5)

I - - N,

а с учетом выражений (1), (3) и (4)Г)

- -2

F F - F 1 5

Данное устройство имеет более высокое быстродействие по сравнению с известным и выполняет операцию умножения со значительно меньшей динамической погрешностью.

Увеличение частоты выходной частотно-импульсной последовательности F,, , а следовательно, и быстродействия достигается за счет того, что соотношение выходных частот данного устройства и известного как видно из сравнения формул (1) и (5), составляет

Fk

(6)

Увеличение частоты выходного сигнала в данном устройстве по сравнению с выходной частотой известного приводит также к уменьшению его динамической погрешности, так как при этом увеличивается частота поступления информации и периодах частот-сом

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство для цифрового измерения разности частот электрических колебаний | 1977 |

|

SU739430A1 |

| Генератор импульсов с линейно-изменяющейся частотой | 1982 |

|

SU1094139A1 |

| Частотно-импульсное делительное устройство | 1980 |

|

SU898429A1 |

| Устройство формирования сигнала сдвинутой частоты | 1986 |

|

SU1394426A1 |

| Устройство для измерения частоты пульса | 1984 |

|

SU1211662A1 |

| Устройство для умножения частоты следования импульсов | 1986 |

|

SU1410027A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

Авторы

Даты

1982-05-07—Публикация

1979-12-28—Подача