со со оо J

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Умножитель частоты | 1987 |

|

SU1448394A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Многоканальное устройство для обработки первичной информации | 1984 |

|

SU1234851A1 |

| Устройство для измерения частоты | 1988 |

|

SU1550434A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Умножитель частоты | 1983 |

|

SU1176439A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах автоматического управления. Цель изобретения - повышение точности умножения за счет выполнения операции линеаризации. Умножитель частоты содержит первый элемент 1 задержки, делитель 2 частоты, первый счетчик 3 импульсов, регистр 4, второй счетчик 5 импульсов, узел 6 формирования поправок, второй элемент 7 задержки, узел 8 управляемой задержки и генератор 9 тактовых импульсов, соединенные между собой функционально. 2 з.п.ф-лы, 2 ил.

фuг.f

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах автоматического управления о

Цель изобретения - повышение точности умножения за счет вьтолнения операции линеаризациио

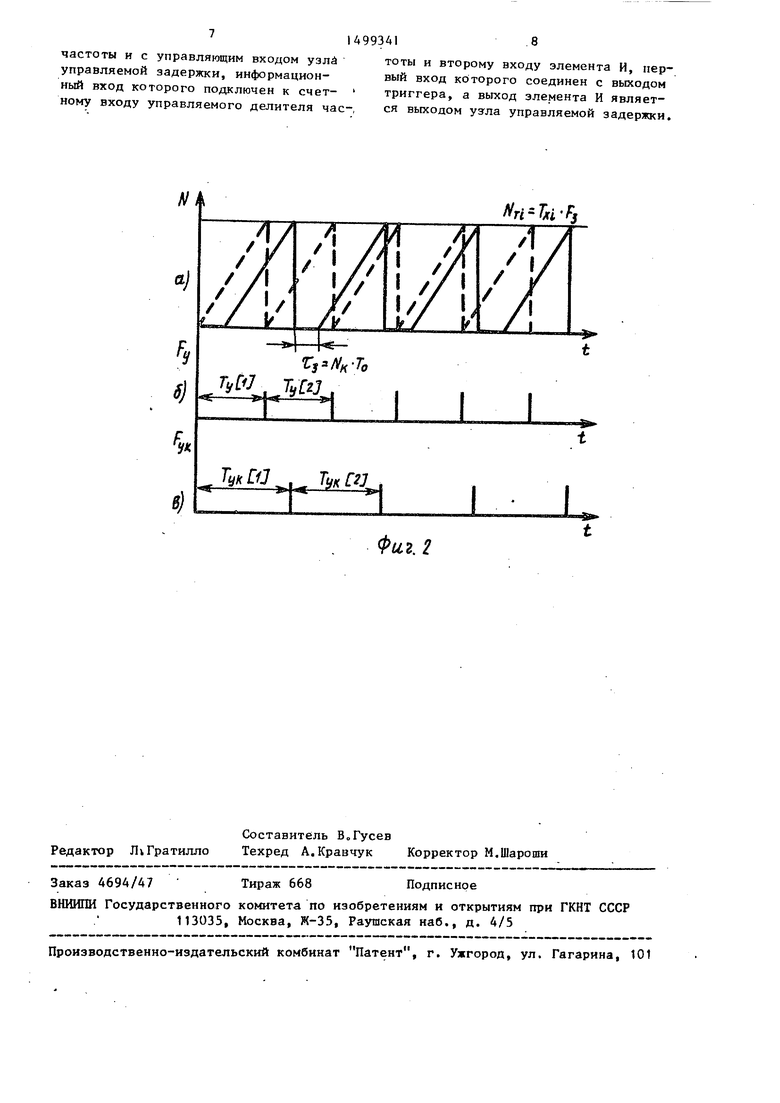

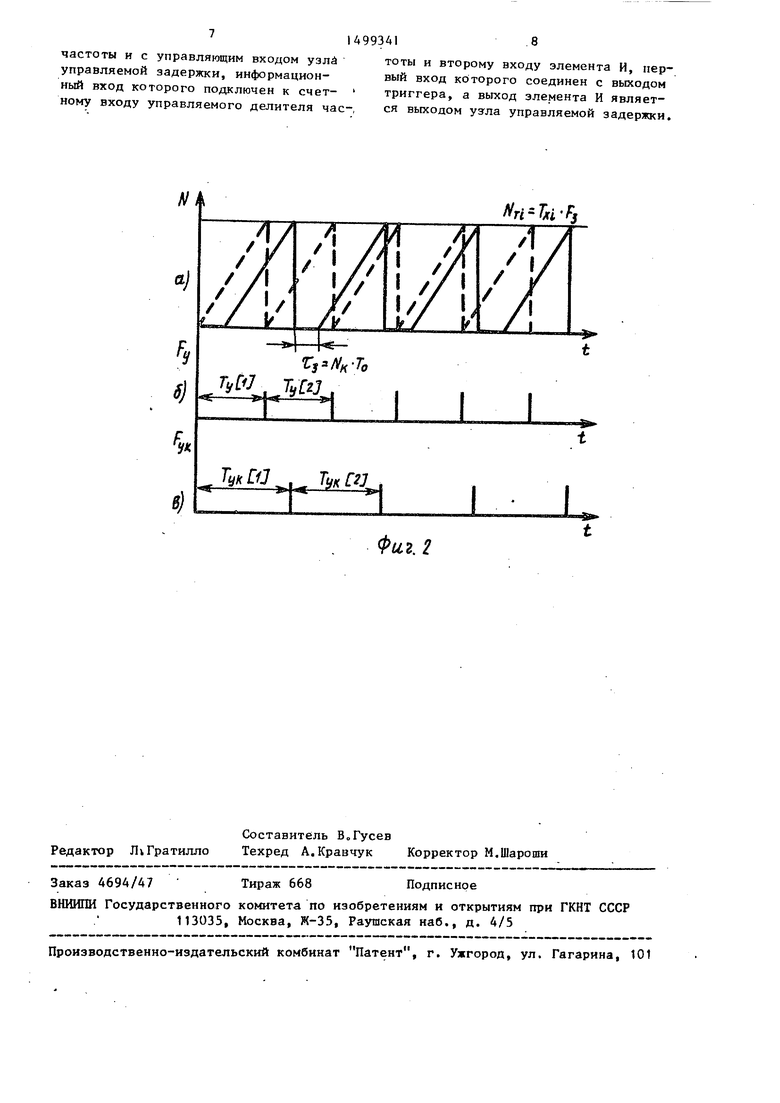

На фиг.1 представлена функциональная схема умножителя; на фиг„2 временные диаграммы работы умножителя

Умножитель частоты содержит первый элемент 1 задержки, делитель 2 частоты, первый счетчик 3 (импуль1499341

- 10

15

25

сов), регистр 4, второй счетчик 5 (импульсов), узел 6 формирования поправок, второй элемент 7 задержки, узел 8 управляемой задержки и генератор 9 тактовых импульсов, соединен-20 ные между собой функционально.

Узел 8 управляемой задержки содержит управляемый делитель 10 частоты, триггер И и элемент И 12, соединенные между собой функционально.

Узел 6 формирования поправок содержит схему 13 сравнения кодов,первый блок 14 памяти, счетчик 15 импульсов, второй блок 16 памяти и регистр 17,соединенные между собой функционально о

Умножитель работает следующим образом.

При поступлении на информационный

вход очередного импульса входного сигнала осуществляется перепись содержимого счетчика 3, в котором формируется кодовый эквивалент периода входной импульсной последовательности, в регистр 4 и перепись кода поправки из блока 16 памяти в регистр 17. Импульс с выхода элемента 1 задержки обнуляет делитель 2, счетчик 3 и счетчик 15о -Код поправки N|, пе30

35

40

блоков 14 и i6 памяти объединены с выходами счетчика 15, состояние ко торого определяется числом импульс формирующихся на выходе схемы 13 сравнения кодов в течение интервал времени, равного периоду Т следов ния импульсов входной последовател ности Соответствующие значения ко дов поправок N,., хранящиеся в блок 16 памяти в момент окончания период Tj, переписываются в регистр 17„

Перепись кодовых эквивалентов N периодов входной импульсной последовательности из регистра 4 в счет чик 5 обеспечивается импульсами эл мента. 7 задержкис Кроме того, импульсы с выхода элемента 7 задержки поступают на синхровход делителя 10 частоты, что обеспечивает перепись содержимого регистра 17 в делитель 10 частоты, а такжр на R-вход триггера IK Данный сигнал переводи триггер в нулевое состояние. При . этом элемент И 12 закрыт, т.е на читающий вход счетчика 5 прекращае ся поступление импульса с генерато 9 тактовых импульсов„ С появлением импульса на выходе делителя 10 час ты триггер I1 переводится в единичное состояние, открывается элемент И 12 и на вычитающий вход счетчика 5 начинают поступать импульсы с генератора 9 тактовых импульсов. Таким образом обеспечивается задержка поступления на вход счетчика 5 и пулъсной последовательности F на и тервал С, N . TO . Как только сче чик 5 установится в состояние О, импульс с выхода его старшего разря да поступает на выход умножителя ча тоты и на элемент 7 задержки. Затем цикл преобразования повторяет ся. Процесс преобразования в данном

реписываемый в регистр 17, формирует- 5 умножителе частоты поясняется вреся узлом 6 формирования поправок следующим образом

На первую группу входов схемы 1.р сравнения кодов узла 6 формирования поправок поступают текущие коды N. Т, F, где - период входного сигнала; Fj - частота заполнения с выходов счетчика 3, а на вторую группу входов схемы 13 сравнения кодов поступают коды с блока 14 памяти,значение каждого из которых соответст- .вует i-му узлу аппроксимации характеристики преобразования измерительного преобразователя. Адресные входы

50

менными диаграммами (фигс2)о Причем на фиг.2а показан процесс преобразо вания кода N в частоту, выполняемо го на основе счетчика 5. На в соответственно показаны выходная импульсная последовательность F(. бе коррекции и откорректированная импульсная последовательность F

Т

55

Таким образом, придавая определе ную нелинейность характеристике пре образования умножителя частоты по о .ношению к характеристике преобразования частотного датчика (путем вве

10

15

25

-20

30

35

40

блоков 14 и i6 памяти объединены с выходами счетчика 15, состояние которого определяется числом импульсов, формирующихся на выходе схемы 13 сравнения кодов в течение интервала времени, равного периоду Т следования импульсов входной последовательности Соответствующие значения кодов поправок N,., хранящиеся в блоке 16 памяти в момент окончания периода Tj, переписываются в регистр 17„

Перепись кодовых эквивалентов N- периодов входной импульсной последовательности из регистра 4 в счетчик 5 обеспечивается импульсами элемента. 7 задержкис Кроме того, импульсы с выхода элемента 7 задержки поступают на синхровход делителя 10 частоты, что обеспечивает перепись содержимого регистра 17 в делитель 10 частоты, а такжр на R-вход.. триггера IK Данный сигнал переводит триггер в нулевое состояние. При . этом элемент И 12 закрыт, т.е на вычитающий вход счетчика 5 прекращается поступление импульса с генератора 9 тактовых импульсов„ С появлением импульса на выходе делителя 10 частоты триггер I1 переводится в единичное состояние, открывается элемент- И 12 и на вычитающий вход счетчика 5 начинают поступать импульсы с генератора 9 тактовых импульсов. Таким образом обеспечивается задержка поступления на вход счетчика 5 им- пулъсной последовательности F на интервал С, N . TO . Как только счетчик 5 установится в состояние О, импульс с выхода его старшего разряда поступает на выход умножителя частоты и на элемент 7 задержки. Затем цикл преобразования повторяет ся. Процесс преобразования в данном

5 умножителе частоты поясняется вре

менными диаграммами (фигс2)о Причем на фиг.2а показан процесс преобразования кода N в частоту, выполняемого на основе счетчика 5. На и в соответственно показаны выходная импульсная последовательность F(. без коррекции и откорректированная импульсная последовательность F

55

Таким образом, придавая определенную нелинейность характеристике преобразования умножителя частоты по от- .ношению к характеристике преобразования частотного датчика (путем вве

дения в блок 16 памяти соответствующих значений поправок ), можно обеспечить линеаризацию ) характеристики преобразования последнего на основе метода кусочно-ступенчатой аппроксимации. Умножитель частоты реализует свои функции, Тое, вьтолняет измерительное умножение и функциональное преобразование с допустимой погрешностью в условиях, когда входной сигнал с частотой Fy. является медленно изменяющейся функцией времени. Данное требование наряду с требованием того, что характеристика преобразов-ания частотного датчика должна быть однозначной и непрерывной на всем интервале наблюдения

F, е

(F.

:),

УЛЛИИ VMoKc Я X/яин Тумаке соответственно минимальное и максимальное значения частоты входного сигнала, является важным с точки зрения обеспечения допустимой погрешности преобразования.

Формула изобретения

мой задержки, управляющий вход которого соединен с выходом второго элемента задержки, выход узла управляемой задержки.соединен с вычитающим

5

входом второго счетчика, а установочные входы узла управляемой задержки соединены соответственно с разрядными выходами узла формирования по10 правок, синхровход которого соединен с информационным входом умножителя, выход первого элемента задержки соединен с управляющим входом узла формирования поправок, установочные вхо-,

15 ДЬ которого соединены соответственно с р азрядными выходами первого счетчика.

ирования поправок содержит схему сравнения кодов, первый блок памяти, счетчик импульсов, второй блок памяти и регистр, причем первая группа входов схемы сравнения кодов соединеа с соответствуюш1.1ми установочными входами узла формирования поправок, торая группа входов которой под- ключена к информационным вькодам первого блока памяти, адресные входы которого, поразрядно объединенные с адресными входами второго блока памяти, подключены к соответствующим выходам счетчика импульсов, счетный вход которого соединен с выходом схемы сравнения кодов, а вход установки в О подключен к управляющему входу узла формирования поправок, причем информационные выходы второго блока памяти подключены к соответствующим входам регистра, разрядные выходы которого соединены соответственно с разрядными выходами узла формирования поправок, а синхронизирующий вход регистра подключен к синхровходу узла формирования поправок.

50

частоты и с управляющим входом узлйтоты и второму входу элемента И, перуправляемой задержки, информацион-вый вход которого соединен с выходом

ный вход которого подключен к счет- триггера, а выход элемента И являетному входу управляемого делителя час-,ся выходом уз-ла управляемой задержки.

)

$)

Гу/УЛ,Г,Ш

т-« ТукШТукС2

,l fj

I I I

L

Физ.2

| Умножитель частоты | 1978 |

|

SU750711A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-22—Подача