Изобретение относится к автоматике и вычислительной технике и может быть использсюано, в устройствах телеметрии, связи и управления. Известен экстраполятор, содержащий два интегратора, блок, масштабировани51, элемент задержки, два сумматора 1. Его недостаток - невысокая точность эстраполяции и неприспособленность к работе с дискретным входным сигналом, поступающим в тактовые моменты времени. Наиболее близким по технической сущ ности к предлагаемому является экстраполятор, содержащий аналоговый регистр сдвига с тремя выходами и три интегрирующих усилителя с дифферашиальными входами(23. Его недостаток - наличие методической погрешности при экстраполяции полинома второй степени. Цель изобретения - повышение точнос ти экстраполяции. Указанная цель достигается тем, что экстрапопятор, содержащий аналоговый решстр сдвига, информационный вход которого является входом экстраполятора, а управляющий вход соединен с шиной тактовых импульсов, и два интегратора, причем первый выход аналогового регистра .сдвига соединен с первым неинвертиру юшим входом первого интегратора, а второй выход аналогового регистра - сдвига соединен с инвертирующим входом первого интегратора, дополнительно содержит сумматор, первый выход аналогового регистра сдвига соединен с первым входом сумматора и с первым неинвертирующим входом, второго интегратора, второй выход аналогового регистра сдвига соединен с инвертирующим входом второго интегратора, третий выход аналогового регистра сдвига соединен со вторыми неинвертируюшими входами первого и второго интег раторов, выход второго интегратора соединен с третьим неимвертирующим входом первого интегратфа, выход которого соеоинен с вторым входом сумматора, а управляющие вхоцы интеграторов соединены с шиной тактовых импульсов. ,

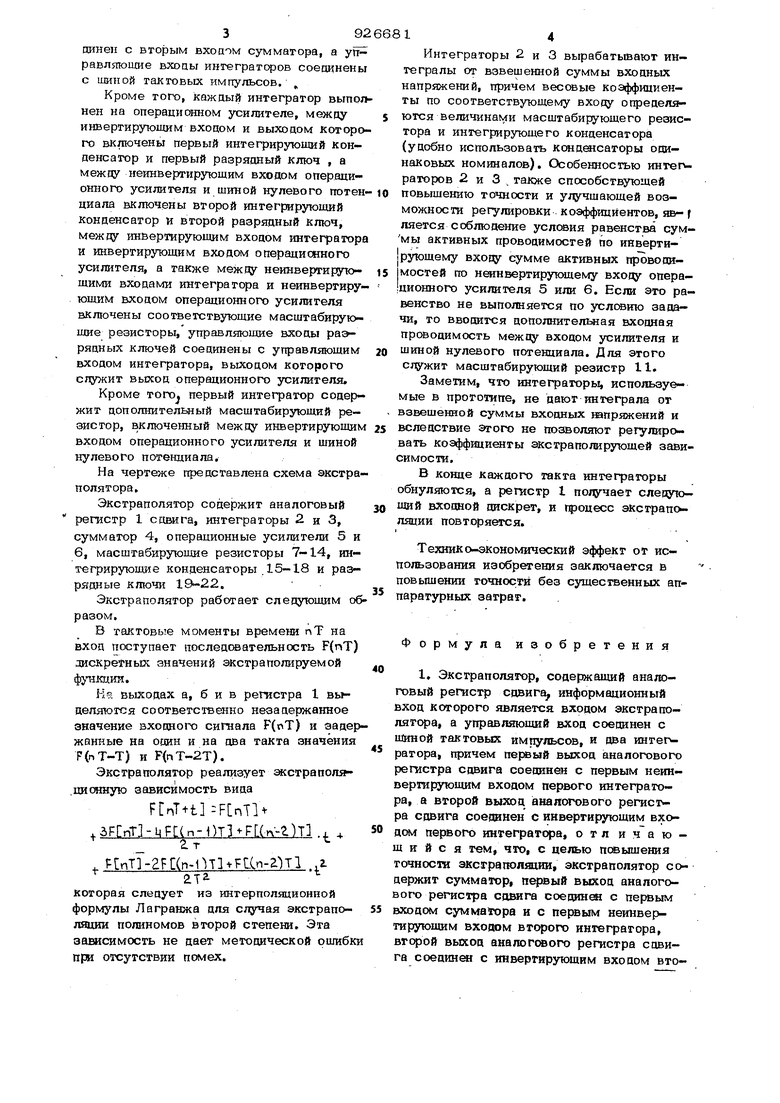

Кроме тогчэ, каждый ингегратор выполнен на операционном усилителе, между инвертирующим входом и выходом которого включены первый интегрируюищй конденсатор и первый разрядный ключ , а между неинвертирующим входом операционного усилителя и шиной нулевого потенциала включены второй интегрирующий конденсатор и второй разрядный ключ, межцу инверигрующим входом интегратора и инвертирующим входом операционного усилителя, а также межцу неинвертирующими входами интегратора и неинвертирующим входом операционного усилителя включены соответствующие масштабирующие резисторы, управляющие вхоць разрядных ключей соединены с управляющим входом интегратора, выходом которого служит выход операционного усилителя.

Кроме того, первый интегратор содержит дополнительный масштабирующий резистор, вкточенный между инвертирующим входом операционного усилителя и шиной нулевого потенциала.

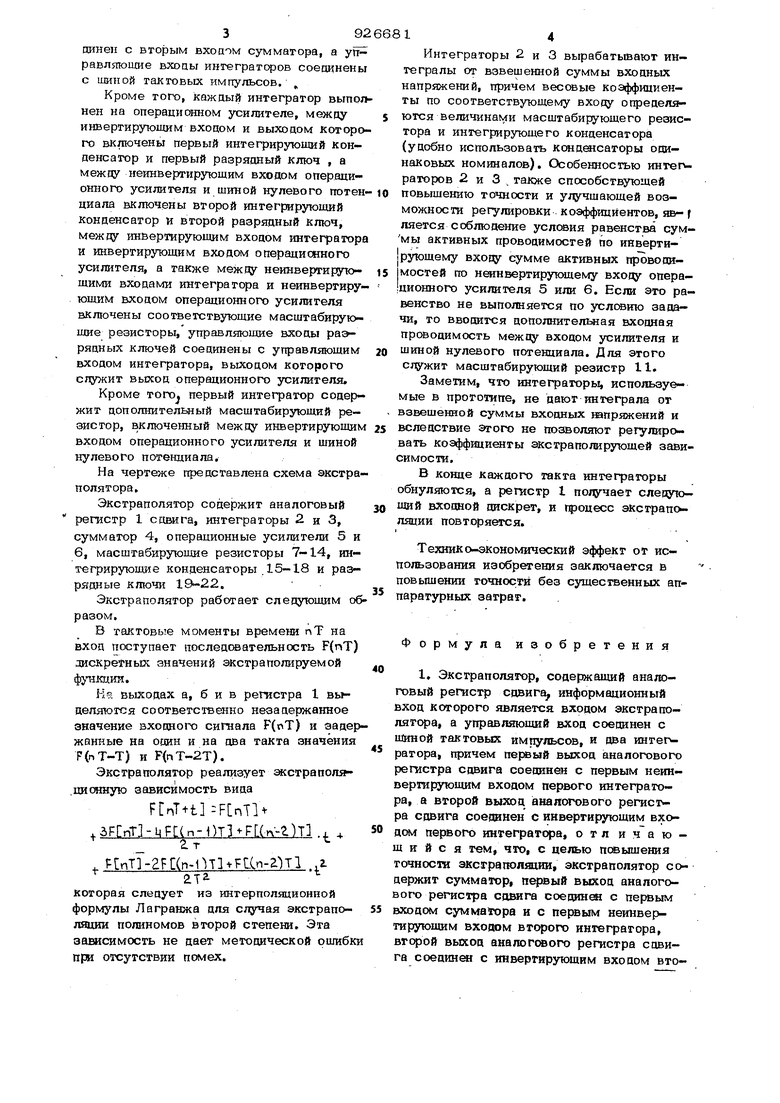

На чертеже представлена схема экстраполятора.

Экстраполятор содержит аналоговый регистр 1 ссшига, интеграторы 2 и 3, сумматор 4, операционные усилители 5 и 6, масштабирующие резисторы 7-14, интегрирующие конденсаторы ,15-18 и разрядные ключи .

Экстраполятор работает следующим образом.

В тактовые моменты времени пТ на вхоц поступает последовательность F(nT) дискретных значений экстраполируемой функции.

Hs выходах а, б и в регистра 1 выделяются соответственно незадержанное значение входаого сигнала F(riT) и задержанные на один и на два такта значения F() и F nT-2T).

Экстраполятор реализует экстраполя.ционную зависимость вида

,зрГпТ -иР(пН)т1 р и--гПЗ..

, prnTT-2Fr(n.nTbFLCn-a)Tl .г

2Т .

которая следует из интерполяционной формулы Лагранжа для случая экстраполадии полиномов второй степени. Эта зависимость не дает методической ригабки при отсутствии помех.

Интеграторы 2 и 3 вырабатьшают интегралы от взвешенной суммы входных напряжений, причем весовые коэффициенты по соответствующему входу определяются величинами масштабирующего резистора и интегрирующего конденсатора (удобно использовать кондагсагоры одинаковых номиналов). Особенностью интег раторов 2 и 3 . также способствующей повышению точности и ул чшающей возможности регулировки коэффициентов, яв-f ляется соблюдение условия равенства суммы активных проводимостей по инвертирующему вхоцу сумме активных пр7|водимостей по неянвертирующему вхос операционного усилителя 5 или 6. Если это равенство не выполняется по успсвкю задачи, то вводится дополнительная входная проводимость между входом усилителя и шиной нулевого потенциала. Для этого сдужит масштабирующий резистр 11.

Заметим, что интеграторы, используемые в прототипе, не дают интеграла от взвешенной суммы входных иапряжений и вследствие этого не позвол5пот регулировать коэффициенты экстраполирующей зависимости.

В конце каждого такта интеграторы обнуляются, а регистр I получает следующий входной дискрет, и процесс экстраполяции повторяется.

Технико-экономический эффект от использования изобретения заключается в повышении точности без существенных аппаратурных затрат.

Формула изобретения

1. Экстраполятор, содержащий аналоговый регистр cдвигa информационный вход которого $шляется входом экстраполятора, а управляющий вход соединен с Шиной тактовых импульсов, и два интег ратора, причем первый выход аналогового регистра сдвига соединен с первым неинвертидтощим входом первого интегратора, а вгорой выход аналогового регистра сдвига соединен с инвертирующим входом первого ингегратора, огл ичающ и и с я тем, что, с це;шю повышения точности эксграполяции, экстраполятор содержит сумматор, первый выход аналогового регистра сцетга соединен с первым входом сумма ра и с первым неинвер тирующим входом второго ингегратора, вгорой выход аналогового регистра сдвига соедини с инвертирующим входом в торого интегратора, третий выхоа аналогового регистра сцшга соединен со вторыми иеинвертируюишми входами первого и второго интеграторов, выход второго интег ратора соединен с третьим неинвертируюшим входом первого интегратора, выход которого соединен с вторым входом сумматора, а управл5пошие входы интеграторов соесЕИнены с шиной тактовых импульсов. 2. Экстраполятор по п. 1, о т л и чающийся тем, что каждый интег ратор выполнен на операционном усилителе, между инвертирующим входом и выходом которого включены первый интегриру кшшй конденсатор и первый разрядный Ключ, а между неинвертирующим входом операционного усилителя и шиной ну пев оiro потенциала включены второй интегрирующий КонденсаторИ вгфой разрядный кгаоч, межЕ инвертирующим входом WH-тегратора и интегрирующим входом операционного усипятепя, а также между неинвертирующими входами интегратора и неинвертирующим входом операционного усилителя включены соответствующие масштабирующие резисторы, управл$йощие входы разрядных ключей соединены с уп равляющим входом интегратора, выходом которого является выход операционного усилителя. 3. Экстраполятч)р поппДи2 отличающийс тем, что тюрвый ин-тегратор содержит йопошштельный маещтабирующнй резистор, включенный медкяу инвертарующим входом операционного утзя- лителя и щиной нулевого потеяциалв. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство, СССР N 251947, кл. G Об G 7/30, 1968. 2.Авторское свидетельство СССР № 467368. К1ь G Об G 7/ЗО, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполятор | 1980 |

|

SU934504A1 |

| Интегратор | 1989 |

|

SU1615752A1 |

| Дифференцирующее устройство | 1980 |

|

SU920758A1 |

| Задатчик скорости | 1984 |

|

SU1234809A1 |

| Функциональный аналогоцифровой преобразователь | 1982 |

|

SU1072066A1 |

| Дифференцирующее устройство | 1983 |

|

SU1120361A1 |

| Аналого-цифровой преобразователь | 2021 |

|

RU2760906C1 |

| Аналоговый интегратор напряжения | 1987 |

|

SU1553988A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Аналоговый интегратор переменного напряжения | 1986 |

|

SU1336047A1 |

Авторы

Даты

1982-05-07—Публикация

1980-07-16—Подача