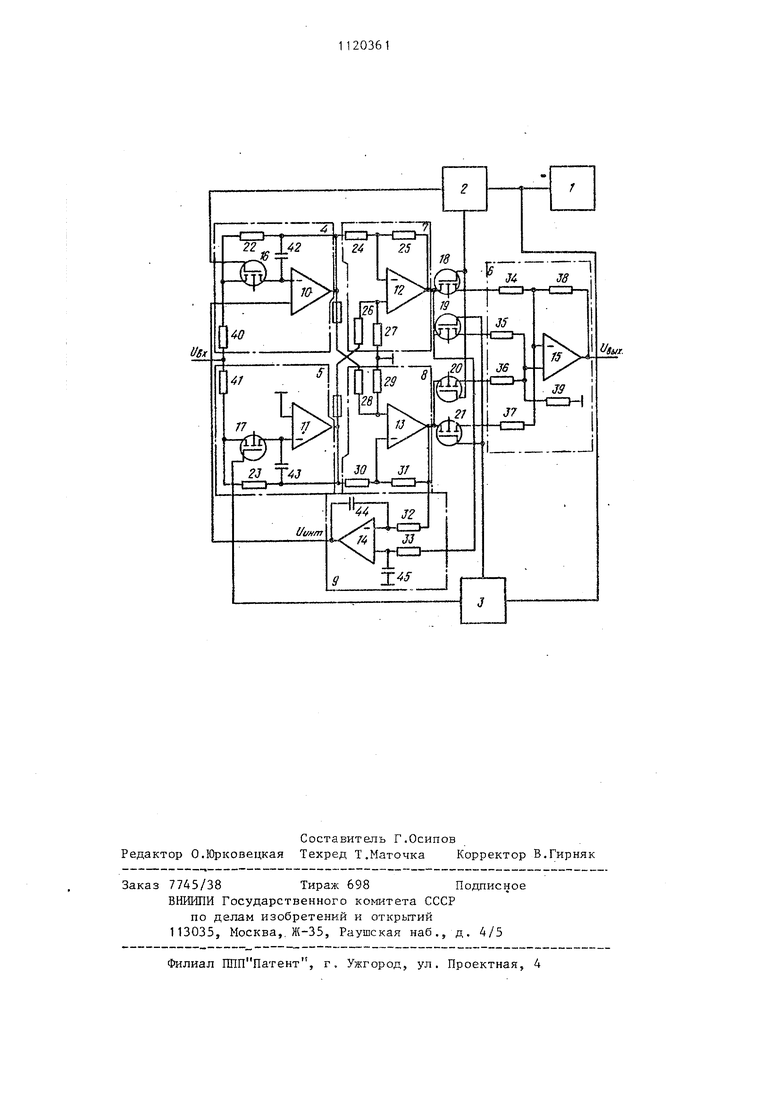

Изобретение относится к аналогсв в лчислительной технике и может быть использовано для получения производ ной от аналогового сигнала, задавае мого в непрерывной, ступенчатой или амллитудно-модулированной форме, Известно устройство, работа кото рого основана на. взятии разности входных значе1-шй в тактовые моменты времени, содерл ащее два запоминаюiiti-fx з.пемента,, выполненных на операци :онпом усштителе с интегрирующим кон денсатором и ключом, выходы sanot-m:на Л15ИХ элементов подключены к блоку вьмитаниЯэ вьгход которого соединен с фазовым детектором, на выходе которого }зьщеляется постоянное напряжение, пропорциональное производной. Згшо№1наюш;1е элементы поочередно уп равляются от генератора тактовых имггульсов m . Недостатком устройства Я1шяется наличие пульсаций па вькоде из-за дрейфа нуля и неидентичпости характеристик операхдаонных уси;штелей. Наиболее близким к изобретению по технической сущности яютяется диф ференцирующее устройство, содержащее два запоминающих элемента, входы которых подключены к входу устройства, а вг гходы - к входам блока вьиита ниЯз вь1ход которого через ключи соединен с входами выходного cyм aтopa генератор тактовых импульсов, с выходом которого связаны два формирователя импульсов, которых сое динены с управляющими входами ключей и з.апомипающих элементов 2j, Недостаток известпого устройства заключается в наличии пульсаци выходного напряжения из-за дрейфа пуля и пеидептичности характеристик операционных усилителей и других активных элементов . Цель изобретения - повышение точнести за счет устранения влияния невдептичпости характеристик и дрейфа ИЗля операциопных усилителей. Цель достигается тем, что д ффepe цирующее устройство, содержащее перЕый и второй запомипаютцие элементы, вьпюлпениые каждый на операционном усилителе, мезкду инвертирующгп входом к В1 1ходом которого включеиы интегрирующий конденсатор и цепь из по следовательно соединеиных первого масштабирующего резистора и первого ключа, а с общим выводом первого ключа и первогб масштаоирующего резистора соединен первый влвод второго масп1табирующего резистора, вторые выводы вторьк масштабгарующих резисторов обоих запоминающих элементов соединены с входом устройства, первьй блок вьиитания, соответствуюац-ie входы которого соединены с выходами onepaiJ ioHHbEc усилителей запоМ1-1наюцшх элементов, первого блока вычитания через второй ключ сое;: ;инен с первым инвертирующим входом выходного сумматора-вычитателя, а через третий ключ - с его первьпм неинвертирую11;им входом, генератор тактовых имгошьсов, выход которого соединен с вxoдa ш первого и второго формирователей импульсов, первые выходы которьк соединены с управляющим входом первого ключа соответствующего запом1- нающего элемента, а вторые выходы с управляюислми входами соответственно второго и третьего ключей,содержит также интегратору второй блок вычитания, четвертый и пятьй ключи, при этом вход вычитаемого первого блока вычитания соединен с входом уменьшаемого второго блока вычитания, вход уменьшаемого первого блока вычитания - с входом вычитаемого второго блока вычитания, вькоды первого и второго блоков вычитания соединены соответственно с неинвертируюпщм и инвертирующИ1у1 входами интегратора, выход которого соединен с .неинвертирующим входом операционного усилителя пернюго запоминающего элемента, неинвертирующий вход операционного усилителя второго запомизгающего эх емента соединен с шиной нулевого потенциала, выход второго блока вычитания через четвертый ключ соединен с вторым неинвертирующим входом выходного сумматоравычитателя J а через пятьй ключ - с его вторым инвертирующим входом, управляющий вход второго ключа соединен с угфавляющим входом четвертого ключа а управляюа1дй вход третьего ключа - с управляюгдим входом пятого ключа. Иа чертенке представлена схема предлагаемого устройства. Устройство coдepжIiт генератор 1 тактовьк иь-лульсов, формирователи 2 и 3 и даyльcoв5 запомт-тнающие элементы 4 и Sj выходной сумматор-дьгчитатель 6, блоки 7 и 8 вычитания, ките3гратор 9, операционные усилители 1015, ключи 16-21, масштабирующие резисторы 22-41, интегрирующие конденсаторы 42-45. Устройство работает следующим образом. Генератор 1 тактовых импульсов вы рабатывает управляющее напряжение та товой частоты, которое поступает на входы двух формирователей 2 и 3 импульсов, каждьм из которых осуществляет преобразование последователь ности тактовых импульсов в две последовательности управляющих импульсов, поступающих на управляющие вход соответствукщих ключей. С первых выходов формирователей на управляющие входы ключей 16 и 17 поступают импульсы малой длительности дпя обновления запоминаемого входного напряжения. Эти импульсы сдвинуты во времени один относительно другого на половину интервала, с вторых выходов формирователей 2 и 3 импульсов на управляющие входы ключей 18, 20 и 19, 21 поступают импульсы, передние фронты которых совпадают во времени с передними фронтами импульсов, идущих с первых выходов, а длительность равна половине периода следования. В результате ключи 18 и 19, а также 361 20 и 21 поочередно открыты. На выходах блоков 7 и 8 вычитания формируются при этом два противофазных переменных напряжения прямоугольной формы с a шлитyдoй, пропорциональной величине производной входного сигнала . На выходе выходного сумматоравычитателя 6, образуется постоянное напряжение, знак и величина которого соответствуют производной входного сигнала. При разомкнутом контуре, содержа-, щем интегратор, и наличии дрейфа нуля операционных усилителей на выходе появляется пульсация, амплитуда которой пропорциональна величине дрейфа. При замкнутом контуре интегратора выходное напряжение блоков 7 и 8 вычитания, поступающее на диф(1)еренциальный вход интегратора, после интегрирования и подачи на вход one- : рационного усилителя 10, вызывает компенсацию дрейфа нуля усилителей и устраняет пульсации выходного напряжения . Таким образом, в предложенном устройстве уменьшены пульсации, вызван- ные дрейфом нуля и неточностью балансировки операционных усилителей.

US.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1980 |

|

SU920758A1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Устройство для определения параметров трехэлементных двухполюсных цепей | 1990 |

|

SU1758587A1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ С ПЕРИОДИЧЕСКОЙ КОРРЕКЦИЕЙ ДРЕЙФА | 2011 |

|

RU2480893C1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| Экстраполятор | 1980 |

|

SU926681A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| Аналоговый решающий узел | 1979 |

|

SU849244A1 |

| Устройство для измерения сопротивления | 1984 |

|

SU1239608A1 |

ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТрО, содержащее первый и второй запоминающие элементы, выполненные каждый на операционном усилителе, между инвертирующим входом и выходом которо-. го включены интегрирующий конденсатор и цепь из последовательно соединенных первого масштабирующего резистора и первого ключа, а с общим выводом первого ключа -и первого -масгитабирующего резистора соединен первый вывод второго масштабирукяцего резистора, вторые выводы вторых масштабирующих резисторов обоих запоминающих элементов соединены с входом устройства, первый блок вычитания, соответствующие входы которого соединены с выходами операционньк усилителей запоминающих элементов, выход первого блока вычитания через второй ключ соединен с первым инвертирующим входом выходного сумматора-вычитателя, а через третий ключ - с его первым неинвертирующим входом, генератор тактовых импульсов, выход которого соединен с входами первого и второго формирователей импульсов, первые выходы которых соединены с управлякящгми входом первого ключа соответствующего запоминаюп;его элемента, а вторые выходы - с управляющими входами соответственно второго и третьего ключей, отличающеес я тем, что, с целью повышения точности .за счет устранения влияния неидентичности характеристик и дрейфа нуля операционных усилителей, оно содержит интегратор, второй блок вычитания, четвертый и пятый ключи, при этом вход вычитаемого первого блока вычитания соединен с входом уменьщаеi мого второго блока вычитания, вход меньшаемого первого блока вычита(Л ния - с входом вычитаемого второго блока вычитания, выходы первого и второго блоков вычитания coeдIiнeны соответственно с неинвертирующим и инвертирующим входами интегратора, выход которого соединен с неинвертирующим входом операционного усилителя ГчЭ первого запоминающего элемента, неинвертирующий вход операционного усио со лителя второго запоминающего элемента соединен с шиной нулевого потенциала, выход второго блока вычитания через четвертый ключ соединен с вторым неинвертирукщим входом выходного сумматора - вычитателя, а через пятый ключ - с его вторым ин вертирующим входом, управляющий вход второго ключа соединен с управляющим входом четвертого ключа, а управляющий.вход третьего кл1сгча - с управляющим входом-пятого ключа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для дифференцированияэлЕКТРичЕСКиХ СигНАлОВ | 1979 |

|

SU851419A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Автоматика, телемеханика и вычислительная техника | |||

| Реферативный журнал ВИНИТИ, 1978, т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-10-23—Публикация

1983-01-10—Подача