(5) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

I

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти на базе интегральных запоминающих устройств.

Известно запоминающее устройство, в котором для автоматического исправления ошибок, возникающих в процессе хранения, подлежащие хранению данные кодируются с помощью кодов, исправляющих ошибки. При э.том в устройство вводятся избыточные разряды, кодирующее и декодирующее устройстве tn.

Однако в запоминающих устройствах подобного типа число контрольных разрядов, необходимых для исправления некоторого заданного числа ошибок в слове, великЬ и высока сложность кодирующих и декодирующих устройств.

Наиболее близким к предлагаемому является запоминающее устройство с КОНТРОЛЕМ

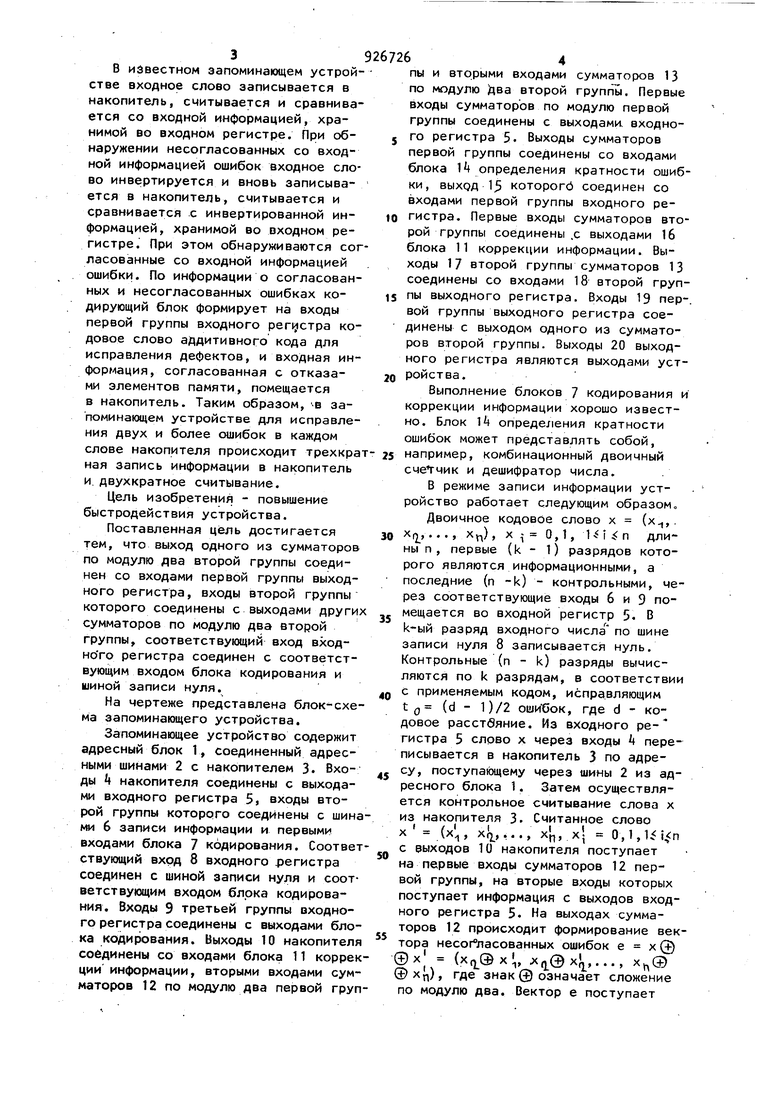

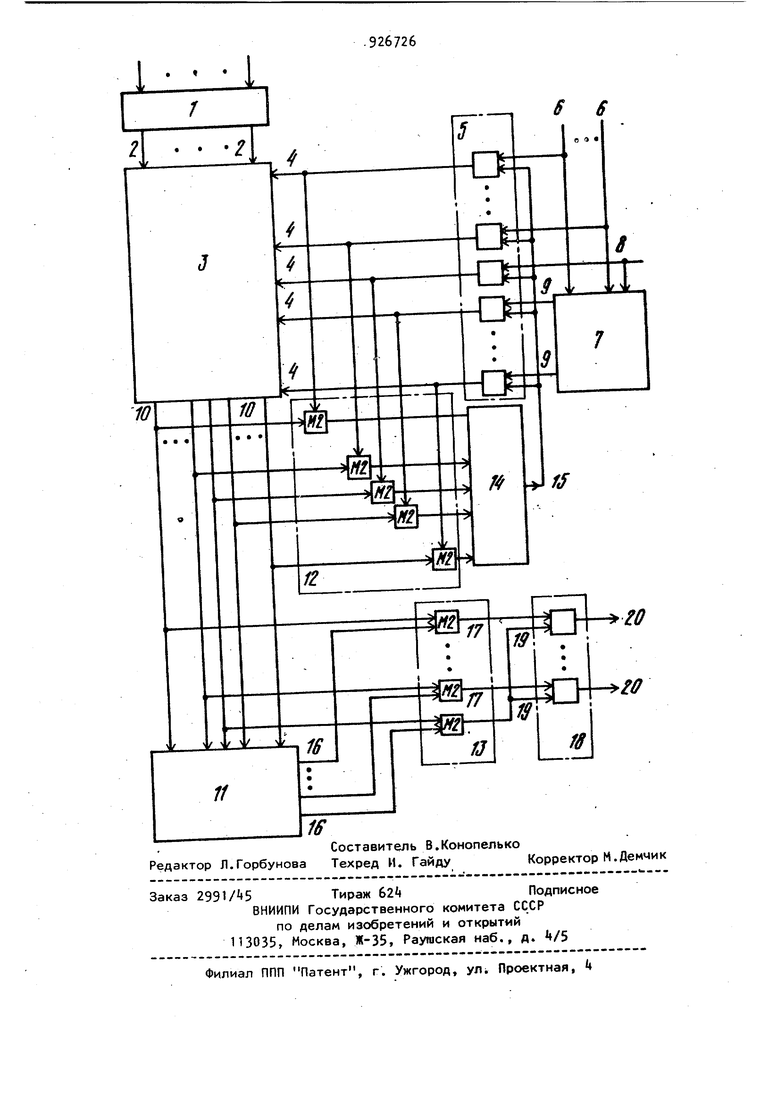

авт.онрмным контролем, содержащее накопитель, одни входы которого сое-: динены с выходами адресного блока, другие - с выходами входного регистра и первыми входами сумматоров по модулю два первой группы, вторые входы которых соединены с выходами накопителя и входами блока коррекции информации, выходы,которого соединены с первыми входами сумматоров по модулю два второй группы, вторые входы которых соединены с соответствующими выходами накопителя, выходы сумматоров по модулю два первой группы соединены со входами блока определения кратности ошибок, выходы которого соединены со входами первой группы входного регистра, входы второй группы которого соединены с Jlинaми записи информации и входами блока кодирования, а входы третьей группы входного регистра соединены с выходами блока кодирования, выходной регистр Г2}. в известном запоминающем устройстве входное слово записывается в накопитель, считывается и сравнивается со входной информацией, хранимой во входном регистре. При обнаружении несогласованных со входной информацией ошибок входное слово инвертируется и вновь записывается в накопитель, считывается и сравнивается с инвертированной информацией, хранимой во входном регистре. При этом обнаруживаются сог ласованные со входной информацией ошибки. По информации о согласованных и несогласованных ошибках кодирующий блок формирует на входы первой группы входного кодовое слово аддитивного кода для исправления дефектов, и входная информация, согласованная с отказами элементов памяти, помещается в накопитель. Таким образом, -в запоминающем устройстве для исправления двух и более ошибок в каждом слове накопителя происходит трехкра ная запись информации в накопитель и двухкратное считывание. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что выход одного из сумматоров по модулю два второй группы соединен со входами первой группы выходного регистра, входы второй группы которого соединены с выходами други сумматоров по модулю два второй группы, соответствующий вход входного регистра соединен с соответствующим входом блока кодирования и шиной записи нуля. На чертеже представлена блок-схе ма запоминающего устройства. Запоминающее устройство содержит адресный блок 1, соединенный адресными шинами 2 с накопителем 3. Входы накопителя соединены с выходами входного регистра 5 входы второй группы которого соединены с шин ми 6 записи информации и первыми входами блока 7 кодирования. Соотве ствующий вход 8 входного регистра соединен с шиной записи нуля и соот ветствующим входом блока кодирования. Входы 9 третьей группы входного регистра соединены с выходами бло ка кодирования. Выходы 10 накопител соединены со входами блока 11 корре ции информации, вторыми входами сум маторов 12 по модулю два первой гру пы и вторыми входами сумматоров 13 по модулю Мва второй группы. Первые входы сумматоров по модулю первой группы соединены с выходами, входного регистра 5. Выходы сумматоров первой группы соединены со входами блока определения кратности ошибки, выход 15 которогб соединен со входами первой группы входного регистра. Первые входы сумматоров второй группы соединены ,с выходами 16 блока 11 коррекции информации. Выходы 17 второй группы сумматоров 13 соединены со входами 18 второй группы выходного регистра. Входы 19 пер-, вой группы выходного регистра соединены с выходом одного из сумматоров второй группы. Выходы 20 выходного регистра являются выходами устройства. Выполнение блоков 7 кодирования и коррекции информации хорошо известно. Блок 14 определения кратности ошибок может представлять собой, например, комбинационный двоичный и дешифратор числа. В режиме записи информации устройство работает следующим образом. Двоичное кодовое слово х (х,. XQ, .. . , Худ), X ,- 0,1, КЧ п длины п, первые (k - 1) разрядов которого являются информационными, а последние (п -k) - контрольными, через соответствующие входы 6 и 9 помещается во входной регистр 5. В k-ый разряд входного числа по шине записи нуля 8 записывается нуль. Контрольные (п - k) разряды вычисляются по k разрядам, в соответствии с применяемым кодом, исправляющим t д (d - 1)/2 ошибок, где d - кодовое расстояние. Из входного ре- гистра 5 слово х через входы 4 переписывается в накопитель 3 по адресу, поступакщему через шины 2 из адресного блока 1. Затем осуществляется контрольное считывание слова х из накопителя 3. Считанное слово X (х,, XQ, ,. . , x|i, х- 0,1,1 с выходов 10 накопителя поступает на первые входы сумматоров 12 первой группы, на вторые входы которых поступает информация с выходов входного регистра 5. На выходах сумматоров 12 происходит формирование вектора несог ласованных ошибок е х @ х (х,®х,, xjj,... , ©xli), где знак ® означает сложение по модулю два. Вектор е поступает в блок }Ц определения кратности ошибок, где происходит определение числа несогласованных с входной информацией отказов в опрашиваемой ячейке. Если е О, цикл записи заканчивается. Если е О, в блоке f. определяется кратность несогласованных ошибок, т.е. число разрядов t, в которых информация, считанная с ячей ки, не совпадает с информацией, записанной в эту ячейку. Такие ошибки называются несогласованными, В этой же ячейке могут быть и согласо ванные отказы tr2, когда записываемая для хранения информация совпадает с состоянием отказавших ячеек. Обозначим через t t + tn общее число отказавших элементов памяти в опрашиваемой ячейке. При записи информации возможны два случая: J Г1 I t где - округление до целого числа в меньшую сторону. Например, при 1-5 -Ь . I В случа§ I Цикл записи заканчивается,так как код выбирается так,что может исправлять t „ ° бок. В случае К блок 1 вырабатывае единичный сигнал, который поступает на выходы 15 входного регистра 5. В результате в последнем оказывается кодовое слово Y , отличающееся от исходного кодового слова во всех компонентах (V называется инверсным кодовым словом). Факт инверсии обоз начается записью единичного сигнала в k-ый разряд входного регистра 5. Кодовое слово V помещается в накопитель 3 на место кодового слова х. Для того,чтобы слово Ч было кодовым, необходимо, чтобы используемый код с to (d - 1)/2 содержал слово, состоящее из одних единиц, или в порождакицей матрице линейного кода в приведенно-ступенчатом виде все столбцы имели нечетное число единиц). В результате инвертирования снова согласованные Ошибки становятся несогласованными и наоборот но число несогласованных ошибок мен 4-. т.е. возникает слу ше, чем чай 1 и применяемый код может ис-править это число ошибок. Таким образом, например, применяя код с d з можно исправить три ошибки, а кодом с d 7 - семь ошибок. В режиме считывания информации из ячейки накопителя 3 считываемая информация поступает на вход блока 11 коррекции информации и на вторые входы сумматоров 13 второй группы. Блок 11 вырабатывает кoppeктиf yюuvиe сигналы в соответствии с вычисленным и дешифрированным синдромом ошибок, которые, поступая на первые входы сумматоров 13 второй группы, производят исправление несогласованных ошибок. Если производится инверсия записываемого слова, то на входы 19 выходного регистра 18 поступает единичный сигнал,и на выходе 20 выходного регистра восстанавливается правильная входная информация. Поясним выше сказанное с использованием корректирующего кода с «(««З и исправлением пяти отказов в слове (t 5;. Возможные случаи появления пяти отказов.в ячейку (если количество отказов меньше пяти, то их коррекция производится аналогично одному иЗ нижеперечисленных случаев : а)все ошибки согласованные ( 5 т.е. состояния отказавших элементов памяти совпадают с записываемой информацией; б)все о|||ибки несогласованные (tn 5), состояния отказавших элементов п.амяти не совпадают с записываемой информацией;. в)одна ошибка согласованная, четыре несогласованные (t(j 1, t q ) . г)две ошибки согласованные, три несогласованные (tij 2, t 3); д)три ошибки согласованные, две несогласованные (t 3, 2); е)четыре ошибки согласованные, од Не несогласованная . ) Рассмотрим процесс хранения информации в каждом из случаев а - е. В случае Q информация, хранимая в отказавших элементах памяти, совпадает с состоянием этих элементов, и блок Il определения кратности ошибок не указывает на наличие ошибок в хранимом слове. В случае Б при контрольном считывании в режиме записи блок Il обнаруживает ошибки и по вектору ошибок 7 e устанавливает, что несогласованных ошибок больше, чем согласованных. На выходе блока И появляется единичный сигнал, который, поступив на выходы 15 входного регистра 5, инвертирует кодовое слово х в кодовое слово V , которое вновь помещается в нaкoпf1тeль. При этом несогласованные ошибки становятся согласованными. Считывание ин формации происходит аналогично, случаю О, но хранимая информация инвертируется на обратную на выходном регистре 18 единичным сигналом с k -го разряда. В случае ft запись информации осу ществляется так же, как и в б. При этом одна согласованная ошибка (t(j 1) становится несогласованной и при считывании происходит исправление этой ошибки сигналом с блока 11 на сумматорах 13 {код исправляет одиночные и двойные ошибки, так как d 5 с последующим инвертированием скорректированного слова сигна лом с выхода К-го разряда. В случае t процесс записи-считывания информации аналогичен случаю 6, но при считывании код с d 5 исправляет уже ошибку кратности два. В случае 3 процесс записи-считывания информации аналогичен случаю 1., но при записи и считывании не происходит инвертирования. В случае & процесс записи-считывания аналогичен случаю Э, но блок 11 коррекции информации корректирует одну несогласованную ошибку. , Таким образом, предлагаемое устройство выполняет те же функции, что и известное, но быст1эодействие предлагаемого устройства в режиме записи выше на рдин цикл записисчитывания. В предлагаемом устройстве требуется максимум два цикла записи и один цикл считывания в режиме записи информации, тогда как в известном устройстве необходимо три цикла записи и два цикла считыв ния в режиме записи. 8 .Формула изобретения Запоминающее устройство с автономным контролем, содержащее накопитель , одни входы которого соединены с выходами адресного блока, другиес выходами входного регистра и первыми входами сумматоров по модулю два первой группы, вторые входы которых соединены с выходами накопителя и входами блока коррекции информации, выходы которого соединены с первыми входами сумматоров по модулю два второй группы, вторые входы которых соединены с соответствующими выходами накопителя, выходы сумматоров по модулю два первой группы соединены со входами блока определения кратности ошибок, выходы которого соединены со входами первой группы входного регистра, входы второй группы которого соединены с шинами записи информации и входами блока кодирования, а входы третьей группы входного регистра соединены с выходами блока кодирования, выходной регистр, отличающее-, с я тем, что, с целью повышения быстродействия устройства, выход одного из сумматоров по модулю два второй группы соединен со входами первой группы выходного регистра, входы второй группы которого соединены с выходами других сумматоров ПО модулю два второй группы, соответствующий вход входного регистра соединен с соответствующим входом блока кодирования и шиной записи нуля. Источники информации, принятые во внимание при экспертизе 1. Самофалов К.Г. и др. Структур но-логические методы повышения надежности запоминающих устройств. М., Машиностроение,. 1976, с. 152. 2. Авторское свидетельство СССР ff 556501, кл. Q 11 С 29/00,1977 (прототип).

1

.926726

6

о о

On

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU972590A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Устройство для контроля записи и считывания информации | 1983 |

|

SU1095241A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

ч

e10

ч Iff

twt - t.

/cf

Ш

10

1S

Ob

19

Ы

Авторы

Даты

1982-05-07—Публикация

1980-05-20—Подача