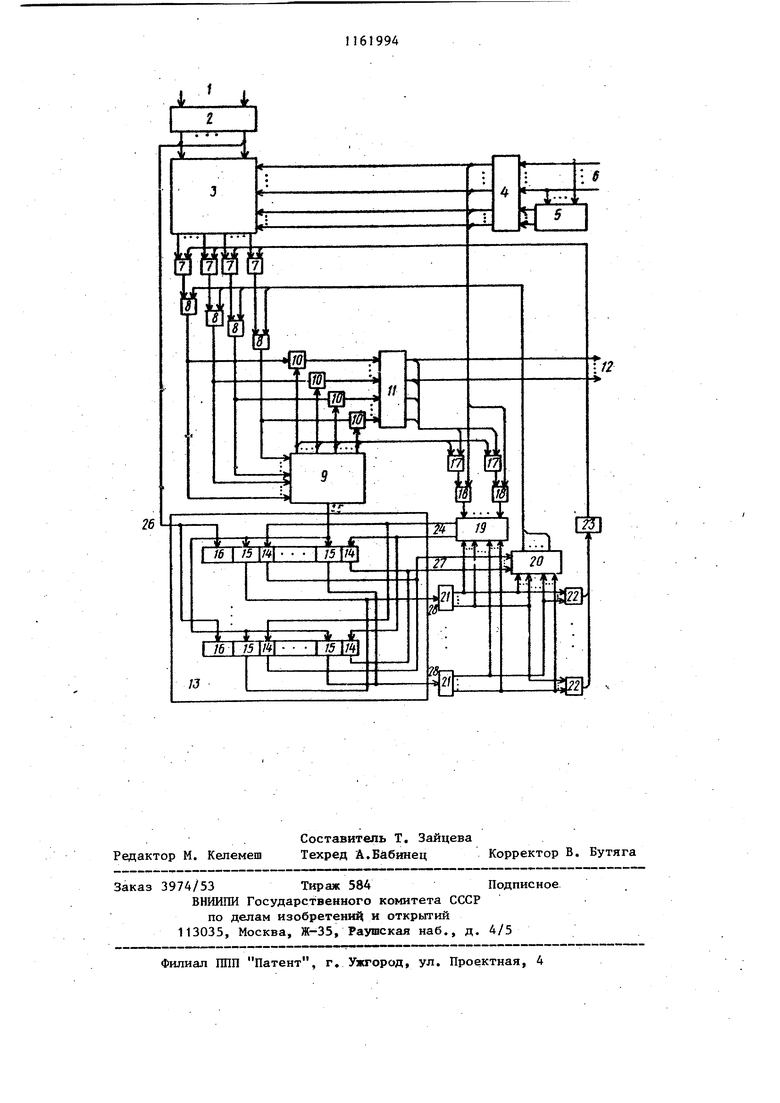

IП Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств на базе интегральных запоминающих устройств, Известно запоминающее устройство с автономным контролем, содержащее Накопитель, адресный блок, входной регистр, группы сумматоров по модулю два, блок коррекции информаиции, блок определения кратности ошибок, блок кодирования и выходной регистр lj . Недостатком такого устройства является его низкое быстродействие при возникновении двух и более ошибок в слове. Наиболее близким техническим решением к изобретению является запоминающее устройство с автономным контролем, содержащее накопитель, соединенный по входам с адресным блоком, выходами входного регистра и первыми входами сумматоров по модулю два первой группы, выходы накопителя подключены к входам блока кор рекции, вторым входам сумматоров по модулю два и первьм входам сумматоров по модулю два второй группы, вторые входы которых соединены с выходами блока коррекции, выходы сумматоров по модулю два первой груп пы соединены с входами блока определения кратности ошибок, вьосоды которого соединены с первой группой входов входного регистра, вторая группа вх „. дов которого подключена к шинам записи информации и входам блока кодирования, выходы которого соединены с третьей группой входов входного регистра, соответствующий вход которого соединен с соответствующим входом блока кодирования и ииной записи нуля, выходы сумматоров по модулю два соединены с входами выходного регистра L2J. Однако и данное устройство характеризуется низким быстродействием и недостаточной достоверностью контроля считываемой информации, так как в нем для исправления ошибок, кратность которых не превышает корректир ющую способность кода, требуется два цикла записи и один цикл считывания в режиме записи информации и один цикл считьшания в режиме считывания информации. 4 Цель изобретения - повьпиение достоверности контроля и быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее адресный накопитель, формирователь адресных сигналов, входной регистр. блок кодирования, блок коррекции, сумматоры по модулю два и выходной регистр, причем одни из входов адресного накопителя соединены с выходами формирователя адресных сигналов, а другие входы - с вьЬсодами входного регистра, одни из входов которого подключены к выходам блока кодированияJ первые и вторые входы сумматоров по модулю два соединены соответственно с входами и с одними из выходов блока коррекции, а выходы - с входами выходного регистра, одни из выходов которого являются выходами устройства, другие входы входного регистра соединены с входами блока кодирования и являются информационными входами устройства, введены ассоциативный накопитель, группы элементов И, группы элементов ИЛИ, коммутаторы, дешифраторы и элементы НЕ, причем первые входы элементов ИЛИ первой группы соединены с выходами элементов И первой группы, первые входы которых подключены к выходам элементов НЕ, а вторые входы - к выходам адресного накопителя, выходы элементов ИЛИ первой группы соединены с входами блока коррекции, одни из входов ассоциативного накопителя подключены соответственно к другим выходам блока коррекции и к выходам первого коммутатора, входы которого соединены с выходами элементов ИЛИ второй группы, первые входы которых подключены к выходам входного регистра, а вторые входы - к -выходам элементов И второй группы, первые входы которых соединены с другими выходами выходного регистра, а вторые входы - с одними из выходов блока коррекции, вторые входы элементов ИЛИ первой группы подключены к выходам второго коммутатора, входы которого соединены с одними из выходов ассоциативного накопителя, другие входы и выходы которого подключены соответственно к выходам формирователя адресных сигналов и к входам дешифраторов, выходы которых соединены с управляющими входами первого и второго коммутаторов и входами элементов ИЛИ третьей группы, выходы которых подключены к входам элементов НЕ. На чертеже представлена функциональная схема предложенного устрой ства. Устройство содержит адресные входы 1, формирователь 2 адресных сигналов, адресный накопитель 3, вх ной регистр 4, блок 5 кодирования. На чертеже обозначены информационны входы 6 устройства. Устройство содержит также первую группу элементов И 7, первую группу элементов ИЛИ 8, блок 9 коррекции, группу сумматоров 10 по модулю два, выходной регистр 11 с выходами 12, ассоциативный накопитель 13, содерж щий функциональную часть 14 для раз мещения содержимого отказавших разрядов, признаковую часть 15 для хра нения номеров отказавших разрядов и аргументную часть 16 для запоминания адресов отказавших ячеек нако пителя 3, вторую группу элементов И 17, вторую группу элементов ИЛИ 1 пр.рвьм 19 и второй 20 коммутаторы, дешифраторы 21, третью группу элементов ИЛИ 22, элементы НЕ 23. На чертеже обозначены входы 24, 25, 26 и выходы 27 и 28 ассоциативного накопителя 13. Предложенное устройство работает следующим образом. Двоичное кодовое слово, содержащее п. разрядов, принимается в регистр 4. При этом k разрядов из п (где k : п) являются информационным Они поступают по входам 6 как в регистр 4, так и на блок 5, с которого n-k контрольных разрядов подаютс в регистр 4. Принятое кодовое слово записывается в накопитель 3 по адре су, поступившему по входам 1 через формирователь 2. В режиме считывания информации при отсутствии ошибок на выходах бл ка 9 нули, следовательно, и в признаковых частях 15 накопителя 13 . также нули. Это приводит к нулевым сигналам на всех входах дешифраторов 21, а значит, и на всех п. выходах каждого из дешифраторов 21. Сле довательно, коммутаторы 19 и 20 заперты, а на выходе элементов НЕ 23 единичные сигналы. Cчитaннot из накопителя 3 кодовое слово через открытые элементы И 7, элементы ИЛИ В без подмены разрядов поступает на входы блоке 9 и на первые входы Сумматоров 10. В силу отсутствия опгабок блок 9 формрфует нулевые сигналы на одних из выходов, которые обеспечивают передачу всех разрядов кодового слова через сумматоры 10 без изменения для приема его в регистр 11, из которого информационные разряды выдаются на выходах 12 устройства. При обнаружении первой ошибки i-ro разряда в режиме считывания по какому-либо адресу на i-м выходе одних из выходов блока 9 сформирована единица, поступающая на второй вход i-ro сумматора 10, где происходит исправление i-ro разряда слова перед приемом его в регистр 11. Единица из блока 9 поступает также на второй вход i-ro элемента И 17. На других выходах блока 9 будет сформирован код номера отказавшего разряда, поступающий на входы частей 15 накопителя 13. С формирователя 2 на входы частей 16 накопителя 13 подается код адреса ячейки, в которой обнаружена ошибка. Адрес ячейки и номер отказавшего разряда записывается в часть 16 и часть 15 Соответственно первой ячейки накопителя 13. Код номера i-rb разряда поступает на первый из дешифраторов 21, на i-M выходе которого формируется единичный сигнал, подаваемый на управляющий вход коммутатора 19. Правильное значение i-ro разряда с регистра 11 через i-й элемент И 17 подается на второй вход i-ro элемента ЖМ 18, на первом входе которого нуль, поступающий с регистра 4. С i-ro элемента РШИ 18 значение i-ro разряда поступает на коммутатор 19, затем через его выход поается на первый из входов 24 накопителя 13, где это значение запомиается в части 14 первой ячейки. При повторном обращении к накопиелю 3 по данному адресу с целью читывания.слова происходит обращеие и к первой ячейке накопит еля 13. его части 15 и части 1Д считываютя код номера i-ro разряда и правильое значение информации i-ro разряда оответственно. Код номера разряда ерез соответствующие выходы 28 по5ступает на первый из дешифраторов 21, на его i-м выходе формируется единичный сигнал, подаваемьй на управляющий вход коммутатора 20 и на вход i-ro элемента ИЛИ 22. Нулевой сигнал с выхода i-ro элемента НЕ 23 группы закроет i-й элемент И 7, чем запрещается прохождение неправильного значения i-ro разряда с накопителя 3. Правильное значение i-ro разряда через первый из выходов 27 накопителя 13 и коммутатор 20 поступает на i-й элемент ИЛИ 8, где подменяет неправильное значение i-ro разряда, считанного с накопителя 3. На регистр 11 и блок 9 при этом подается правильное значение кодового слова. Если в цикле записи потребуется запись новой информации по данному адресу, то в части 14 первой ячейки накопителя 13 будет запомнено перво начальное значение i-ro разряда. Пр изводится это следующим образом. Значение 1-го разряда с выхода ре гистра А подается на первый вход i-го элемента ИЛИ 18, на втором вхо.де которого нуль, так как при этом с регистра 11 поступают нули, С элемента ИЛИ 18 значение i-ro разряда, как показано выше, через коммутатор 19 поступает в накопитель 13, Если возникла новая ошибка в другом разряде в результате чтения информации из накопителя 3 по адресу. 4« по которому ранее бьша обнаружена ошибка, данные о которой зафиксированы в накопителе 13, то новая ошибка будет обнаружена и исправлена рассмотренным способом, В следующие часть 16 и часть 14 ячейки накопителя 13 в части 16 которой записан рассматриваемый адрес ячейки накопителя 3, будет занесен соответственно номер и правильное значение очередного отказавшего разряда. При повторном обращении к накопителю 3 по данному адресу и считываемой информации будут применяться уже значения двух отказавших разрядов. Аналогичным образом, в предлагаемом устройстве могут корректироваться ошибки большей кратности, Тлким образом, в предложенном устройстве применяется ассоциативный накопитель дпя коррекции ошибок большой кратности, что повьш1ает достоверность контроля накопителя. Причем запись информации производится за один .цикл записи, а считывание за один цикл считывания, -ч результате чего быстродействие устройства повышается в 3 раза по сравнению с прототипом при записи информации и наличия ошибки, Технико-экономическое преимущество предложенного устройства заключается в более высокой достоверности контроля и более высоком быстродействии по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

ЗАПОМИНАКЯЦЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее адресный накопитель, формирователь адресных сигналов, входной регистр, блок кодирования, блок коррекции, сумматоры по модулю два и выходной регистр, причем одни из входов адресного накопителя соединены с выходами формирователя адресных сигналов, а другие входы - с выходами входного регистра, одни из входов которого подключены к выходам блока кодирования, первые и вторые входы сумматоров по модулю два соединены содтветственно с входами и с одними из выходов блока коррекции, а выходы - с входами выходного регистра, одни из выходов которого являются выходами устройства, другие входы входного регистра соединены с входами блока кодирования и являются информационными входами устройства, отличающееся тем, что, с целью повышения достоверности контроля и быстродействия . устройства, в неро введены ассоциативный накопитель, группы элементов И, группы элементов ИЛИ, коммутаторы, дешифраторы и элементы НЕ, причем первые входы элементов ИЛИ первой группы соединены с выходами элементов И первой группы, первые входы которых подключены к выходам элементов НЕ, а вторые входы - к выходам адресного накопителя, выходы элементов ИЛИ первой группы соединены с входами блока коррекции, одни из входов ассоциативного накопителя подключены соответственно к другим выходам блока коррекции и к выходам первого коммутатора, входы которого соединены с выходами элементов ИЛИ второй группы, первые входы которых (Л подключены к выходам входного регистра, а вторые входы - к выходам элементов И второй группы, первые входы которых соединены с другими выходами выходного регистра, а вторые входы - с одними из выходов блока коррекции, вторые входы элементов ИЛИ первой группы подключены к выхоОд дам второго коммутатора, вхгды которого соединены с одними из выходов 00 ассоциативного накопителя, другие входы и выходы которого подключены соответственно к выходам формирователя адресных сигналов и к входам дешифраторов, выходы которых соединены с управляющими входами первого и второго коммутаторов и входам элементов ИЛИ третьей группы, выходы которых подключены к входам элементов НЕ.

ri

.

I /6 I I /5i/4j

/J

2/r

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1975 |

|

SU556501A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-15—Публикация

1984-01-04—Подача