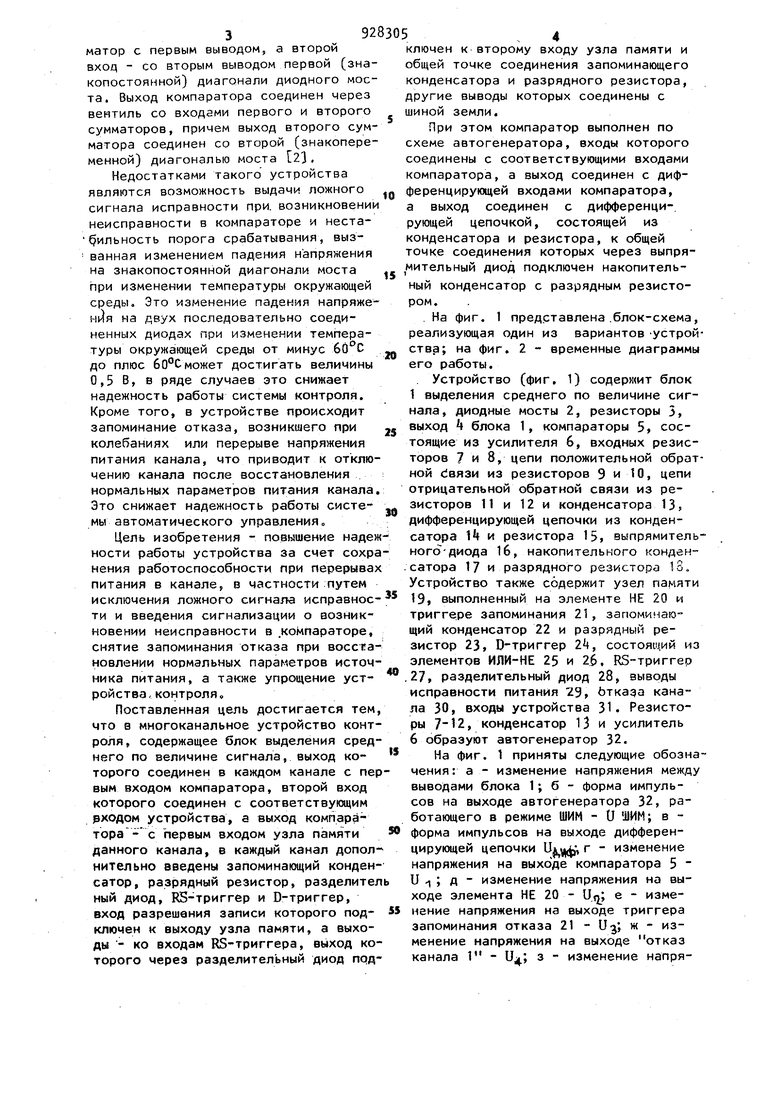

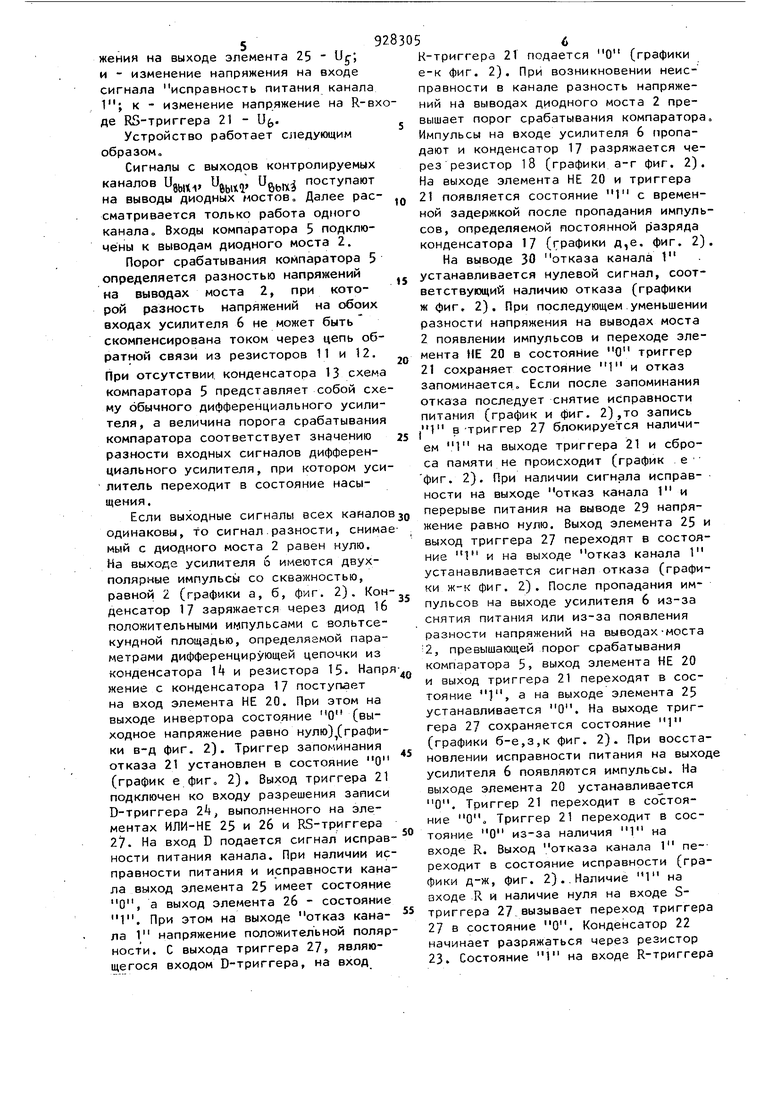

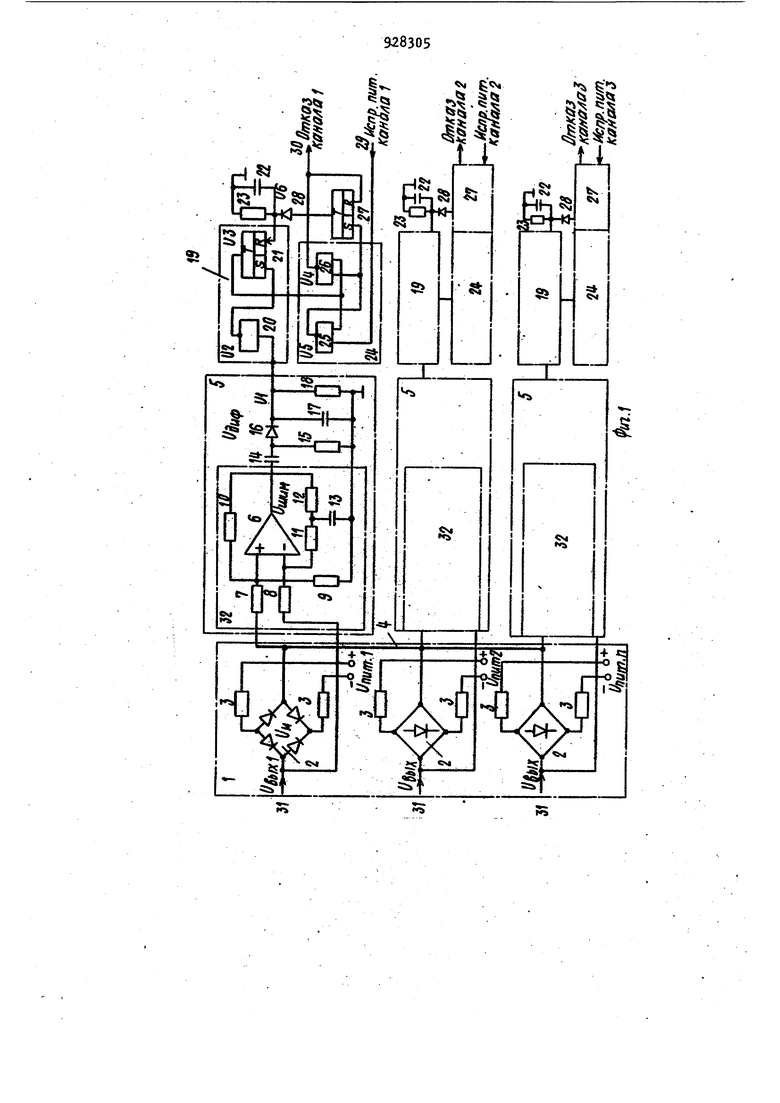

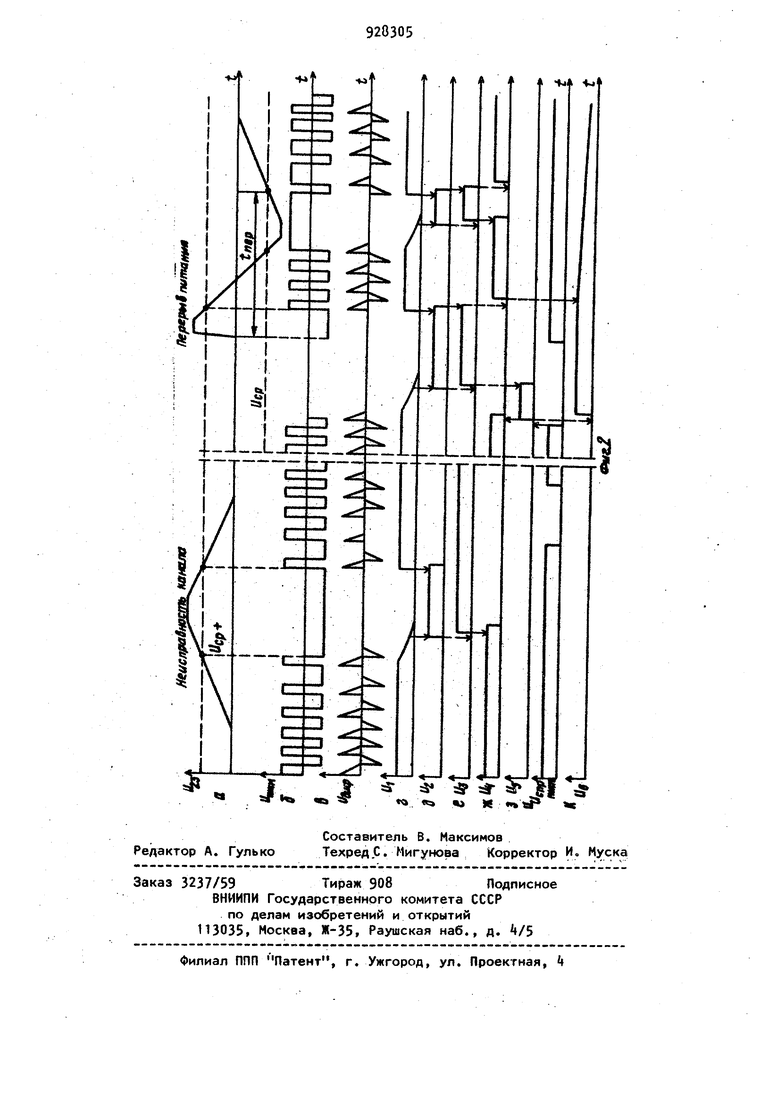

Изобретение относится к приборостроению и автоматике и может быть использовано при построении систем автоматического управления повышенной Надежности. В системах автоматического управления с многоканальным резервированием и непрерывным контро лем исправности каждого из каналов применяются устройства для выделения среднего по величине сигнала, по принципу мажоритарной логики, так на зываемые кворум-элементы. Известно устройство, содержащее узел выбора среднего значения сигнала, так называемый кворум-элемент и компараторы, т.е. релейные сравнивающие устройства. Выходы контролиру мых каналов подключены ко входам кворум-элемента. Один вход компаратора подключен к выходу кворум-элемента, а второй вход компаратора - к выходу контролируемого канала. Сигна с выхода канала и сигнал с выхода кворум-элемента поступают на релейно сравнивающее устройство, которое при определенной абсолютной в ёличине разности входных сигналов выдает сигнал отказа. Для обеспечения правильного функционирования такой системы необходимо запоминание отказа и исключение влияния отказавшего канала на работу резервированной системы 1. Недостатками этого устройства являются запоминание отказа при перерыве питания или колебаниях напряжения источника питания и сохранение сигнала отказа при восстановлении нормальных параметров питания контролируемого канала. Наиболее близким к изобретению является устройство выбора непрерывного сигнала по принципу большинства, содержащее один общий блок выделения среднего по величине сигнала, выполненный на диодных мостах, и в каждом контролируемом канале два сумматора, вентиль и компаратор, Первый вход компаратора соединен через сум- матор с первым выводом, а второй вход - со вторым выводом первой (знакопостоянной) диагонали диодного моста. Выход компаратора соединен через вентиль со входами первого и второго сумматоров, причем выход второго сумматора соединен со второй (знакопеременной) диагональю моста 21, Недостатками такого устройства являются возможность выдачи ложного сигнала исправности при. возникновении неисправности в компараторе и неста ильность порога срабатывания, вызванная изменением падения напряжения на знакопостоянной диагонали моста при изменении температуры окружающей среды. Это изменение падения напряжеН11я на двух последовательно соединенных диодах при изменении температуры окружающей среды от минус до плюс бО Сможет достигать величины 0,5 В, в ряде случаев это снижает надежность работы системы контроля. Кроме того, в устройстве происходит запоминание отказа, возникшего при колебаниях или перерыве напряжения питания канала, что приводит к отключению канала после восстановления нормальных параметров питания канала Это снижает надежность работы системы автоматического управления,, Цель изобретения - повышение надеж ности работы устройства за счет сохра нения работоспособности при перерывах питания в канале, в частности путем исключения ложного сигнала исправное ти и введения сигнализации о возникновении неисправности в .компараторе, снятие запоминания отказа при весегановлении нормальных параметров источника питания, а также упрощение устроиства,контроля. Поставленная цель достигается тем, что в многоканальное устройство контро я, содержащее блок выделения среднего по величине сигнала, выход которого соединен в каждом канале с пер вым входом компаратора, второй вход которого соединен с соответствующим эходом устройства, а выход компаратора- с первым входом узла памяти данного канала, в каждый канал дополнительно введены запоминащий конденсатор, разрядный резистор, разделител ный диод, RS-триггер и D-триггер, вход разрешения записи которого подключей к выходу узла памяти, а выходы - ко входам RS-триггера, выход которого через разделительный диод под92 4 ключен к второму входу узла памяти и общей точке соединения запоминающего конденсатора и разрядного резистора, другие выводы которых соединены с шиной земли. При этом компаратор выполнен по схеме автогенератора, входы которого соединены с соответствующими входами компаратора, а выход соединен с дифференцирующей входами компаратора, а выход соединен с дифференцирующей цепочкой, состоящей из конденсатора и резистора, к общей точке соединения которых через выпрямительный диод подключен накопительный конденсатор с разрядным резистором. На фиг. 1 представлена .блок-схема, реализующая один из вариантов устройства; на фиг. 2 - временные диаграммы его работы. . Устройство (фиг. 1) содержит блок 1 выделения среднего по величине сигнала, диодные мосты 2, резисторы 3, выход k блока 1, компараторы 5, состоящие из усилителя 6, входных резисторов 7 и 8, цепи положительной обратной из резисторов 9 и 10, цепи отрицательной обратной связи из резисторов 11 и 12 и конденсатора 13 дифференцирующей цепочки из конденсатора ft и резистора 15, выпрямительного диода 16, накопительного конденсатора 17 и разрядного резистора 13. Устройство также содержит узел памяти 19. выполненный на элементе НЕ 20 и триггере запоминания 21, запоминающий конденсатор 22 и разрядный резистор 23, 0 триггер , состоящий из элементов ИЛИ-НЕ 25 и 26. RS-триггер 27, разделительный диод 28, выводы исправности питания 29, Ъткада канала 30, входы устройства 31. Резисторы , конденсатор 13 и усилитель 6 образуют автогенератор 32. На фиг. 1 приняты следующие обозначения: а - изменение напряжения между выводами блока 1; б - форма импульсов на выходе автогенератора 32, работающего в режиме ШИМ - О ШИМ; в форма импульсов на выходе дифференцирующей цепочки изменение напряжения на выходе компаратора 5 и -1 ; д - изменение напряжения на выходе элемента НЕ 20 - е - изменение напряжения на выходе триггера запоминания отказа 21 - ж - изменение напряжения на выходе отказ канала 1 - з - изменение напряженин на выходе элемента 25 - Ur, и - изменение напряжения на входе сигнала исправность питания канала к - изменение напряжение на R-BX де RS-триггера 21 - U, Устройство работает следующим образом. Сигналы с выходов контролируемых каналов М, U поступают на выводы диодных мостов. Далее рассматривается только работа одного канала Входы компаратора 5 подключены к выводам диодного моста 2. Порог срабатывания компаратора 5 определяется разностью напряжений на выврдах моста 2, при которой разность напряжений на обоих входах усилителя 6 не может быть скомпенсирована током через цепь обратной связи из резисторов 11 и 12. При отсутствии конденсатора 13 схема компаратора 5 представляет собой схе му обычного дифференциального усилителя, а величина порога срабатывания компаратора соответствует значению разности входных сигналов дифференциального усилителя, при котором уси литель переходит в состояние насыщения. Если выходные сигналы всех канало одинаковы, то сигнал разности, снима мый с диодного моста 2 равен нулю. На выходе усилителя 6 имеются двухполярные импульсы со скважностью, равной 2 (графики а, б, фиг. 2). Кон денсатор 17 заряжается через диод 16 положительными и ilпyльcaми с вольтсекундной площадью, определяемой параметрами дифференцирующей цепочки из конденсатора It и резистора 15- Напр жение с конденсатора 17 поступает на вход элемента НЕ 20. При этом на выходе инвертора состояние О (выходное напряжение равно нулю)(графики в-д фиг. 2). Триггер запоминания отказа 21 установлен в состояние О (график е фиг 2), Выход триггера 21 подключен ко входу разрешения записи D-триггера 2, выполненного на элементах ИЛИ-НЕ 25 и 26 и RS-триггера 27. На вход D подается сигнал исправ ности питания канала. При наличии ис правности питания и исправности кана ла выход элемента 25 имеет состояние О, а выход элемента 26 состояние1. При этом на выходе отказ кана ла 1 напряжение положительной поляр ности. С выхода триггера 27, являющегося входом D-триггера, на вход 9 56 Н-триггера 21 подается О (графики е-к фиг. 2). При возникновении неисправности в канале разность напряжений на выводах диодного моста 2 превышает порог срабатывания компаратора. Импульсы на входе усилителя 6 пропадают и конденсатор 17 разряжается через резистор 18 (графики а-г фиг. 2). На выходе элемента НЕ 20 и триггера 21 появляется состояние 1 с временной задержкой после пропадания импульсов, определяемой постоянной разряда конденсатора 17 (графики д,е. фиг. 2). На выводе 30 отказа канала 1 устанавливается нулевой сигнал, соответствующий наличию отказа (графики ж фиг. 2). При последующем.уменьшении разности напряжения на выводах моста 2 появлении импульсов и переходе элемента НЕ 20 в состояние О триггер 21 сохраняет состояние 1 и отказ запоминается. Если после запоминания отказа последует снятие исправности питания (график и фиг. 2),то запись в-триггер 27 блокируется наличием 1 на выходе триггера 21 и сброса памяти не происходит (график е фиг. 2). При наличии сигнала исправности на выходе отказ канала 1 и перерыве питания на выводе 29 напряжение равно нулю. Выход элемента 25 и выход триггера 27 переходят в состояние 1 и на выходе отказ канала 1 устанавливается сигнал отказа (графики ж-к фиг. 2). После пропадания импульсов на выходе усилителя 6 из-за снятия питания или из-за появления разности напряжений на выводах-моста 2, превышающей порог срабатывания компаратора 5, выход элемента НЕ 20 и выход триггера 21 переходят в состояние 1, а элемента 25 на выходе устанавливается О. На выходе три)- гера 27 сохраняется состояние 1 (графики б-е,з,к фиг. 2). При восстановлении исправности питания на выходе усилителя 6 появляются импульсы. На выходе элемента 20 устанавливается О. Триггер 21 переходит в соЪтояние Триггер 21 переходит в состояние О из-за наличия 1 на входе R. Выход отказа канала 1 переходит в состояние исправности (графики д-ж, фиг. 2)..Наличие 1 на входе R и наличие нуля на входе Sтриггера 27 вызывает переход триггера 27 в состояние О. Конденсатор 22 начинает разряжаться через резистор 23. Состояние 1 на входе R-триггера 21 сохраняется в течение времени, определяемого постоянной времени раз ряди конденсатора 22. Запоминание 1 на входе R-триггера 21 после перехода элемента 26 в состояние 1 необходимо для восстановления сигнала исправности канала после пов торного отказа, возникающего из-за переходных процессов в контролируемом канале в течение t „(график а фиг. 2).при включении питания канала При возникновении неисправности (про бой, обрыв какого-либо элемента схемы) компаратора 5 автогейерацйя срывается и напряжение на конденсаторе 17 равно нулю. На выходе отказ канала 1 появляется сигнал отказа. Узел памяти 19 и D-триггер 2 выполнены на микросхемах с униполярным МОП-транзисторами. Питание узла памяти 19 и D-триггера 2k производится от отдельного источника питания повы шенной надежности (аккумуляторная батарея). Данное устройство значительно надежнее известных устройств. формула изобретения 2. Многоканальное устройство конт роля, содержащее блок выделения среднего по величине сигнала, выход которого соединен в каждом канале с первым входом компаратора, второй вход которого соединен с соответствующим входом устройства, а выход компаратора - с первым входом узла памяти данного канала, отличаю щ е е с я тем, что, с целью повышения надежности работы устройства за счет сохранения работоспособности при перерывах питания в канале, в каждый канал дополнительно введены запоминающий конденсатор, разрядный резистор, разделительный диод, RSтриггер и D-триггер, вход разрешения записи которого подключен к выходу узла памяти, а выходы - ко входам RS-триггера, выход которого через разделительный диод подключен к второму входу узла памяти и общей точке соединения запоминающего конденсатора и разрядного резистора, другие выводы которых соединены с шиной земли. 2. Устройство по п.1, о т л и чающееся тем, что компаратор выполнен по схеме автогенератора, входы которого соединены с соответствующими входами компаратора, а выход соединен с дифференцирующей цепочкой, состоящей из конденсатора и резистора, к общей точке соединения которых через выпрямительный диод подключен накопительный конденсатор с разрядным резистором. Источники информации, принятые во внимание при экспертизе 1.Белгородский С.Л. Автоматизация управления посадкой самолета. М,, Транспорт, 1972, с. 286-289. 2.Авторское свидетельство СССР № 623206, клс Н 03 К 19Л2, 1978 (прототип).

ll

K

«M R«N

s.n

IIS

tl If

i-i

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное резервированное аналоговое устройство | 1980 |

|

SU984089A2 |

| Устройство выбора непрерывного сигнала по принципу большинства | 1984 |

|

SU1193800A2 |

| Устройство выбора непрерывного сигнала по принципу "большинства | 1982 |

|

SU1051722A1 |

| Устройство для контроля и сигнализации высоты полета самолета | 1990 |

|

SU1817125A1 |

| Устройство для допускового контроля напряжений | 1981 |

|

SU1091124A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Реле времени | 1981 |

|

SU1111213A1 |

| Трехканальное мажоритарное устройство | 1980 |

|

SU924931A1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГУЛИРОВАНИЯ ДВИЖЕНИЯ ЖЕЛЕЗНОДОРОЖНЫХ ТРАНСПОРТНЫХ СРЕДСТВ | 2004 |

|

RU2286279C2 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

Авторы

Даты

1982-05-15—Публикация

1980-02-22—Подача