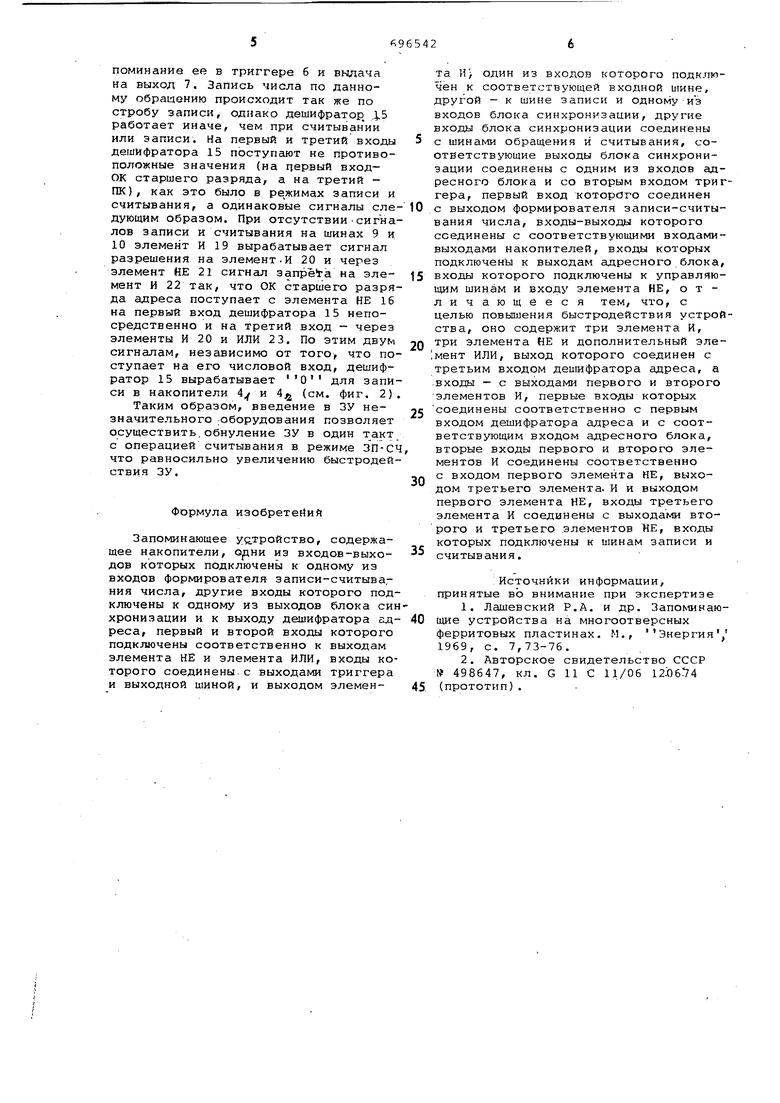

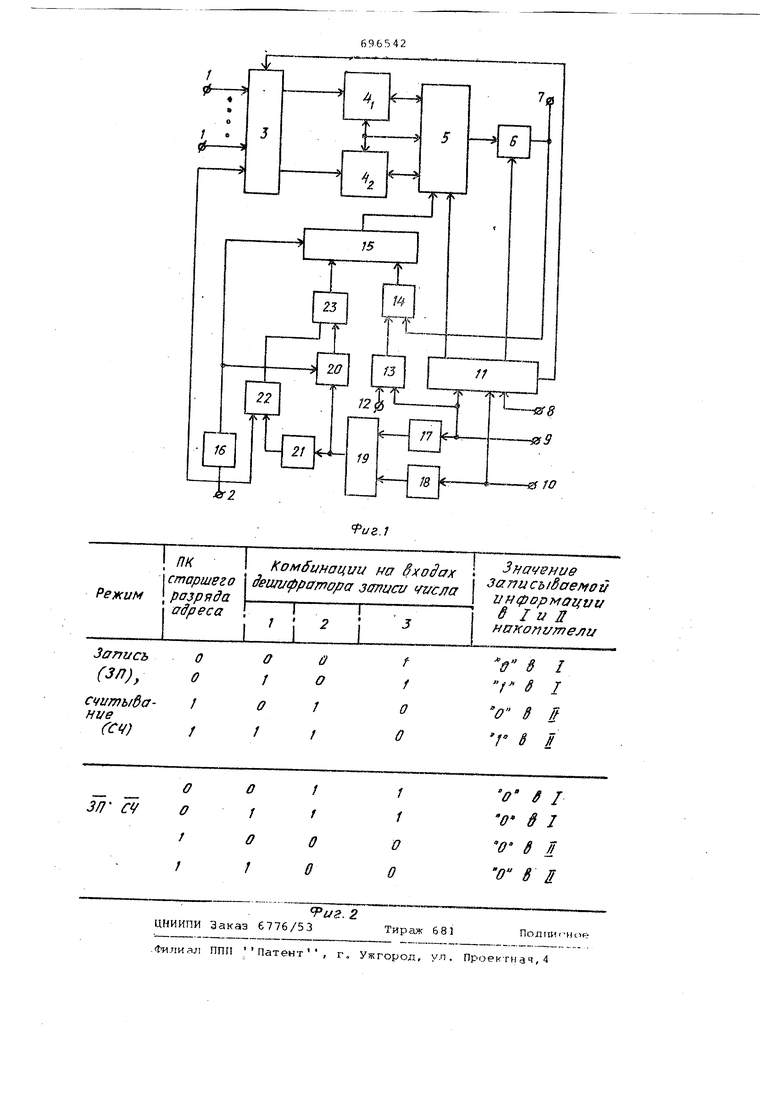

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам (ЗУ) с на копителями, выполненными на многоотверстных ферритовых пластинах. Известно запоминающеЪ устройство (ЗУ), сЬдержащее накопители, адресны блок, блок синхронизации, блок выделения информации, блок записи информации,: при этом накопители и усили-тали записи-считывания включены по мостовой схеме с целью к тенсации помех от записи, запись водится в разные накопители импульса ми противоположной полярности 1. Наиболее близким техническим реше нием к даннся«1У изобретению является запоминающее устройство, содержащее накопители, одни из входов-выходов которых по.цключены к одному из входов формирователя записи-считывания числа, .ЦРУгие входы которого подключены к одному из выходов блока синхр низации и к выходу дешифратора а.цреса, первый и второй Входы которого по.цключены соответственно к выходам элемента dE и элемента ИЛИ, входы которого соединены с выходами триггера и выходной шиной, и выходом эле мента И, один из входов которого под ПрОИ 3ключен к соответствующей входной шине, другой - к шине записи и одному из входов блока синхронизации, другие ВХО.ЦЫ блока синхронизации Соединены с шинами обращения и считывания, соответствующие выходы блока синхронизации соединены с одним из входов адресного блока и со вторым входом триггера, первый вход которого соединен с выходом формирователя записисчитывания числа, ВХОДЫ-ВЫХО.ЦЫ которого соединены с соответствующими входами-выхедами накопителей, входы которых подключены к выходам адресного блока, входы которого подключены к управляющим шинам и входу элемента НЕ 2 . Недостатком известных устройств является то, что в Них при считывани информации происходит регенерация той информации, которая считывается. Иногда, например, при применении ЗУ в устройствах регистрации, необходимо после считывания информации производить обнуление ЗУ. в известных устройствах обнуление производится в цикле записи, что снижает быстродействие ЗУ. Цель изобретения - повышение быстроцействия ЗУ. Поставленная цель достигается тем что запомниаю.чее устройство соидержит три элемента И, три элемента ЙЕ и дополнительный элемент ИЛИ, выход которого соединен с третьим входом дешифратора адреса, а входы - с выходами первого и второго элементов И первые входы которых соединены соответственно с первым входом дешифратора адреса II с соответствую1(им входом адресного блока, вторые входы первого и второго элементов И соединены соответственно с входом первого элемента НЕ, выходом .третьего элемен та И , и выходом первого элеме.нта НЕ входы третьего элемента И соединены .выходами второго и третьего элементо НЕ, входы которых,подключены к шинам записи и считывания. На фиг. 1 представлена Блок-схема запоминающего устройства для одного разряда числа на фиг. 2 показа ю значение записываемой информации, по лучаемся на вьлходы дешифратора записи числа, в Зависимости от кодовых комбинаций числа в различных режимах работы ЗУ. Запоминающее устройство содержит управляющие шины 1,2, подключенные к адресному блоку 3, выходы которого соединены с входшми накопителей 4, 4г, формирователь 5 записи-считывани числа соединен по мостовой схеме с накопителями 4, 4, выход формирователя записи-считывания 5 подключен к первому входу триггера б регистра числа, выход которого соединен с выходной шиной 7 числа. Чина обращения 8, шина записи 9, шина считывания 10 подключены к блоку синхронизации 11, выходы которого соединены с входом блока выделения адреса 3, с управляющим выходом формирователя 5 записи-считывания числа и со вторым входом триггера 6. Шина записи 9 и вход ная шина числа 12 через элемент И 13 а выходная шина 7 непосредственно подключены к входам элемента ИЛИ 14. Выход элемента ИЛИ 14 соединен с первым входом де11ифратора адреса 15, первый вход которого соединен с выходом элемента НЕ 16 и через него с управляющей шиной 2, Шина записи 9 подключена к входу элемента НЕ 17, шина считывания 10 - к входу элемента НЕ 18. Выходы элементов НЕ 17, 18 подключены к входам элемента И 19, выход которого соединен с входом элементов И 20 и входом элемента НЕ 21. Один из входов элемента И 20 подключён к первому входу дешифратора записи числа 15 и выходу элемента НЕ 16. Выход элемента НЕ 21, вход элемента НЕ 16 иуправляющая шина 2 подк.лючены к входам элемента И 22. Выходы элементов И 20 и 22 соединены с входами дополнительного элемента ИЛИ 23,-выход которого подключен к третьему входу дешифратора 15. В pemiMe считывания информации по шинам 1-й 2 в блок 3 поступает адрес, При этом, если старший разряд адреса имеет значение .О , то выбирается ячейка накопителен 4 (см.фиг.2), если значение1 - то ячейка накопителя 4jj, в режиме считывания на входы ЗУ кроме адреса по.ступает признак считывания по шине 10 и обращение по шине 8. По итне записи 9 элемент И 19 закрыт и сигналом с элемента НЕ 21 открыт элемент И 22. Старший разряд адреса поступает в виде прямого кода (ПК) через элемент И 22, далее через элемент ИЛИ 23 на третий вход дешифратора 15 записи числа, йа первый вход которого поступает обратный код (ОК) старшего разряда адреса с выхода элемента НЕ 16. Блок синхронизации. 11 вырабатывает строб для блока 3, импульсы сброса и приема в регистр числа, а так же строб записи для регенерации. По переднему фронту строба ДШ про- . изводится считывание информации из 4 или 42 накопителя, формирование ее до необходимого уровня в формирователе 5 записи-считывания и прием в триггер 6 числа. Число с триггера 6 поступает па выход по шине 7. и через элемент ИЛИ 14 на дешифратор 15 записи числа, который в зaвиcи ocти от значения информации, старшего разряда адреса, формирует число в соответствии с таблицей (см. фиг.2). -По стробу записи, поступающему на управляющий вход формирователя 5, формируется разрядный ток соотв-етствующего накопителя, который либо складывается с током от выборки адреса по заднему фронту стробов ДШ либо выи тогда записывается читается, из него и тогда записывается О . Это происходит с рабочим сердечником накопителя. В компенсационном сердечнике (на хранение одного бита информации используется 2 сердечника) происходит обратное: при сложении токов происходит запись О и при вычитании-запись j1. В реушме записи число в триггер регистра 6 не принимается и. поступает на дешифратор 15,. извне с элемента И 13 по другому входу элемен-. та ИЛИ 14. Дешифратор 15 работает при этом как в режиме считывания (см. фиг. 2). В режиме считывания без регенерации (режим ЗПСЧ) в ЗУ поступает сигнал по шинам 1, 2 и 8, Блок синхронизации 11 вырабатывает сигналы, как и в режиме считывания. Так же по переднему Фронту строба Л1) происходит считывание информации, эапоминание ее в триггере 6 и выдача на выход 7. Запись числа по данному обращению происходит так же по стробу записи, однако дешифратор, .1.5 работает иначе, чем при считывании или записи. На первый и третий входы дешифратора 15 поступают не противоположные значения (на цервый входОК старшего разряда, а на третий ПК), как это было в режимах записи и считывания, а одинаковые сигналы сле дующим образом. При отсутствииСигналов записи и считывания на шинах 9 и 10 элемент И 19 вырабатывает сигнал разрешения на элемент-И 20 и через элемент НЕ 21 сигнал запрета на элемент И 22 так, что ОК старшего разряда адреса поступает с элемента НЕ 16 на первый вход дешифратора 15 непосредственно и на третий вход - через элементы И 20 и ИЛИ 23. По этим двум сигналам, независимо от того, что поступает на его числовой вход, дешифратор 15 вырабатывает О для записи в накопители 4 и 4jt (см. фиг. 2) Таким образом, введение в ЗУ незначительного оборудования позволяет осуществить.обнуление ЗУ в один такт с операцией считывания в режиме что равносильно увеличению быстродействия ЗУ. Формула изобретений Запоминающее уд.тройство, содержащее накопители, орни из входов-выходов которых подключены к одному из входов формирователя записи-считыва,ния числа, другие входы которого подключены к одному из выходов блока син хронизации и к выходу дешифратора адреса, первый и второй входы которого подключены соответственно к выходам элемента НЕ и элемента ИЛИ, входы которого соединены.с выходами триггера и выходной шиной, и выходом элемента Н один из входов которого подключен к соответствующей входной шине, другой - к шине записи и одному из входов блока синхронизации, другие входы блока синхронизации соединены с шинами обращения и считывания, соответствующие выходы блока синхронизации соединены с одним из входов адресного блока и со вторым входом триггера, первый вход которого соединен с выходом форми{хэвателя записи-считывания числа, входы-выходы которого соединены с соответствующими входамивыходами накопителей, входы которых подключены к выходам адресного блока, входы которого подключены к управляющим шинам и входу элемента НЕ, от личающееся тем, что, с целью повышения быстродействия устройства, оно содержит три элемента И, три элемента НЕ и дополнительный элемент ИЛИ, выход которого соединен с третьим входом дешифратора адреса, а .входы - с выходами первого и второго элементов И, первые входы которых соединены соответственно с первым входом дешифратора адреса и с соответствующим входом адресного блока, вторые входы первого и второго элементов И соединены соответственно с входом первого элемента НЕ, выходом третьего элемента. И и выходом первого элемента НЕ, входы третьего элемента И соединены с выходами второго и третьего элементов НЕ, входы которых подключены к шинам записи и считывания. Источники информации, принятые во внимание при экспертизе 1.Лашевский Р.А. и др. Запоминающие устройства на многоотверсных ферритовых пластинах. М., Энергия 1969, с. 7,73-76. 2.Авторское свидетельство СССР № 498647, кл. G 11 С 11/06 12. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Запоминающее устройство | 1982 |

|

SU1084903A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Запоминающее устройство | 1978 |

|

SU799001A1 |

| Запоминающее устройство | 1974 |

|

SU487417A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

Авторы

Даты

1979-11-05—Публикация

1978-10-03—Подача