Изобретение относится к технике передачи дискретной информации и может использоваться в системах передачи дискретной информации с передающего пункта на приемный.

Цель изобретения повышение достоверности передачи.

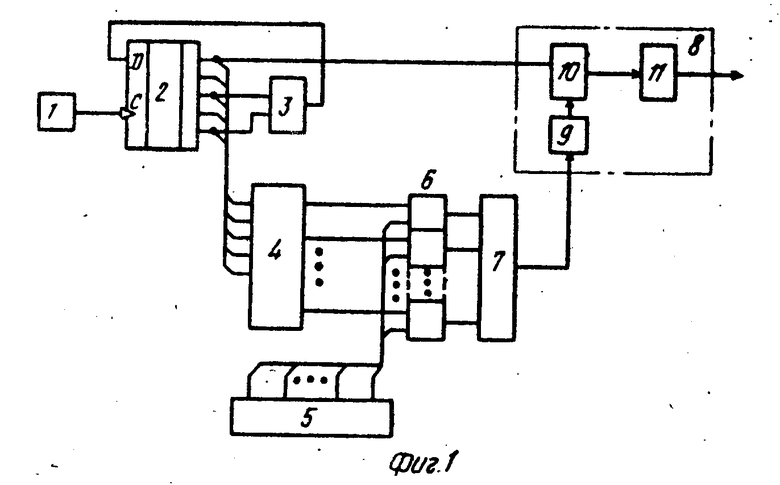

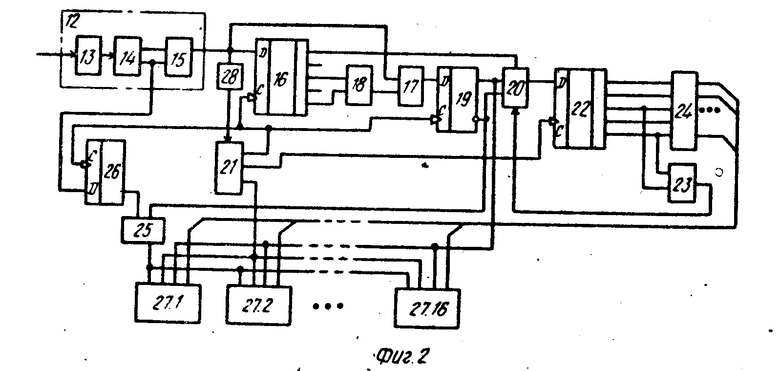

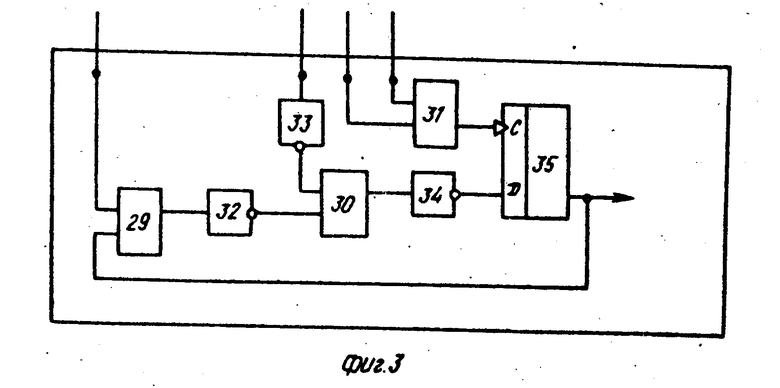

На фиг. 1 представлена структурная электрическая схема передающей стороны системы передачи дискретной информации; на фиг. 2 то же, приемной стороны; на фиг. 3 вариант выполнения блока приема информации.

Система передачи дискретной информации содержит на передающей стороне (см. фиг. 1) тактовый генератор 1, регистр сдвига 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, дешифратор 4, блок 5 датчиков информации, блок 6 совпадения, элемент ИЛИ 7 и передатчик 8, состоящего из перестраиваемого генератора 9, элемента И 10 и согласующего блока 11, а на приемной стороне (см. фиг. 2) приемник 12, состоящий из согласующего блока 13, блока 14 частотных демодуляторов и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, первый регистр 16 сдвига, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 17 и 18, первый триггер 19, коммутатор 20, формирователь 21 стробирующих импульсов, второй регистр 22 сдвига, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23, дешифратор 24, элемент И 25, второй триггер 26, блоки 27.1.27.16 приема информации, блок 28 выделения тактовой частоты.

Каждый блок 27.1.27.16 приема информации содержит (см. фиг. 3) первый, второй и третий элементы И 29, 30 и 31, первый, второй и третий инверторы 32, 33 и 34 и триггер 35.

Система передачи дискретной информации работает следующим образом. Регистр 2 сдвига на передающей стороне (см. фиг. 1), переключаемый импульсами с выхода тактового генератора 1 и охваченный обратной связью через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, генерирует на своих выходах циклическую последовательность двоичных символов, вид и длина которой определяются видом и степенью выбранного неприводного многочлена. В частности, при длине регистра 2 сдвига, равной пяти, и включении элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 (см. фиг. 1) на его выходах формируется кольцевая числовая последовательность длиной 31. В ней представлены все двоичные числа от 1 до 31. Дешифратор 4 формирует на своих шестнадцати (в общем случае 2n-1 выходах, где n длина регистра 2 сдвига) выходах импульсы при появлении на его выходах нечетных двоичных чисел, которым соответствуют единицы в кодовом кольце. В момент отсутствия сигналов с блока 5 датчиков информации блок 6 совпадения заперт, сигналы на его выходах отсутствуют, на выходе элемента ИЛИ 7 также отсутствуют сигналы, перестраиваемый генератор 9 формирует на выходе периодические импульсы с частотой следования f1, которые поступают на вход элемента И 10, на другой вход которого поступает кодовая последовательность, осуществляющая амплитудную модуляцию сигнала несущей частоты f1. Выходной сигнал элемента И 10 поступает в линию связи через согласующий блок 11.

На приемной стороне (см. фиг. 2) на первом выходе блока 14 частотных демодуляторов приемника 12 выделяется огибающая сигнала, передаваемого на частоте f2, т.е. при отсутствии сигналов блока 5 датчиков информации на первом выходе блока 14 частотных демодуляторов присутствует исходная кодовая последовательность, которая через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15 поступает на вход блока 28 выделения тактовой частоты, на первый вход первого регистра 16 сдвига и первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17. Блок 28 предназначен для выделения тактовой частоты из принимаемых сигналов и позволяет исключить канал передачи тактовой частоты, уменьшить полосу частот, занимаемую системой. Кроме того, выходной сигнал блока 28 с целью повышения помехозащищенности системы может быть стабилизирован по частоте и фазе при помощи, например, узкополосного фильтра, настроенного на тактовую частоту. Выходной сигнал блока 28 управляет работой формирователя 21 стробирующих импульсов, формирующего на своих выходах последовательности импульсов тактовой частоты, сдвинутых один относительно другого на определенное время.

Первые строб-импульсы с соответствующего выхода формирователя 2 f управляют работой первого регистра сдвига 16, осуществляющего запись синхросигналов, приходящих из линии связи, и работой первого и второго триггеров 19 и 26. Второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 включен так же, как и соответствующий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3 на передающей стороне, поэтому на его выходе на каждом также формируется сигнал, появление которого ожидается на следующем такте. Первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17 формирует на своем выходе нулевой сигнал при совпадении ожидаемого и пришедшего на первый вход первого регистра 16 сдвига сигналов и единичный сигнал при несовпадении. Эти сигналы первыми строб-импульсами формирователя 28 записываются первым триггером 19 на время такта. Если ошибка в принятом синхросигнале не зафиксирована (т.е. пришедший и ожидаемый сигнал совпадают), то первый триггер 19 находится в исходном (нулевом) состоянии, и управляемый им коммутатор 20 разрешает прохождение сигнала с первого выхода первого регистра 16 сдвига на первый вход второго регистра сдвига 22, управляемого строб-импульсами с другого выхода формирователя 21 и осуществляющего при отсутствии помех перезапись сигналов с первого регистра сдвига 16 с небольшой задержкой для исключения в схеме состязаний. Дешифратор 24 осуществляет избирание объектов.

В случае выявления первым элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 17 ошибки в синхросигнале (несовпадение ожидаемого и пришедшего сигналов) первый триггер 19 переходит во второе состояние, переключая коммутатор 20, замыкающий обратную связь второго регистра 22 сдвига на третьем элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 23, включенном аналогично элементу ИСКЛЮЧАЮЩЕЕ ИЛИ 3 с передающей стороны, и второй регистр 22 сдвига на время действия помех переходит на работу в автономном режиме, осуществляя регенерацию пораженного помехой участка кодового кольца. При исчезновении помехи коммутатор 20 снова переводит его в режим перезаписи сигналов первого регистра 16 сдвига.

Передача информации осуществляется следующим образом. При появлении на втором входе одного из элементов блока 6 совпадения сигналов от блока 5 датчиков информации на соответствующей временной позиции (см. фиг. 1) на выходе этого элемента блока 6 появляется сигнал, поступающий через элемент ИЛИ 7 на вход перестраиваемого генератора 9 и изменяющий его частоту с f1 на f2.

Таким образом, единицы в синхросигнале (кодовом кольце) передаются в линию связи частотой f1 при отсутствии информационного сигнала соответствующего датчика блока 5 на данной временной позиции с частотой f2 при наличии сигнала датчика блока 5.

В каждом из приемников 12 на приемной стороне (см. фиг. 2) огибающая сигналов, передаваемых частотой f2, выделяется на втором выходе блока 14 частотных демодуляторов и поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и на первый вход второго триггера 26. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 при отсутствии ошибок формируется кодовое кольцо в исходном формируемом регистром 2 сдвига и элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 3 виде, используемое для синхронизации передающего и приемного пунктов.

Таким образом, сигналы, передаваемые частотой f2, используются как для передачи информации, так и для передачи синхросигнала (единиц кодового кольца). Эти сигналы поступают на первый вход второго триггера 26 и записываются в него строб-импульсами с формирователя 21.

При отсутствии ошибок на первом выходе первого триггера 19 присутствует сигнал логического нуля, а на втором его выходе сигнал логической единицы. Эти сигналы обеспечивают поддержание нулевого уровня на выходе первого элемента И 29 блока 27.1.27.16 (см. фиг. 3), и через первый инвертор 31 единичного сигнала на втором входе второго элемента И 30, а также прохождение информационных сигналов с выхода второго триггера 26 через элемент И 25, второй инвертор 33, второй элемент И 30, третий инвертор 34 на первый вход триггера 35. Запись информации триггером 35 происходит по второму входу выходным сигналом третьего элемента И 31 в момент совпадения выходного сигнала дешифратора 24 и третьего строб-импульса соответствующего выхода формирователя 21.

При появлении ошибки первый триггер 19 на первом выходе формирует сигнал логической единицы, а на втором выходе сигнал логического нуля. При этом на выходе элемента И 25 независимо от состояния второго триггера 26 присутствует сигнал логического нуля, т.е. осуществляется стирание недостоверной информации, а на выходе второго инвертора 33 присутствует сигнал логической единицы.

Единичный сигнал с выхода первого триггера 19 поступает также на второй вход первого элемента И 29, на первый вход которого поступает сигнал, записанный триггером 35 на предыдущем цикле на данной временной позиции. Этот сигнал через первый элемент И 29, первый инвертор 32, второй элемент И 30 и третий инвертор 34 поступает на первый вход триггера 35 и вновь переписывается им, т.е. при выявлении ошибки ложная информация не поступает, а осуществляется подтверждение записанного на предыдущем цикле сигнала.

Информационный сигнал, передаваемый частотой f2, участвует также и в формировании синхросигнала на приеме, высокая помехозащищенность которого определяет помехозащищенность всей системы. Так как синхросигнал (кодовое кольцо) строится на основе рекуррентных соотношений, появляется возможность выявления ошибок в нем и его регенерации. При выявлении ошибок в синхросигнале осуществляется стирание принятой информации и перезапись записанного в предыдущем цикле сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПЕРЕДАТЧИКА ДИСКРЕТНЫХ СИГНАЛОВ С РАССРЕДОТОЧЕННЫМИ ПРИЕМНИКАМИ | 1983 |

|

SU1126185A1 |

| Устройство передачи и приема информации | 1991 |

|

SU1793454A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство для приема данных | 1990 |

|

SU1837347A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| СПОСОБ КОНТРОЛЯ ВЕЛИЧИНЫ ДОПУСТИМОГО СБЛИЖЕНИЯ ДВУХ ТРАНСПОРТНЫХ СРЕДСТВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2033359C1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1536422A1 |

1. Система передачи дискретной информации, содержащая на передающей стороне элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок совпадения, передатчик, дешифратор и последовательно соединенные тактовый генератор и регистр сдвига, одни выходы которого подключены к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом регистра сдвига, другой выход которого подключен к первому входу передатчика, при этом входы дешифратора соединены с соответствующими выходами регистра сдвига, а на приемной стороне - два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор, блоки приема информации, формирователь стробирующих импульсов, два триггера, элемент И и приемник, первый выход которого подключен к входу блока выделения тактовой частоты, к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого триггера, и к первому входу первого регистра сдвига, выходы которого соединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы дешифратора соединены с первыми входами блоков приема информации, отличающаяся тем, что, с целью повышения достоверности передачи, на передающей стороне введен блок датчиков информации, выходы которого подключены к одним входам блока совпадения, другие входы и выходы которого соединены соответственно с выходами дешифратора и входами элемента ИЛИ, выход которого подключен к второму входу передатчика, а на приемной стороне введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и последовательно соединенные коммутатор и второй регистр сдвига, выходы которого подключены к входам третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому входу коммутатора, второй вход которого соединен с вторыми входами блоков приема информации и первым выходом первого триггера, второй выход которого подключен к третьему входу коммутатора, четвертый вход которого соединен с соответствующим выходом первого регистра сдвига и с первым входом элемента И, к второму входу которого подключен выход второго триггера, первый вход которого соединен с вторым выходом приемника, причем выход блока выделения тактовой частоты подключен к входу формирователя стробирующих импульсов, первый выход которого соединен с вторыми входами первого и второго триггеров и первого регистра сдвига, второй и третий выходы формирователя стробирующих импульсов соединены соответственно с вторым входом второго регистра сдвига, выходы которого подключены к входам дешифратора, и с третьими входами блоков приема информации, к четвертым входам которых подключен выход элемента И.

2. Система по п. 1, отличающаяся тем, что передатчик содержит последовательно соединенные перестраиваемый генератор, элемент И и согласующий блок, выход которого является выходом передатчика, первым и вторым входами которого являются соответственно второй вход элемента И и вход перестраиваемого генератора.

3. Система по п. 1, отличающаяся тем, что приемник содержит последовательно соединенные согласующий блок и блок частотных демодуляторов, выходы которого подключены к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход последнего является первым выходом приемника, вторым выходом которого является соответствующий выход блока частотных демодуляторов, а вход согласующего блока является входом приемника.

4. Система по п. 1, отличающаяся тем, что каждый блок приема информации содержит три элемента И, три инвертора и триггер, выход которого подключен к первому входу первого элемента И, выход которого через первый инвертор подключен к первому входу второго элемента И, второй вход и выход которого соединены соответственно с выходом второго инвертора и входом третьего инвертора, выход которого подключен к первому входу триггера, второй вход которого соединен с выходом третьего элемента И, при этом первым, вторым, третьим и четвертым входами каждого блока приема информации являются соответственно первый вход третьего элемента И, второй вход первого элемента И, второй вход третьего элемента И и вход второго инвертора.

| Патент США N 3445815, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1996-05-27—Публикация

1985-01-07—Подача