(5) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1705825A2 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830382A1 |

| Устройство управления микропрограм-МНыМи пЕРЕХОдАМи | 1979 |

|

SU813428A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1161941A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

1

Изобретение относится к вычислительной технике, в частности к проектированию процессоров с микропрограммным управлением.

Известно также микропрограммное устройство, управления, содержащее запоминающее устройство, генератор тактовых импульсов, дешифраторы, элементы И, ИЛИ D.

Недостатком данного устройства является то, что введение специального разряда, непосредственно соединенного со входом блокировки дешифратора элементарных микроопераций, с одной стороны ограничивает число функций использования (до двух) данного поля, с другой стороны приводит к неэффективному расходованию разрядов микрокомандного слова.

Наиболее близким к предлагаемому является микропрограммное устройство управления, содержащее блок памяти микрокоманд, вход которого соединен с выходом адресного регистра, регист

Признака результата, блок операций, дешифратор и блок регистров, причем первый и второй выходы блока памяти микрокоманд соединены с одноименными входами блока операций, первый выход которого соединен с третьим входом блока операций и с первым входом адресного регистра, второй вход ко- ; торого соединен с третьим выходом . блока памяти микрокоманд, четвертый

to вход блока операций соединен с выходом регистра признака результата, первый вход которого соединен с выходом дешифратора 2j.

Недостатками известного устройст15ва являются низкие функциональные возможности..

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности

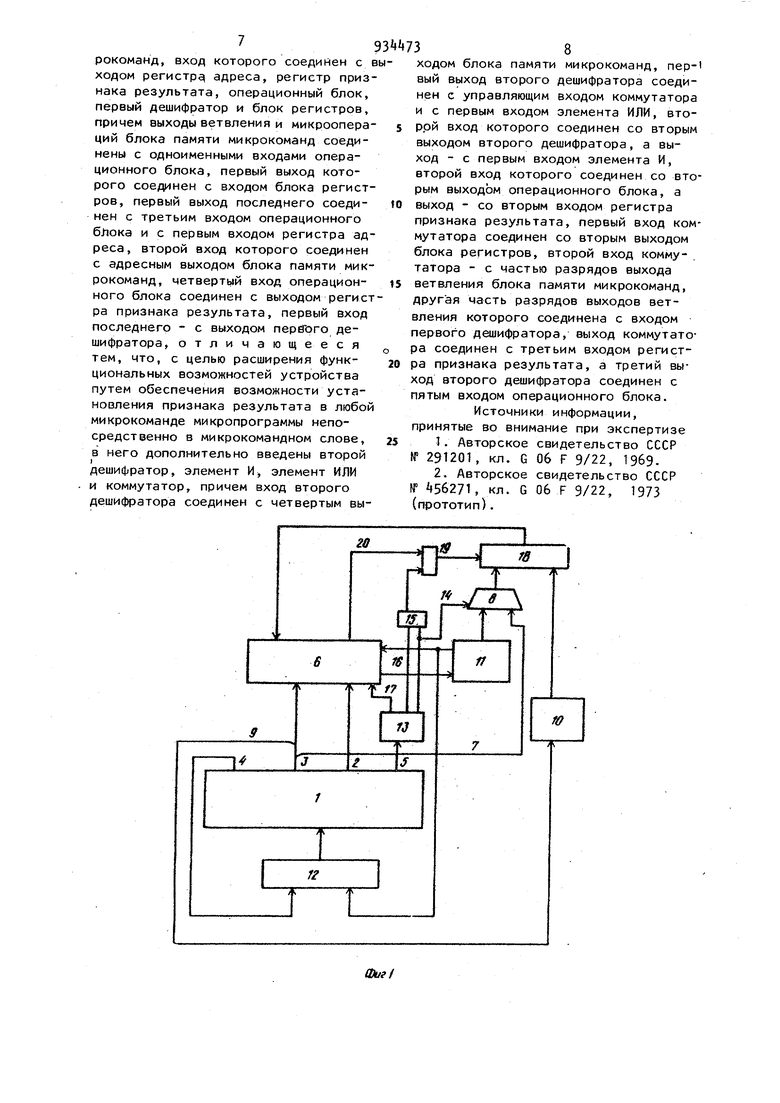

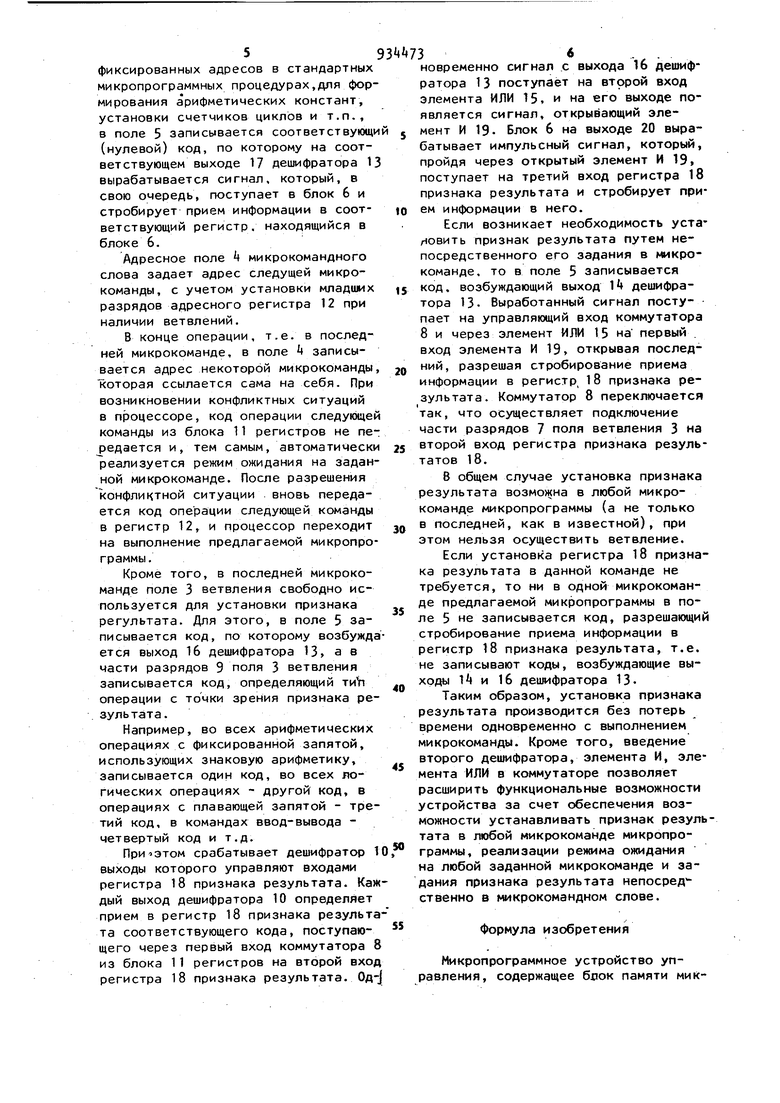

К) устанавливать признак результата в любой микрокоманде микропрограммы непосредственно в микрокомандном слове. Поставленная цель достигается тем что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, вход которого соединен с выходом адресного регистра, регистр признака результата, блок операций , первый дешифратор и блок регистров, причем первый и второй выходы блока памяти микрокоманд соединены с одноименными входами блока операций, первый выход которого соединен с входом блока регистров, первый выход которого соединен с третьим входом блока операций и с первым входом адресного регистра,второй вход K торого соединен с третьим выходом бл ка памяти микрокоманд, четвертый вход блока операции соединен с выходом регистра признака результата, вый вход которого соединен с выходом первого дешифратора, дополнитель но введены второй дешифратор, элемент И, элемент ИЛИ и коммутатор, причем вход второго дешифратора соединен с четвертым выходом блока памяти микрокоманд, первый выход второ го дешифратора соединен с управляющи входом коммутатора и с первым входом элемента ИЛИ, второй вход которого соединен со вторым выходом второго дешифратора, а выход - с первым входом элемента И, второй вход которого соединен со вторым выходом операцион ного блока, а выход - со вторым входом регистра признака результата, первый вход коммутатора соединен со вторым выходом блока регистров, второй вход коммутатора - с частью разрядов второго выхода ветвления блока памяти микрокоманд, другая часть разрядов которого соединена с входом первого дешифратора, выход коммутатора соединен с третьим входом регистра признака результата, а третий выход второго дешифратора соединен с пять1м входом операционного блока. На фиг. 1 представлена функциональная схема предлагаемого микропрограммного устройства управления; на фиг. 2 - блок-схема операционного блока. Устройство содержит блок 1 памяти микрокоманд, первый, второй, третий выходы образуют соответственно: поле 2 микроопераций, поле 3 ветвления и адресное поле 4, четвертый выход представляет собой поле 5, указывающее функциональное назначение использования поля 3 ветвления в текущей микрокоманде, операционный блок 6, часть разрядов 7 поля 3 ветвления, коммутатор 8, другая часть разрядов 9 поля 3 ветвления, дешифратор 10, блок 11 регистров, регистр 12 адреса, дешифратор 13 с первым выходом 1, элемент ИЛИ 15, второй выход 16 дешифратора 13, третий выход 17 дешифратора 13, регистр 18 признака результата, элемент И 19, второй выход 20 операционного блока 6. Операционный блок 6 содержит первый вход 21 блока, дешифратора 22 микроопераций, первый выход 23 блока. элемент И 2, второй выход 25 блока, первую группу элементов И 2б, 7 тактовых импульсов, программ„ регистр В, четвертый вход 29 блока, второй вход 30 блока, группу регистров (среди них регистр констант, регистры адреса,регистрсчетчик циклов и т.д.), часть шин 32. -32 , вторую группу элементов И 33,нулевую шину 3, пятый вход 35 блока, третий вход 36 блока, дешифратор 37 кода операций, коммутаторы 38-38. Микропрограммное устройство управления работает следующим образом. Для выполнения команд код опера- ции команды из регистра кода операции, расположенного в блоке 11 регистров передается в регистр 12. После этого из блока 1 памяти микрокоманд выбирается последовательность микрокоманд, составляющая микропрограмму выполнения текущей команды. Поле 2 микрооперации определяет тип выполняемой микрокоманды, вырабатывает элементарные микрооперации и управляет блоком 6. Поле 3 ветвления является многофункциональным. При необходимости ветвления микропрограммы во входе выполнения команды в зависимости от режимов работы процессора или промежуточных результатов в поле 5 записывается нулевой код, по которому на соответствующем выходе 17 дешифратора 13 вырабатывается сигнал разрешения ветвления, поступающий в блок 6, а в поле ветвления 3 записывается код ветвления (ненулевой), по которому блок 6 вырабатывает код для установки младших разрядов адресного регистра 12 перед выборкой следующей микрокоманды. Для использования поля 3 для других целей, например для формирования 5 фиксированных адресов в стандартных микропрограммных процедурах,для фор мирования арифметических констант, установки счетчиков циклов и т.п., в поле 5 записывается соответствующ (нулевой) код, по которому на соответствующем выходе 17 дешифратора 1 вырабатывается сигнал, который, в свою очередь, поступает в блок 6 и стробирует прием информации в соответствующий регистр, находящийся в блоке 6. Адресное поле k микрокомандного слова задает адрес следущей микрокоманды, с учетом установки младших разрядов адресного регистра 12 при наличии ветвлений. В конце операции, т.е. в последней микрокоманде, в поле записывается адрес некоторой микрокоманды Т оторая ссылается сама на себя. При возникновении конфликтных ситуаций в процессоре, код операции следующе команды из блока 11 регистров не пе редается и, тем самым, автоматическ реализуется режим ожидания на задан ной микрокоманде. После разрешения конфликтной ситуации вновь передается код операции следующей команды в регистр 12, и процессор переходит на выполнение предлагаемой микропро граммы . Кроме того, в последней микрокоманде поле 3 ветвления свободно используется для установки признака регультата. Для этого, в поле 5 записывается код, по которому возбуждз ется выход 16 дешифратора 13 а а части разрядов 9 поля 3 ветвления записывается код, определяющий тип операции с точки зрения признака результата. Например, во всех арифметических операциях с фиксированной запятой, использующих знаковую арифметику, записывается один код, во всех логических операциях - другой код, в операциях с плавающей запятой - третий код, в командах ввод-вывода четвертый код и т.д. срабатывает дешифратор 1 выходы которого управляют входами регистра 18 признака результата. Каж дый выход дешифратора 10 определяет прием в регистр 18 признака результа та соответствующего кода, поступающего через первый вход коммутатора 8 из блока 11 регистров на второй вход регистра 18 признака результата. Од3новременно сигнал с выхода 16 дешифратора 13 поступает на второй вход элемента ИЛИ 15, и на его выходе появляется сигнал, открывающий элемент И 19. Блок 6 на выходе 20 вырабатывает импульсный сигнал, который, пройдя через открытый элемент И 19, поступает на третий вход регистра 18 признака результата и стробирует прием информации в него. Если возникает необходимость уста новить признак результата путем непосредственного его задания в микрокоманде, то в поле 5 записывается код, возбуждающий выход 1 j дешифратора 13. Выработанный сигнал поступает на управляющий вход коммутатора 8 и через элемент ИЛИ 15 на первый . вход элемента И 19, открывая последний, разрешая стробирование приема информации в регистр, 18 признака результата. Коммутатор 8 переключается так, что осуществляет подключение части разрядов 7 поля ветвления 3 на второй вход регистра признака результатов 18. В общем случае установка признака результата возможна в любой микрокоманде микропрограммы (а не только в последней, как в известной), при этом нельзя осуществить ветвление. Если установка регистра 18 признака результата в данной команде не требуется, то ни в одной микрокоманде предлагаемой микропрограммы в поле 5 не записывается код, разрешающий стробирование приема информации в регистр 18 признака результата, т.е, не записывают коды, возбуждающие выходы 1 и 16 дешифратора 13Таким образом, установка признака результата производится без потерь времени одновременно с выполнением микрокоманды. Кроме того, введение второго дешифратора, элемента И, элемента ИЛИ в коммутаторе позволяет расширить функциональные возможности устройства за счет обеспечения возможности устанавливать признак результата в любой микрокоманде микропрограммы, реализации режима ожидания на любой заданной микрокоманде и задания признака результата непосред ственно в микрокомандном слове. Формула изобретения Микропрограммное устройство управления, содержащее бдок памяти микрокоманд, вход которого соединен с ходом регистру адреса, регистр признака результата, операционный блок, первый дешифратор и блок регистров, причем выходы ветвления и микроопераций блока памяти микрокоманд соединены с одноименными входами операционного блока, первый выход которого соединен с входом блока регистров, первый выход последнего соединен с третьим входом операционного блока и с первым входом регистра адреса , второй вход которого соединен с адресным выходом блока памяти микрокоманд, четвертый вход операционного блока соединен с выходом регист ра признака результата, первый вход последнего - с выходом перйЪго дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности установления признака результата в любой микрокоманде микропрограммы непосредственно в микрокомандном слове, в него дополнительно введены второй дешифратор, элемент И, элемент ИЛИ и коммутатор, причем вход второго дешифратора соединен с четвертым выв38 ходом блока памяти микрокоманд, первый выход второго дешифратора соединен с управляющим входом коммутатора и с первым входом элемента ИЛИ, второй вход которого соединен со вторым выходом второго дешифратора, а выход - с первым входом элемента И, второй вход которого соединен со вторым выходом операционного блока, а выход - со вторым входом регистра признака результата, первый вход коммутатора соединен со вторым выходом блока регистров, второй вход коммутатора - с частью разрядов выхода ветвления блока памяти микрокоманд, другая часть разрядов выходов ветвления которого соединена с входом первого дешифратора, выход коммутатора соединен с третьим входом регистра признака результата, а третий выход второго дешифратора соединен с пятым входом операционного блока. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 291201, кл. G 06 F 9/22, 19б9. 2, Авторское свидетельство СССР ff «56271, кл. G 06 F 9/22, 1973 (прототип).

Авторы

Даты

1982-06-07—Публикация

1980-08-15—Подача