ления подключена к второму управляю шему входу информационной магистрали, причем устройство микропрограммного управления содержит четыре группы элементов И, четыре элемента И, элемент НЕ, дешифратор,элемент ИЛИ, генератор тактовых импульсов, регистр микрокоманд, память микрокоманд и счетчик адреса, причем вход устройства микропрограммного управления соединен с первым входом первого элемента И, второй.вход которого соединен с первым выходом дешифратора и с первыми входами элементов И первой и второй групп, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого подключен к первым входам элементов И третьей группы, к входу записи счетчика адреса и через элемент НЕ к первому входу второго элемента И, второй вход которого соединен с первым выходом генератора тактовых импульсов, второй выход которого подключен к синхровходу регистра микрокоманд, информационный вход которого соединен с выходом памяти микрокоманд, адресный вход которой соединен с выходом счетчика адреса, счетный вход которого соединен с выходом второго элемента И, а информационный вход счетчика адреса подключен к выходам элементов И второй и третьей групп, входы которых и выходы элементов И первой группы подключены к входу/выходу устройства , выход регистра микрокоманд подключен к второй и третьей группам выходов устройства, к первым входам элементов И четвертой группы, к вторым входам элементов И первой группы, к входу дешифратора и к первым входам третьего и четвертого элементов И, вторые входы которых подключены к.второму выходу дешифратора, а выходы - к пятой группе выходов устройства, второй и третий выходы дешифратора подключены соответственно к четвертой группе выходов устройства, четвертый выход дешифратора подключен к вторым входам элементов четвертой группы, выходы которых подключены к первой группе выходов устройства и к второму входу элемен|та ИЛИ, регистр команд содержит п счетчиков, операционный регистр, (п + 2) группы элементов И, причем информационный вход регистра команд соедине: с информационными i-ro (i l,.,.,n) счетчика и

операционного регистра, управляющие входы которых подключены к входу занесения регистра команд, /счетные входы п счетчиков подключены к группе управляющих входов регистра команд, прямые и инверсные выходы п счетчиков подключены к группе управляющих выходов регистра команд, первые входы элементов И i-й группы (1 3,...,п + 2) подключены к входам занесения регистра команд, выходы элементов И i-й группы (i 3,,..,п +2) подключены к информационному выходу регистра команд, выходы i-ro счетчика (i 1,...,п) подключены к -й(о 2,...,п + 1) группе выходов регистра команд и к вторым входам элементов И i-й группы (i l...n) соответственно, выход операционного регистра подключен к первой группе выходов регистра команд и к вторым входам элементов И(п+1)и(п+2) групп.

2.Процессор по п. 1, о т л и чающийся тем, что адресный коммутатор содержит (п + 1) группу элементов И, дешифратор и группу эл ментов ИЛИ, причем первые входы элементов И i-й группы (i 1,...,п) подключены соответственно к 3-й группе информационных входов адресного коммутатора {j 2,..,,п + 1), первая группа информационных.входов коммутатора подключена к первым входам элементов И (п + 1)-й группы и

к информационному входу дешифратора i-й выход которого соединен с вторыми входами элементов И i-й группы (i 1,...,п), вторые входы элементов И (п + 1)-й группы и управляющий вход дешифратора подключены к группе управляющих входов коммутатора, выходы элементов И i-й группы (i 1,...,п + 1) подключены соответственно к i-му входу элементов И группы, выходы которых подключены к группе выходов коммутатора.

3.Процессор по п. 1, отличающийся тем, что коммутатор ветвлений содержит две группы элементов И, два элемента ИЛИ, два дешифратора, причем выход коммутатора соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, первые входы которых подключены к выходу первого дешифратора, вход KOl-oporo подключен к первой группе информационных входов коммутатора, вход второго дешифратора подключен к второй группе информационных вхрдов коммутатора, третья группа информационных входов которого подключена к первым входам элементов И второй группы, объединена

с выходом второго элемента ИЛИ, группой управляющих входов коммутатора и подключена к вторым входам элементов И первой группы,,выход второго дешифратора подключен к вторым входам элементов И второй группы, выходы которых подключены соответственно ко входам ВТОРОГО элемента ИЛИ.

4.Процессор по п. 1, о т л и чающийся тем, что операционный коммутатор содержит дешифратор.

группу элементов И и группу элементов ИЛИ, причем группа управляющих входов коммутатора подключена к первым входам элементов И группы и к управляющему входу дешифратора, информационный вход которого подключен к первой и второй группам информационных входов коммутатора,.вторая группа информационных входов коммутатора подключена к вторым входам элементов И группы, выходы которых подключены к первым входам элементов ИЛИ.группы, вторые входы которых подключены к выходу дешифратора, а выходы элементов ИЛИ группы подключены к группе информационных выходов и выходу старшего разряда коммутатора «соответственно.

5. Процессор по п. 1, отличающийся тем, что информационная магистраль содержит две группы элементов И, два элемента ИЛИ и регистр, причем первый и второй входы первого и второго элементов ИЛИ подключены к первок(у и второму управляющим входам магистрали, вход и выход которой подключены соответственно к первым входам и выходам элементов И первой и второй групп первые входы элементов И второй группы соединены с выходами регистра, входы которого соединены с выходами элементов И первой группы, вторые входы элементов И первой и второй групп соединены соответственно с выходами первого и второго элементов ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для микропрограммногоупРАВлЕНия | 1979 |

|

SU822186A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1211724A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1091160A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1164747A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

1. ПРОЦЕССОР С МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ, содержаний регистр команд, регистр состояний и операционное устройство, первая группа информационных входов которого подключена к выходу информационной магистрали, устройство микропрограммного управления, первая группа выходов которого подключена к входам занесения регистра команд и регистра состояний, первая группа информационных входов которого подключена к выходу признаков операционного ус гройства, группа информационных выходов которого подключена к входу ййформационной магистрали, отличающийся тем, что, с целью сокращения оборудования , он содержит адресный коммутатор, коммутатор ветвлений и операционный коммутатор, группа входов/выходов устройства микропрограммного управления подключена к входу/выходу информационной магистрали, вторая группа выходов устройства микропрограммного управления подключена к первым группам информационных входов коммутатора ветвлений и гщресного когФкутатора, третья группа выходов - к первой группе информационных входов операционного коммутатора, вторая группа информационных входов которого соединена с второй группой информационных входов коммутатора ветвлений и подключена к первой группе выходов регистра команд, i-ая (i l,...,n);(n - число операндов в команде), группа информационных выходов которого подключена соответственно к i-й группе информационных входов адресного коммутатора, группа выходов которого подключена к второй группе информационных входов операционного устройства, вход кода операций которого подключен к первому управляющему входу информационной магистрали и к группе информа- ig ционных выходов операционного коммутатора , группа управлятацих входов которого и группа управляющих входов адресного котимутатора соединены соответственно с четвертой группой выходов устройства микропрограммного управления, вход которого подключен к выходу коммутатора ветвлениП, третья группа информационных входов ко TODoro соединена с первой группой to выходов регистра состояний, вторая 4iai группа выходов которого подключена к входу информационной магистрали, to вторая группа информационных вхо дов регистра состояний соединена с выходом информационной магистрали, ЭО выход старшего разряда операционного коммутатора подключен к управляющему входу регистра состояний, группа управляющих выходов регистра команд подключена к группе управляющих входов коммутатора ветвлений, пятая группа выходов устройства микропрограммного управления подключена соответственно к группе управляющих входов регистра команд, информационные вход/выход которого подключен к входу/выходу информационной магистрали, первая группа выходов устройства микропрограммного управ

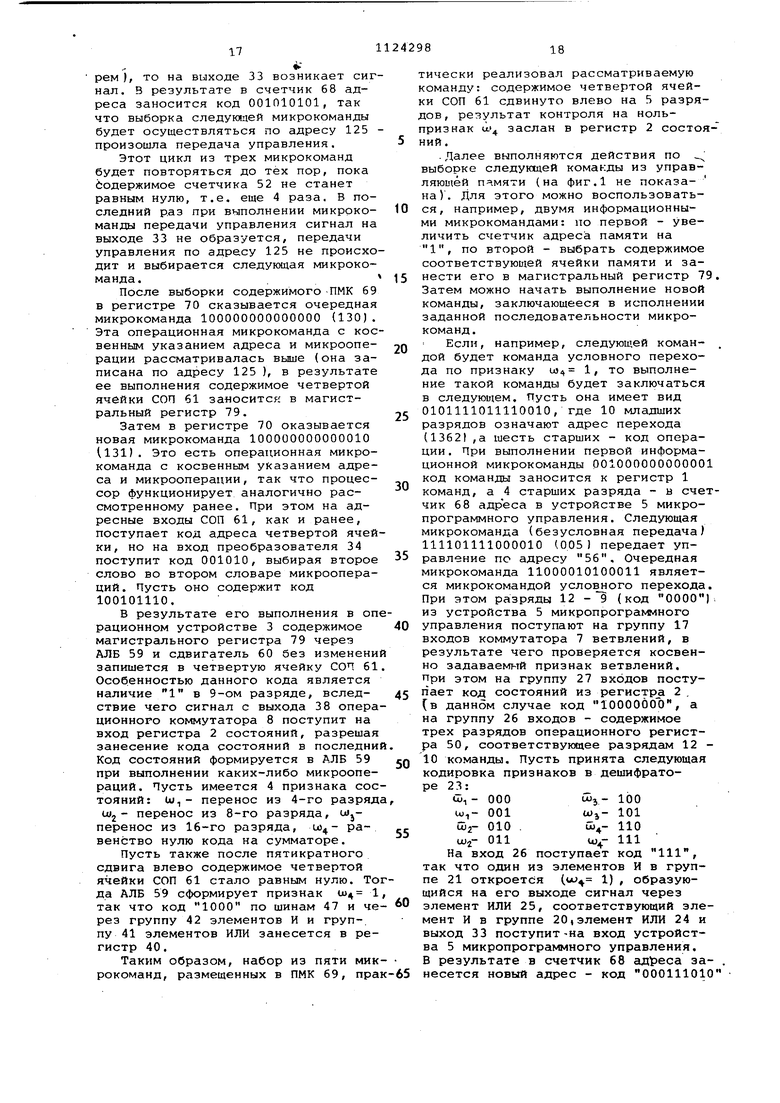

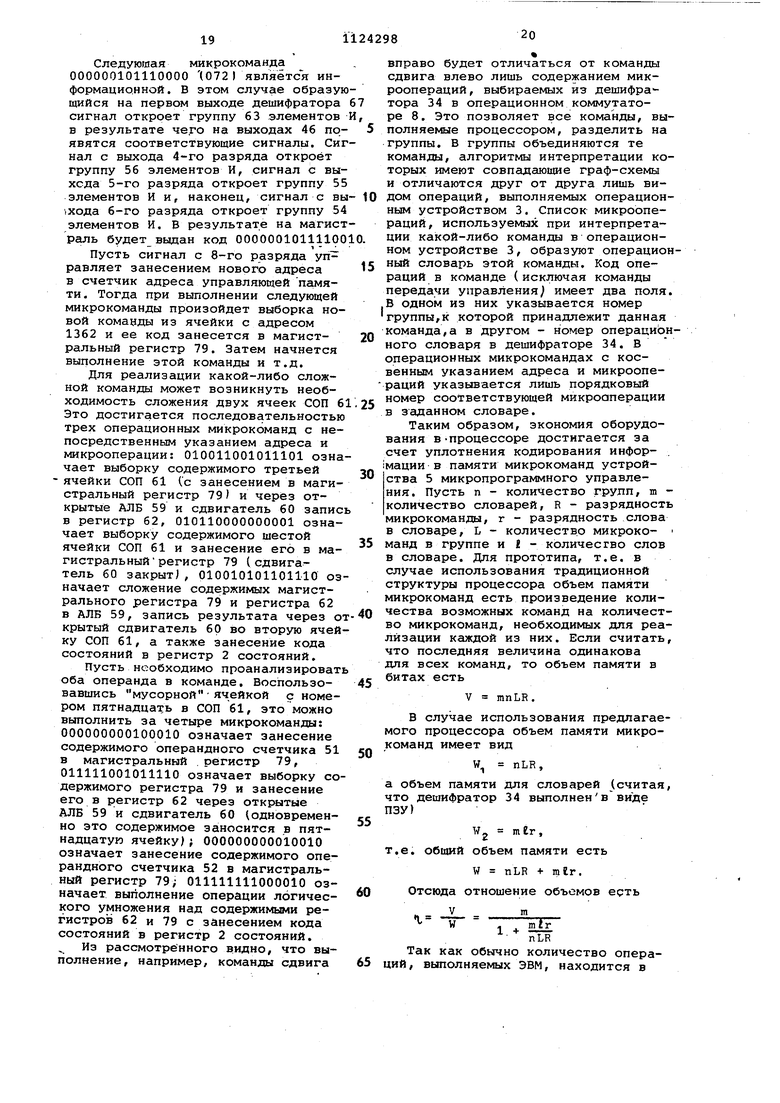

Изобретение относится к вьочислительной технике и может быть ис.пользовано в ЭВМ малой и средней производительности.

Известна вычислительная машина, у которой система команд многооперандна и интерпретация команд на микропрограммном уровне требует выполнения большого числа микроко-. манд tl3.

Недостатком ее является большой объем памяти микрокоманд.

Наиболее близким к изобретению является процессор, содержащий регистр команд, регистр состояний и операционное устройство, первая група входов которых подсоединена к информационной магистрали, устройство микропрограммного управления, подсоединенное к управляющим входам регистра команд и регистра состояНИИ, вторая группа входов которого подключена к операционному устройству, группа выходов которого подсоединена к информационной магистрали , вторая и третья группа входов операционного устройства подключены соответственно к устройству микропрограммного управления и к регистру состояний, а выход операционного устройства - к устройству микропрограммного управления, группа входов которого подсоединена к регйстру команд 2.

Основной недостаток этого процессора - большие затраты памяти микро команд в устройстве микропрограммного управления при реализации команд требующих исполнения последовательности из нескольких операций операционного устройства.

Цель предлагаемого изобретения сокращение оборудования.

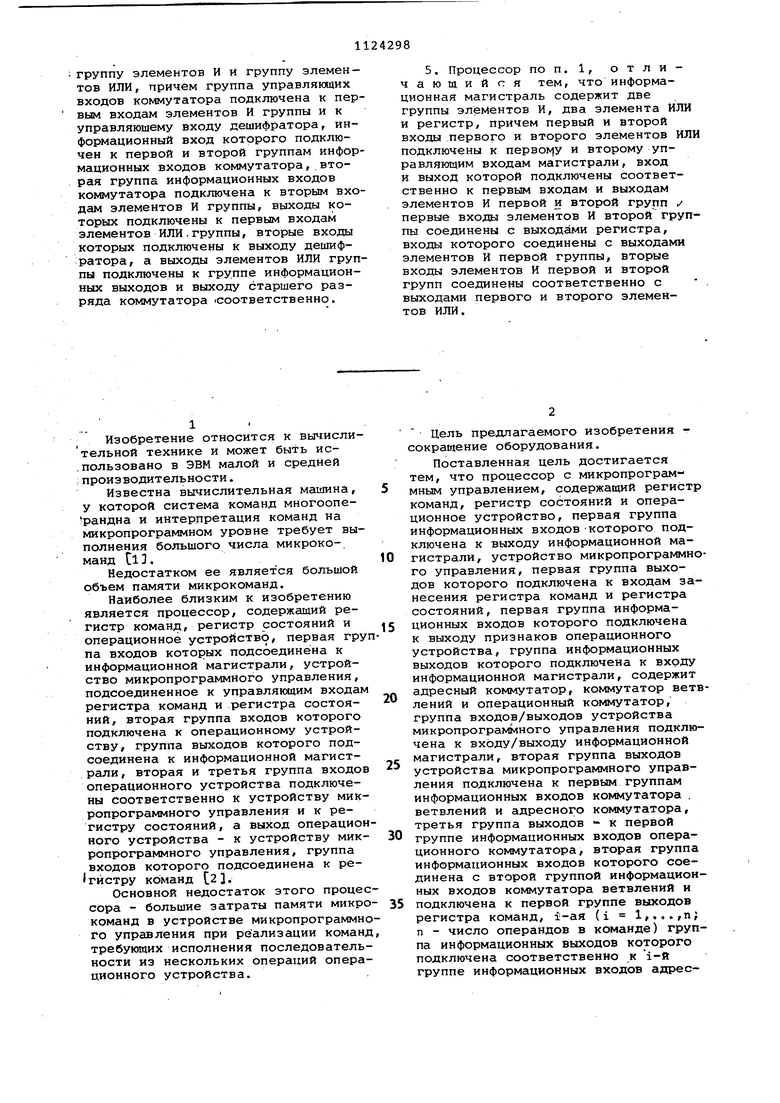

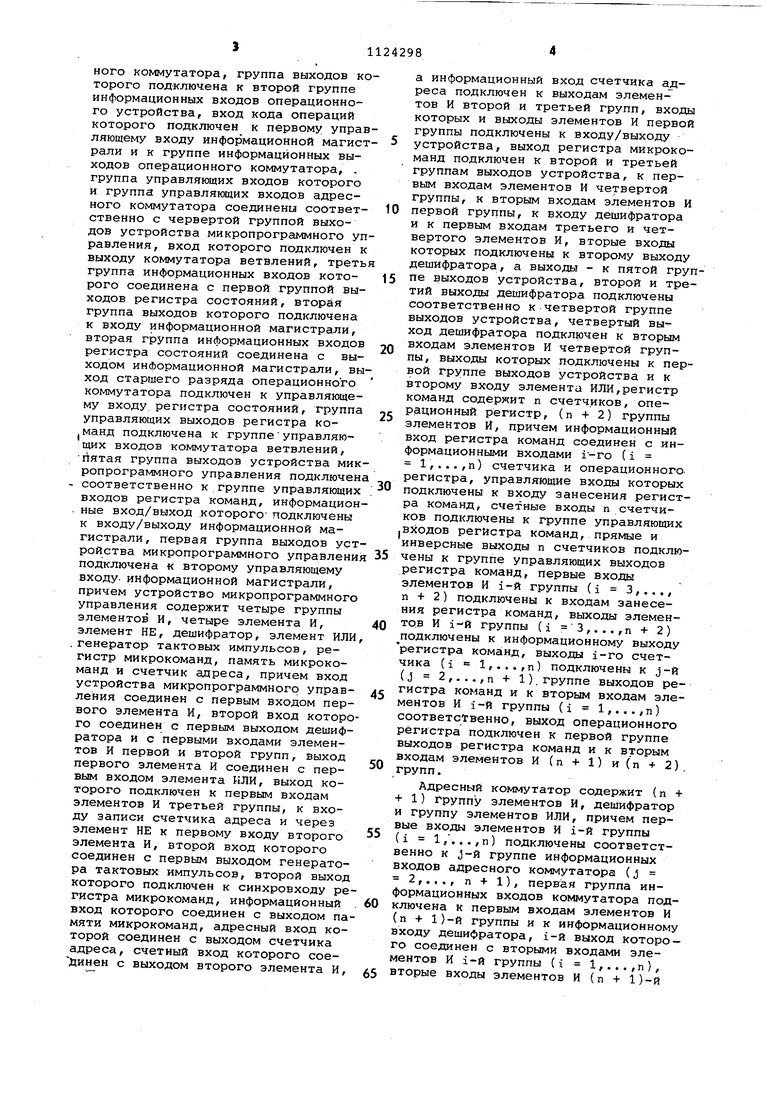

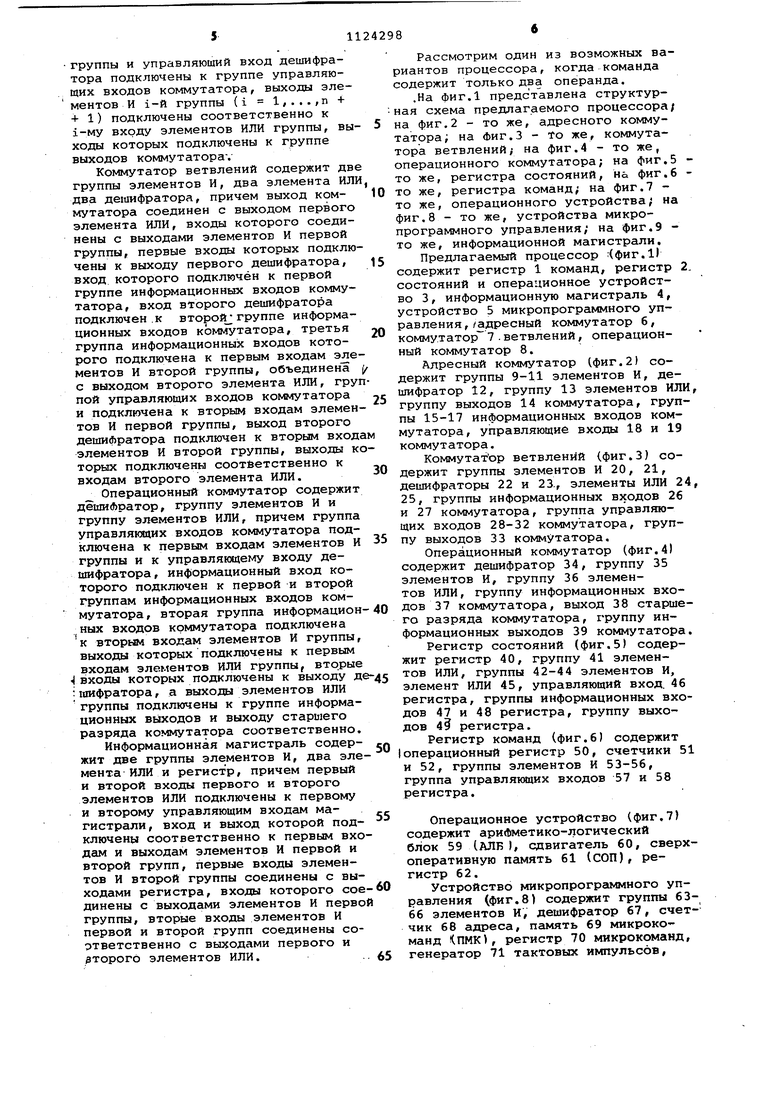

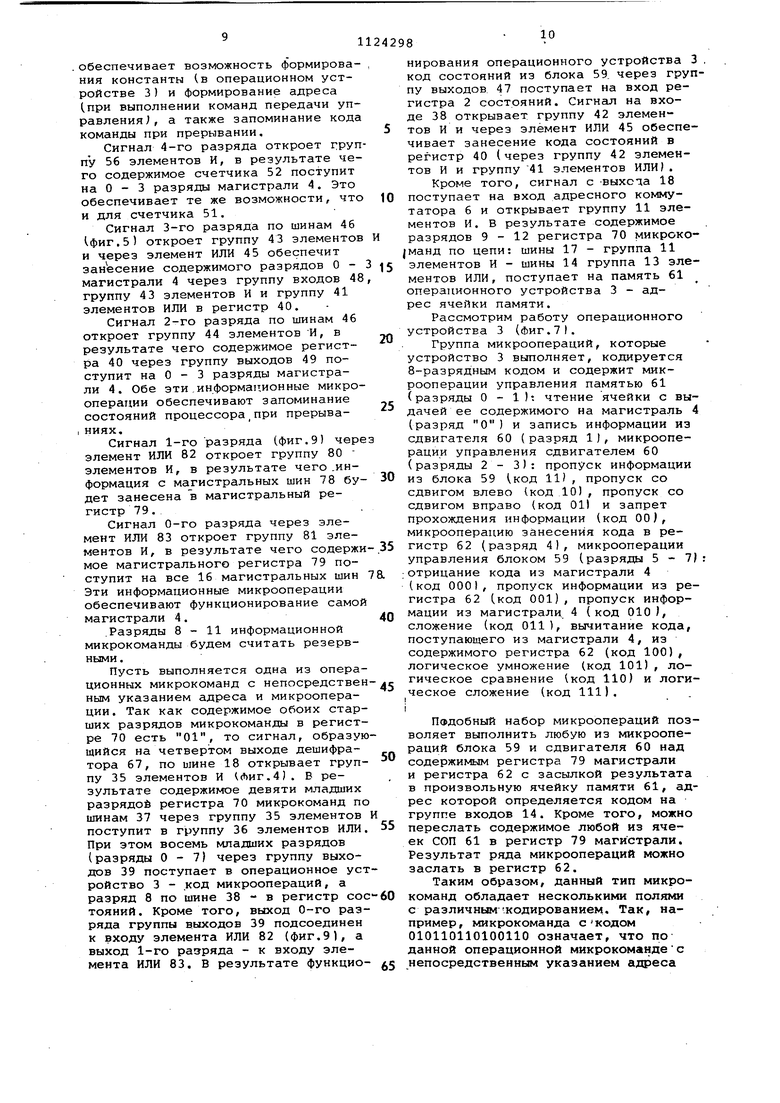

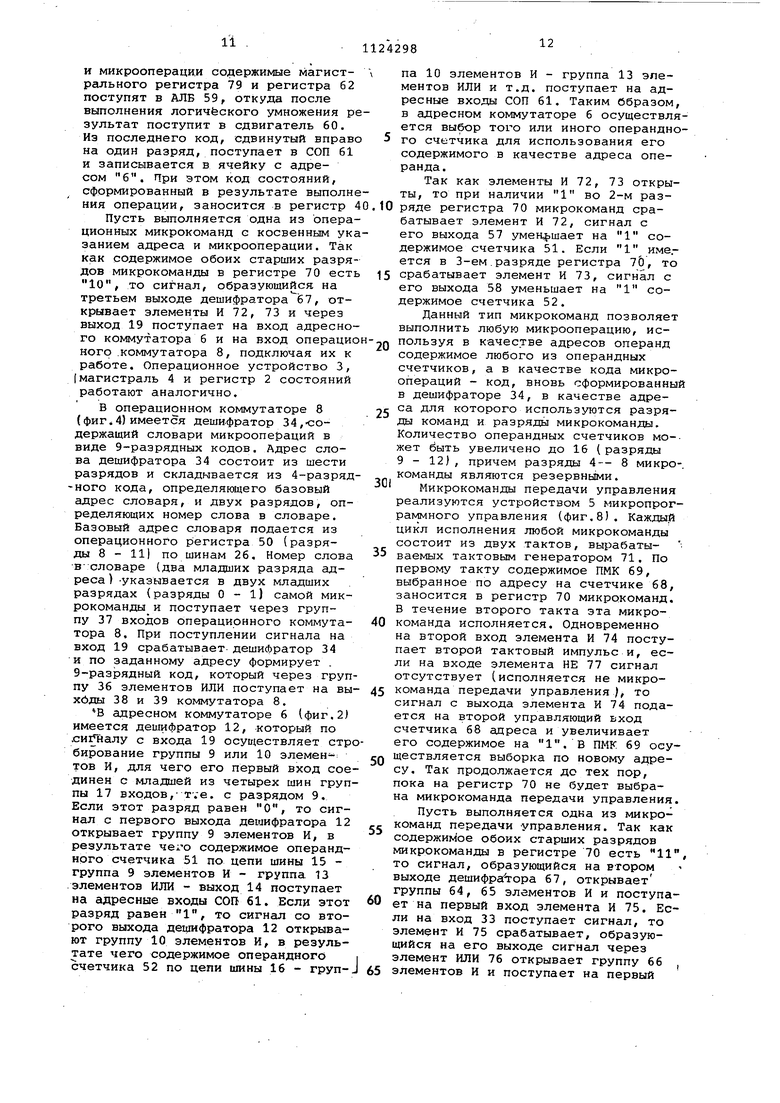

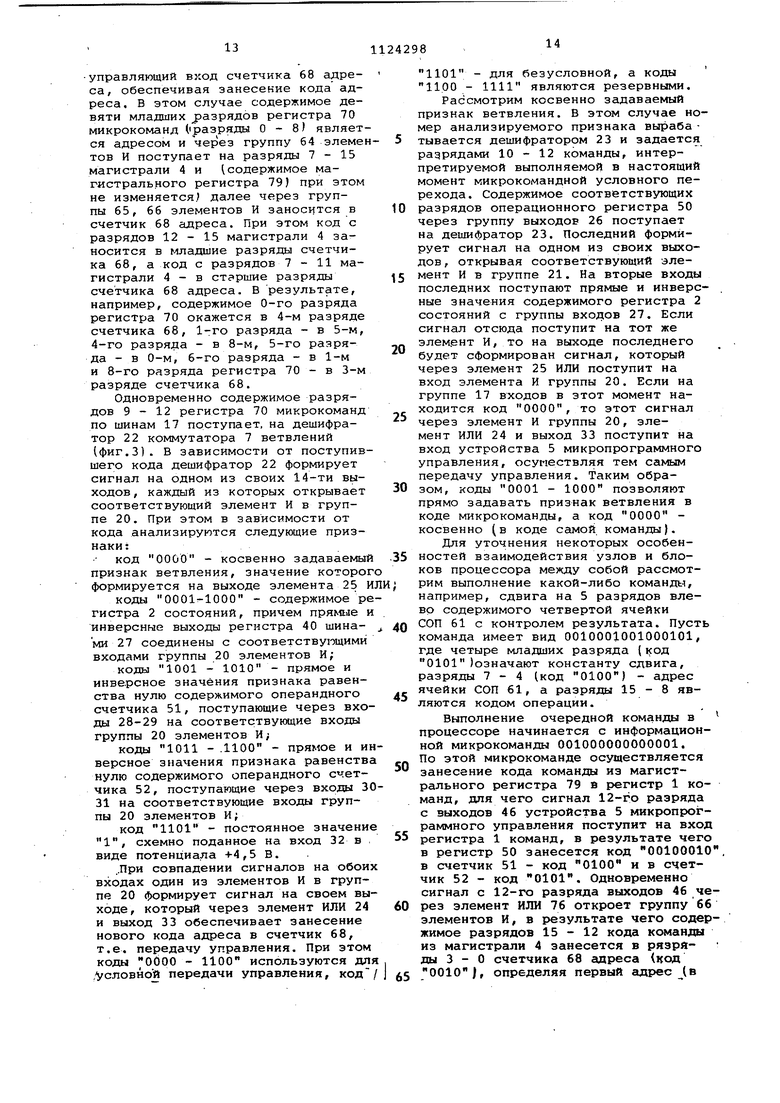

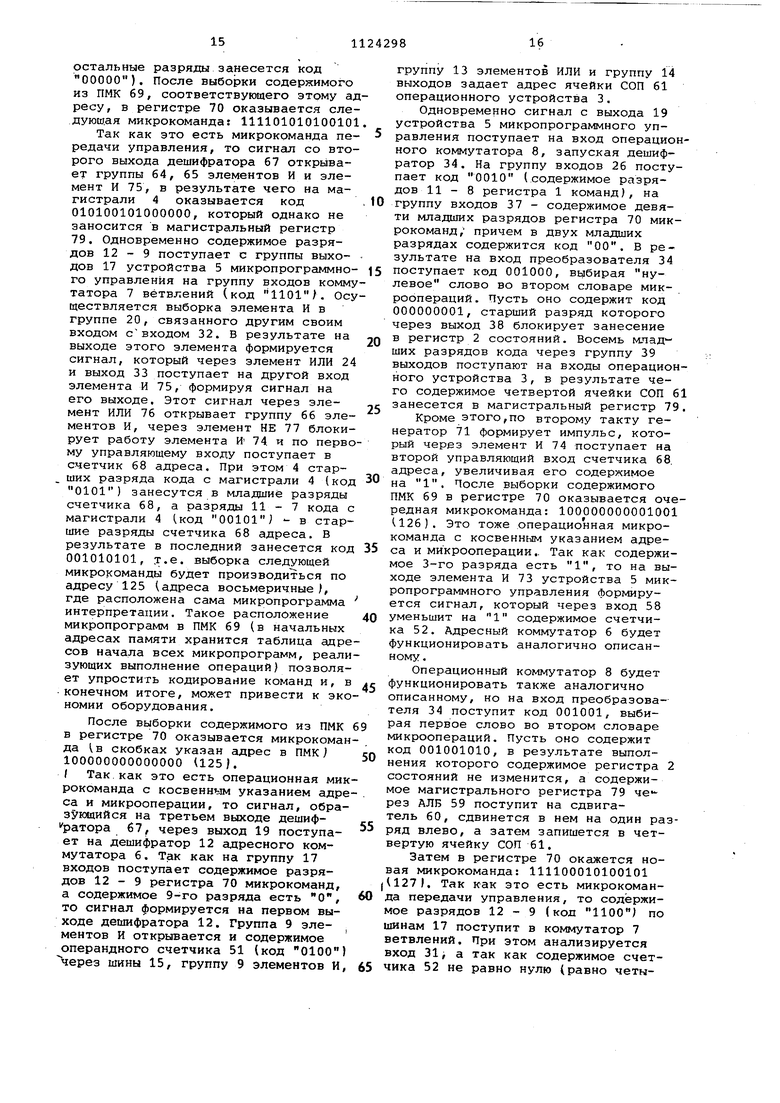

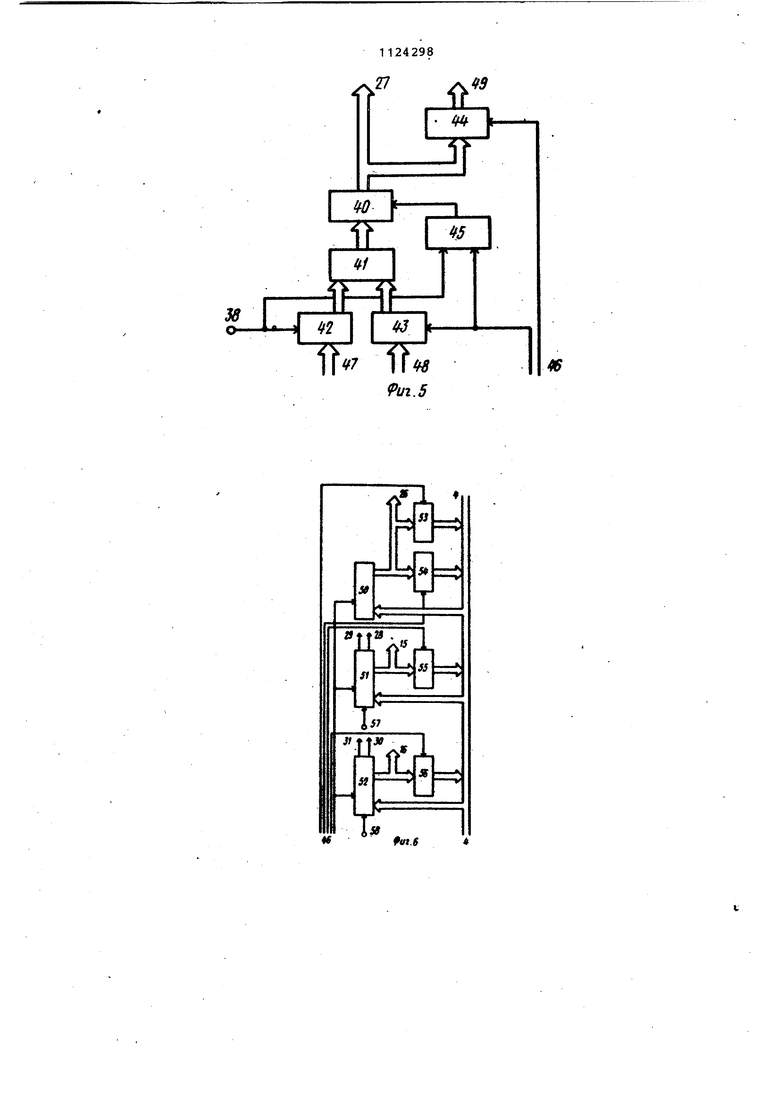

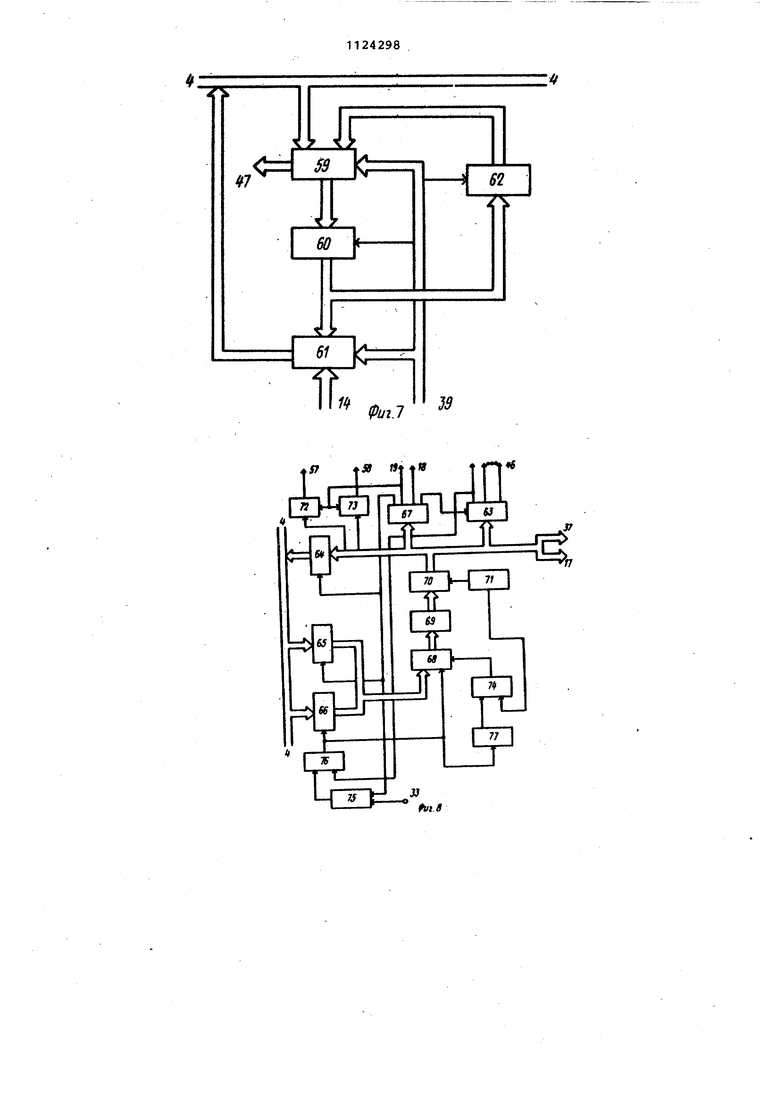

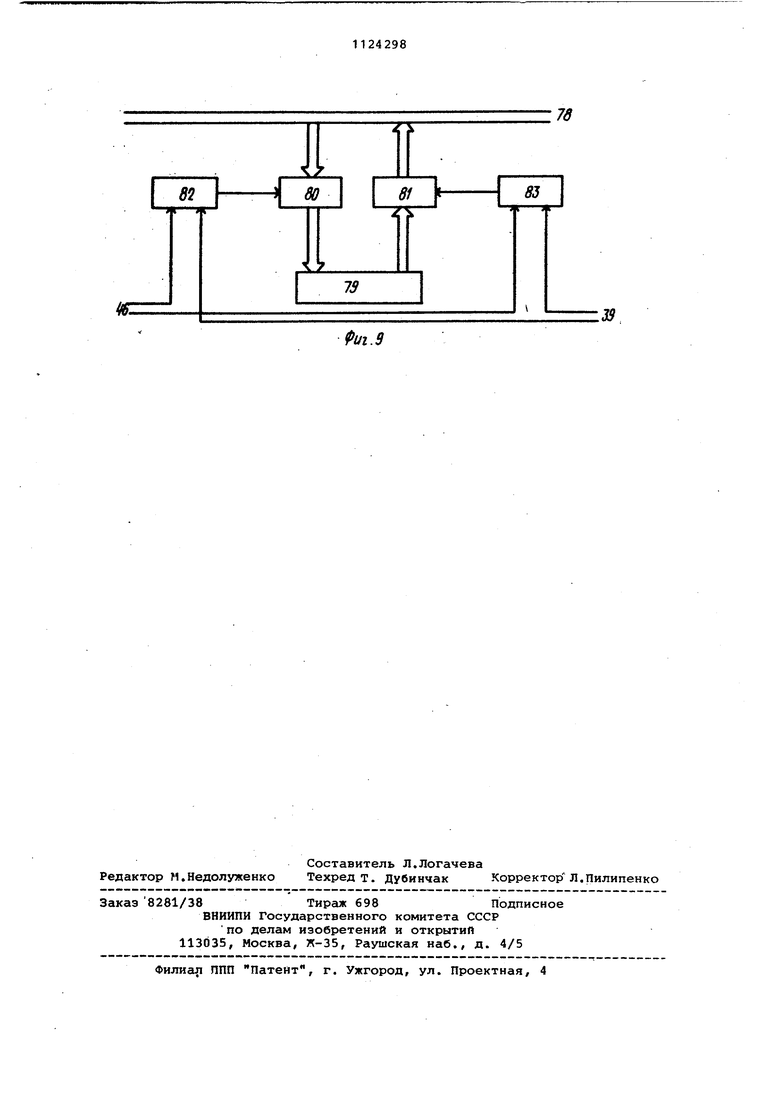

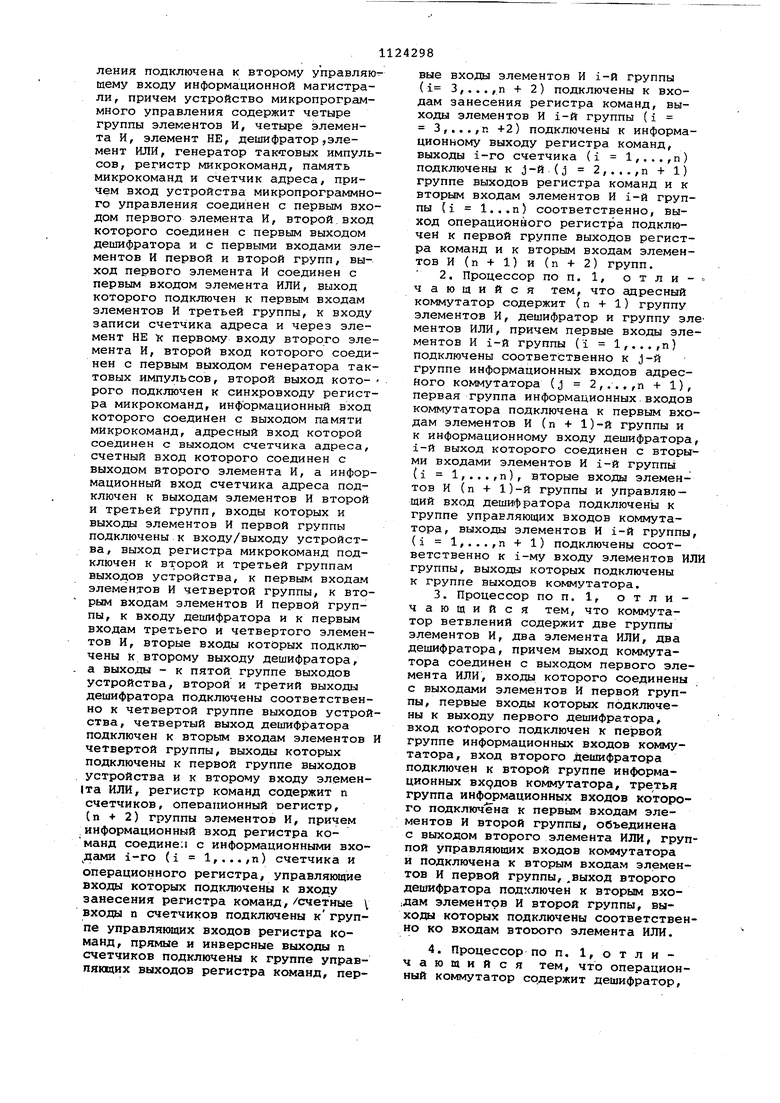

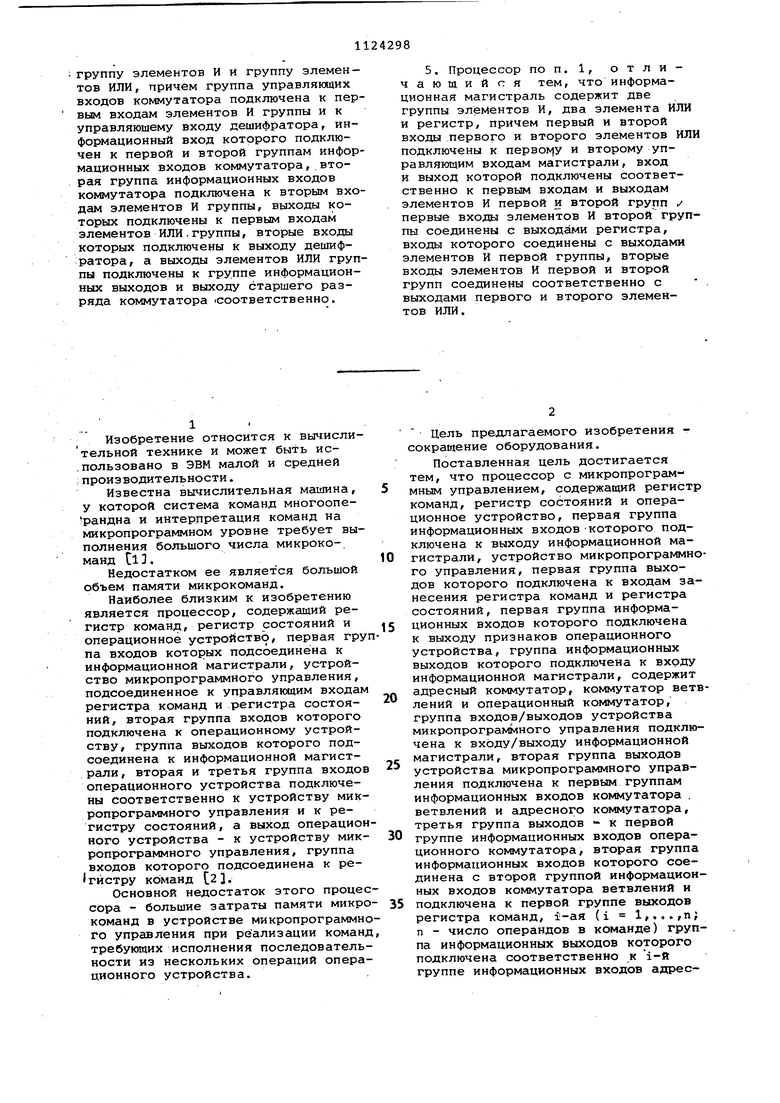

Поставленная цель достигается тем, что процессор с микропрограм мным управлением, содержащий регистр команд, регистр состояний и операционное устройство, первая группа информационных входов которого подключена к выходу информационной магистрали, устройство микропрограммного управления, первая группа выходов которого подключена к входам занесения регистра команд и регистра состояний, первая группа информационных входов которого подключена к выходу признаков операционного устройства, группа информационных выходов которого подключена к входу информационной магистрали, содержит адресный коммутатор, коммутатор ветвлений и операционный коммутатор, группа входов/выходов устройства микропрограммного управления подключена к входу/выходу информационной магистрали, вторая группа выходов устройства микропрогрс1ммного управления подключена к первым группам информационных входов коммутатора . ветвлений и адресного коммутатора, третья группа выходов - к первой группе информационных входов операционного коммутатора, вторая группа информационных входов которого соединена с второй группой информационных входов коммутатора ветвлений и подключена к первой группе выходов регистра команд, i-ая (i 1,.,.,п; п - число операндов в команде) группа информационных выходов которого подключена соответственно к Ч-й группе информационных входов адресного коммутатора, группа выходов ко торого подключена к второй группе информационных входов операционного устройства, вход кода операций которого подключен к первому управ ляющему входу информационной магист рали и к группе информационных выходов операционного коммутатора, . группа управляющих входов которого и группа управляющих входов адресного коммутатора соединены соответственно с червертой группой выходов устройства микропрограммного уп равления, вход которого подключен к выходу коммутатора ветвлений, треть группа информационных входов которого соединена с первой группой выходов регистра состояний, вторая группа выходов которого подключена к входу информационной магистрали, вторая группа информационных входов регистра состояний соединена с выходом информационной магистрали, вы ход старшего разряда операционного коммутатора подключен к управляющему входу регистра состояний, группа управляющих выходов регистра команд подключена к группеуправляющих входов коммутатора ветвлений, гтятая группа выходов устройства мик ропрограммного управления подключен . соответственно к группе управляющих входов регистра команд, информацион . ные вход/выход .которого подключены к входу/выходу информационной магистрали , первая группа выходов уст ройства микропрограммного управлени подключена к второму управляющему входу, информационной магистрали, причем устройство микропрограммного управления содержит четыре группы элементов И, четыре элемента И, элемент НЕ, дешифратор, элемент ИЛИ ,генератор тактовых импульсов, регистр микрокоманд, память микрокоманд и счетчик адреса, причем вход устройства микропрограммного управления соединен с первым входом первого элемента И, второй вход которо го соединен с первым выходом дешифратора и с первыми входами элементов И первой и второй групп, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого подключен к первым входам элементов И третьей группы, к входу записи счетчика адреса и через элемент НЕ к первому входу второго элемента И, второй вход которого соединен с первым выходом генератора тактовых импульсов, второй выход которого подключен к синхровходу ре гистра микрокоманд, информационный вход которого соединен с выходом па мяти микрокоманд, адресный вход которой соединен с выходом счетчика адреса, счетный вход которого сое динен с выходом второго элемента И, а информационный вход счетчика адреса подключен к выходам элементов И второй и третьей групп, входы которых и выходы элементов И первой группы подключены к входу/выходу устройства, выход регистра микрокоманд подключен к второй и третьей группам выходов устройства, к первым входам элементов И четвертой группы, к вторым входам элементов И первой группы, к входу дешифратора и к первым входам третьего и четвертого элементов И, вторые входы которых подключены к второму выходу дешифратора, а выходы - к пятой группе выходов устройства, второй и третий выходы дешифратора подключены соответственно к четвертой группе выходов устройства, четвертый выход дешифратора подключен к вторым входам элементов И четвертой группы, выходы которых подключены к первой группе выходов устройства и к второму входу элемента ИЛИ,регистр команд содержит п счетчиков, операционный регистр, (п + 2) группы элементов И, причем информационный вход регистра команд соединен с информационными входами i-ro (i 1,. .. ,n) счетчика и операционногорегистра, управляющие входы которых подключены к входу занесения регистра команд, счетные входы п счетчиков подключены к группе управляющих входов регистра команд, прямые и инверсные выходы п счетчиков подключены к группе управляющих выходов регистра команд, первые входы элементов И i-й группы (i 3,.,., п + 2) подключены к входам эанесения регистра команд, выходы элементов И i-й группы (i -3,...,п + 2) подключены к информационному выходу регистра команд, выходы 1-го счетчика (i « 1,,..,п) подключены к j-й (j 2,...,п + 1) группе выходов регистра команд и к вторым входам элементов И i-й группы (i 1,.,.,п) соответственно, выход операционного регистра подключен к первой группе выходов регистра команд и к вторым входам элементов И(п+1)и(п+2) групп. Адресный коммутатор содержит {п + + 1) группу элементов И, дешифратор и группу элементов ИЛИ, причем первые входы элементов И i-й группы { i 1,.. ., п) подключены соответственно к J-й группе информационных входов адресного коммутатора (j 2,.,,, п + 1), первая группа информационных входов коммутатора подключена к первым входам элементов И (п + 1)-й группы и к информационному входу дешифратора, i-й выход которого соединен с вторыми входами элементов И i-й группы (1 1,...,п), вторые входы элементов И (п + 1)-й группы и управляющий вход дешифратора подключены к группе управляющих входов коммутатора, выходы эле ментов И i-й группы (i 1,...,п + + 1) подключены соответственно к i-му входу элементов ИЛИ группы, вы ходы которых подключены к группе выходов коммутатора-. Коммутатор ветвлений содержит дв группы элементов И, два элемента ИЛ два де1иифратора, причем выход коммутатора соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, первые входы которых подклю чены к выходу первого дешифратора, вход которого подключён к первой группе информационных входов коммутатора, вход второго дешифратора подключен.к второй группе информационных входов коммутатора, третья группа информационных входов которого подключена к первым входам эле ментов И второй группы, объединена с выходом второго элемента ИЛИ, гру пой управляющих входов коммутатора и подключена к вторым входам элемен тов И первой группы, выход второго дешифратора подключен к вторым вход элементов И второй группы, выходы к торых подключены соотбетственно к входам второго элемента ИЛИ. Операционный коммутатор содержит дешифратор, группу элементов И и группу элементов ИЛИ, причем группа управляющих входов коммутатора подключена к первым входам элементов И группы и к управляющему входу дешифратора, информационный вход которого подключен к первой и второй группам информационных входов коммутатора, вторая группа информацион ных входов коммутатора подключена к вторым входам элементов И группы, выходы которых подключены к первым входам элементов ИЛИ группы, вторые 4 входы которых подключены к выходу д ; шифратора, а выходы элементов ИЛИ группы подключены к группе информационных выходов и выходу старшего разряда коммутатора соответственно. Информационная магистраль содержит две группы элементов И, два эле мента ИЛИ и регистр, причем первый и второй входы первого и второго элементов ИЛИ подключены к первому и второму управляющим входам магистрали, вход и выход которой подключены соответственно к первым вхо дам и выходам элементов И первой и второй групп, первые входы элементов И второй группы соединены с выходами регистра, входы которого сое динены с выходами элементов И перво группы, вторые входы элементов И первой и второй групп соединены соответственно с выходами первого и эторого элементов ИЛИ. Рассмотрим один из возможных вариантов процессора, когда команда содержит только два операнда. .На фиг.1 представлена структурная схема предлагаемого процессора; на фиг.2 - то же, адресного коммутатора; на Фиг.З - то же, коммутатора ветвлений; на фиг.4 - то же, операционного коммутатора; на фиг,5 то же, регистра состояний, не фиг.б то же, регистра команд; на фиг.7 то же, операционного устройства; на фиг.8 - то же, устройства микропрограммного управления; на фиг.9 то же, информационной магистрали. Предлагаемый процессор ;(фиг.11 содержит регистр 1 команд, регистр 2. состояний и операционное устройство 3, информационную магистраль 4, устройство 5 микропрограммного управления, /адресный коммутатор 6, коммутатор 7.ветвлений, операционный коммутатор 8. Адресный коммутатор (фиг.2) содержит группы 9-11 элементов И, дешифратор 12, группу 13 элементов ИЛИ, группу выходов 14 коммутатора, группы 15-17 информационных входов коммутатора, управляющие входы 18 и 19 коммутатора. КоммутатЪр ветвлений (фиг.З) содержит группы элементов И 20, 21, дешифраторы 22 и 23., элементы ИЛИ 24, 25, группы информационных входов 26 и 27 коммутатора, группа управляющих входов 28-32 коммутатора, группу выходов 33 коммутатора. Операционный коммутатор (фиг.4) содержит дешифратор 34, группу 35 элементов И, группу 36 элементов ИЛИ, группу информационных входов 37 коммутатора, выход 38 старшего раэряда коммутатора, группу информационных выходов 39 коммутатора. Регистр состояний (фиг.5) содержит регистр 40, группу 41 элементов ИЛИ, группы 42-44 элементов И, элемент ИЛИ 45, управляющий вход. 46 регистра, группы информационных входов 47 и 48 регистра, группу выходов 49 регистра. Регистр команд (фиг,6) содержит операционный регистр 50, счетчики 51 и 52, группы элементов И 53-56, группа управляющих входов 57 и 58 регистра. Операционное устройство (фиг,7) содержит ариЛметико-догический блок 59 (АЛБ I, сдвигатель 60, сверхоперативную память 61 (СОП), регистр 62, Устройство микропрограммного управления (фиг,8) содержит группы 6366 элементов И, дешифратор 67, счетчик 68 адреса, пгжять 69 микрокоманд (ПМК), регистр 70 микрокоманд, генератор 71 тактовых импульсов. элементы И 72-75, элемент ИЛИ 76, элемент НЕ 77. Информационная магистраль (фиг. содержит шину 78, регистр 79, груп пы 80, 81 элементов И, элементы ИЛИ 82, 83. Рассмотрим кодирование микроко, манд. Устройство 5 микропрограммного управления процессора выполняет ми рокоманды четырех видов: информаци ные, операционные с непосредственным указанием адреса и микрооперации, операцио.нные с косвенным указанием адреса и. микрооперации, пер дачи управления. Размер слова микрокоманды - 15 двоичных разрядов. В двух старших разрядах слова микрокоманды записы вается код, определяющий ее вид, а также ойределяювдий кодирование остальных разрядов (далее приводится один из возможных вариантов коди- рования). Для информационных микрокоманд содержимое двух старших разрядов есть 00, а в разрядах 0-12 рас полагаются коды микроопераций, под ключающих блоки и устройства проце сора, а также запоминающее устройство (на фиг.1 не показано)к магис . рали 4 (используется унитарное коди рование). Информационные микрокоманды управляют обменом информации между блоками и устройствами проце сора, а также между процессором и внешними устройствами (на фиг.1 не показаны)., Для операционных микрокоманд с непосредственным указанием адреса микроопераций содержимое двух стар ших,разрядов есть 01, в разрядах 0-8 расположен код микроопераций операционного устройства 3, в разрядах 9-12 помещается адрес ячейки памяти 61. Для операционных микрокоманд с косвенным указанием адреса и микро операций содержимое двух старших разрядов есть 10, в двух младших разрядах слова .шкрокоманды содержится номер кода в словаре микроопе раций, зафиксированных в дешифраторе 34 операционного коммутатора 8. Разряд 2 содержит код микрооперации уменьшения на 1 содержимого операндного счетчика 51, а разряд 3то же для счртчика 52. Разряд 9 мик рокоманды определяет, какой из счет чиков будет участвовать в выполне. НИИ микрокоманды, при которой содер жимое одного из этих счетчиков используется в качестве адреса ячейки СОП 61 (если 9-ый разряд содержи ; О, то используется счетчик 51, ес ли 1 - то счетчик 52.), Разряды 4 - 8 и 10 - 12 являются в данном случае нecyшecтвeнн.ми (резервными ). Для микрокоманд передачи управления содержимое двух старших разрядов есть 11, разряды О - 8 содержат адрес памяти 69 в устройстве 5 микропрограммного управления, а разряды 9-12 определяют направление ветвления в коммутаторе 7, т.е. определяют, выбор значения того или иного признака с целью его использования в качестве условия при выполнении передачи управления в устройстве 5. Рассмотрим функционирование блоков и узлов процессора при выполнении отдельных микрокоманд, код которых расположен в регистре 70 устройства 5 микропрограммного управления (Фиг.8). Пусть выполняется одна из информационных микрокоманд. Так как содержимое обоих старших разрядов равно О, то сигнал, образующийся на первом выходе дешифратора 67, поступает на первые входы элементов И в группе 63, в результате чего на группе информационных выходов 46 появятся сигналы, соответствующие кодам микрооперации (разряды О - 12).. При этом сигнал с выхода 12-го разряда через элемент 76 ИЛИ откроет группу 66 элементов И, через элемент 77 НЕ закроет элемент 74 И и по первому управляющему входу обеспечит занесение в счетчик 68 кода адреса, причем его код из разрядов 12 - 15 магистрали 4 через группу 66 элементов И занесется в младшие разряды счетчика 68 (разряды 0-3). Кроме того, сигнал 12-го разряда поступит на вход регистра 1 команд (фиг.6) и обеспечит занесение кода команды в операционный регистр 50 (разряды 8 - 15), счетчик 51 (разря-ды 4 - 7) и счетчик 52 (разряды О 3). Сигнал 7-го разряда откроет группу 53 элементов И, в результате чего содержимое разрядов 10 - 15 регистра 50 поступит на соответствующие разряды магистрали 4, что обеспечивает, например, запоминание кода команды при прерывании. Сигнал 6-го разряда откроет группу 54 элементов И, в результате чего содержимое разрядов 8-9 регистра 50 поступит на соответствующие разряды магистрали 4, что обеспечивает формирование адреса при выполнении команд передачи управления, а также запоминание кода команды при . прерывании. Сигнал 5-го разряда откроет группу 55 элементов И, в результате чего содержимое счетчика 51 поступит на 4-7 разряды магистрали 4, что .обеспечивает возможность формирования константы (в операционном устройстве 3) и формирование адреса (.при выполнении команд передачи управления , а также запоминание кода команды при прерывании. Сигнал 4-го разряда откроет груп пу 56 элементов И, в результате чего содержимое счетчика 52 поступит на 0-3 разряды магистрали 4. Это обеспечивает те же возможности, что и для счетчика 51. Сигнал 3-го разряда по шинам 46 1ФИГ.5) откроет группу 43 элементов и через элемент ИЛИ 45 обеспечит занесение содержимого разрядов 0магистрали 4 через группу входов 48 группу 43 элементов И и группу 41 элементов ИЛИ в регистр 40. Сигнал 2-го разряда по шинам 46 откроет группу 44 элементов И, в результате чего содержимое регистра 40 через группу выходов 49 поступит на О - 3 разряды магистрали 4. Обе эти.информационные микрооперации обеспечивают запоминание состояний процессора,при прерыва, ниях. Сигнал 1-го разряда (фиг.9) чере элемент ИЛИ 82 откроет группу 80 элементов И, в результате чего .информация с магистральных шин 78 бу дет занесена в магистральный регистр 79. Сигнал 0-го разряда через элемент ИЛИ 83 откроет группу 81 элементов И, в результатечего содержи мое магистрального регистра 79 поступит на все 16 магистральных шин Эти информационные микрооперации обеспечивают функционирование самой магистрали 4. .Разряды 8-11 информационной микрокоманды будем считать резервными. Пусть выполняется одна из операционных микрокоманд с непосредствен ным указанием адреса и микрооперации. Так как содержимое обоих старших разрядов микрокоманды в регистре 70 есть 01, то сигнал, образую щийся на четвертом выходе дешифратора 67, по шине 18 открывает группу 35 элементов И 1(Ъиг.4) . В результате содержимое девяти младших разрядоб регистра 70 микрокоманд по шинам 37 через группу 35 элементов поступит в группу 36 элементов ИЛИ При этом восемь младших разрядов (разряды О - 7) через группу выходов 39 поступает в операционное уст ройство 3 - .код микроопераций, а разряд 8 по шине 38 - в регистр сое тонНИИ. Кроме того, выход 0-го разряда группы выходов 39 подсоединен к входу элемента ИЛИ 82 (фиг.91, а выход 1-го разряда - к входу элемента ИЛИ 83. В результате функцио8 ° нирования операционного устройства 3 , код состояний из блока 59. через группу выходов 47 поступает на вход регистра 2 состояний. Сигнал на входе 38 открывает группу 42 элементов И и через элемент ИЛИ 45 обеспечивает занесение кода состояний в регистр 40 (через группу 42 элементов И и группу 41 элементов ИЛИ). Кроме того, сигнал с -выхода 18 поступает на вход адресного коммутатора 6 и открывает группу 11 элементов И. В результате содержимое разрядов 9-12 регистра 70 микроко|манд по цепи: шины 17 - группа 11 элементов И - шины 14 группа 13 элементов ИЛИ, поступает на память 61 операционного устройства 3 - адрес ячейки памяти. Рассмотрим работу операционного устройства 3 (фиг.71. Группа микроопераций, которые устройство 3 выполняет, кодируется 8-разрядным кодом и содержит микрооперации управления памятью 61 (разряды О - 1 It чтение ячейки с выдачей ее содержимого на магистраль 4 (разряд О) и запись информации из сдвигателя 60 (разряд 1), микрооперации управления сдвигателем 60 (разряды 2 - 3): пропуск информации из блока 59 код 111, пропуск со сдвигом влево (код 10), пропуск со сдвигом вправо (код 01) и запрет прохождения информации (код 00), микрооперацию занесения кода в регистр 62 (разряд 4), микрооперации управления блоком 59 (разряды 5 - 7): отрицание кода из магистрали 4 (код 0001, пропуск информации из регистра 62 (код 001), пропуск информации из магистрали 4 (код 010), сложение (код 011), вычитание кода, поступающего из магистрали 4, из содержимого регистра 62 (код 100), логическое умножение (код 101), логическое сравнение (код 110) и логическое сложение (код 111). Подобный набор микроопераций позволяет выполнить любую из микроопераций блока 59 и сдвигателя 60 над содержимым регистра 79 магистрали и регистра 62 с засылкой результата в произвольную ячейку памяти 61, адрес которой определяется кодом на группе входов 14. Кроме того, можно переслать содержимое любой из ячеек СОП 61 в регистр 79 магистрали. Результат ряда микроопераций можно заслать в регистр 62. Таким образом, данный тип микрокоманд обладает несколькими полями с различным кодированием. Так, например, микрокоманда скодом 010110110100110 означает, что по анной операционной микрокомандес непосредственным указанием адреса и микрооперации содержимые магистрального регистра 79 и регистра 62 поступят в АЛБ 59, откуда после выполнения логического умножения ре зультат поступит в сдвигатель 60. Из последнего код, сдвинутый вправо на один разряд, поступает в СОП 61 и записывается в ячейку с адресом 6. При этом код состояний, сформированный в результате выполне ния операции, заносится в регистр 4 Пусть выполняется одна из операционных микрокоманд с косвенным ука занием адреса и микрооперации. Так как содержимое обоих старших разрядов микрокоманды в регистре 70 есть 10, то сигнал, образующийся на третьем выходе дешифратора б 7, открывает элементы И 72, 73 и через выход 19 поступает на вход адресного комму Та тор а 6 и на вход операцио кого .коммутатора 8, подключая их к работе. Операционное устройство 3, (магистраль 4 и регистр 2 состояний работают аналогично. В операционном коммутаторе 8 (фиг.4) имеется дешифратор 34,-содержащий словари микроопераций в виде 9-разрядных кодов. Адрес слова дешифратора 34 состоит из шести разрядов и складывается из 4-разряд -иого кода, определяющего базовый адрес словаря, и двух разрядов, определяющих номер слова в словаре. Базовый адрес словаря подается из операционного регистра 50 (разряды 8 - 11) по шинам 26, Номер слова В словаре (два младших разряда адреса ) -указывается в двух младших разрядах (разряды 0-1) самой микрокоманды и поступает через группу 37 входов операционного коммутатора 8, При поступлении сигнала на вход 19 срабатывает- дешифратор 34 и по заданному адресу формирует . 9-разрядный код, который через груп пу 36 элементов ИЛИ поступает на вы хбды 38 и 39 коммутатора 8. В адресном коммутаторе 6 (фиг.2) имеется дешифратор 12, который по си:Гналу с входа 19 осуществляет стр бирование группы 9 или 10 злемен-: тов И, для чего его первый вход сое динен с младшей из четырех шин груп пы 17 входов, Tve. с разрядом 9. Если этот разряд равен О, то сигнал с первого выхода дешифратора 12 открывает группу 9 элементов И, в результате содержимое операндного счетчика 51 по цепи шины 15 группа 9 элементов И - группа 13 .элементов ИЛИ - выход 14 поступает на адресные входы СОП 61. Если этот разряд равен 1, то сигнал со второго выхода дешифратора 12 открывают группу 10 элементов И, в результате чего содержимое операндного счетчика 52 по цепи шины 16 - rpynпа 10 элементов И - группа 13 элементов ИЛИ и т.д. поступает на адресные входы СОП 61. Таким Образом, в адресном коммутаторе 6 осуществляется выбор того или иного операндного счетчика для использования его содержимого в качестве адреса операнда. Так как элементы И 72, 73 открыты, то при наличии 1 во 2-м разряде регистра 70 микрокоманд срабатывает элемент И 72, сигнал с его выхода 57 уменьшает на 1 содержимое счетчика 51. Если 1 име.ется в 3-ем.разряде регистра 7б, то срабатывает элемент И 73, сигнал с его выхода 58 уменьшает на 1 содержимое счетчика 52. Данный тип микрокоманд позволяет выполнить любую микрооперацию, используя в к-ачестве адресов операнд содержимое любого из операндных счетчиков, а в качестве кода микроопераций - код, вновь сформированный в дешифраторе 34, в качестве адреса для которого используются разряды команд и разряды микрокоманды. Количество операндных счетчиков мо-жет быть увеличено до 16 ( разряды 9 - 12) , причем разряды 4-- 8 микро-. команды являются резервнь1ми. Микрокоманды передачи управления реализуются устройством 5 микропрограммного управления (фиг. 8). Кажды.й цикл исполнения любой микрокоманды состоит из двух тактов, вырабатываемых тактовым генератором 71. По первому такту содержимое ПМК 69, выбранное по адресу на счетчике 68, заносится в регистр 70 микрокоманд. В течение второго такта эта микрокоманда исполняется. Одновременно на второй вход элемента И 74 поступает второй тактовый импульс и, если на входе элемента НЕ 77 сигнал отсутствует (исполняется не микрокоманда передачи управления), то сигнал с выхода элемента И 74 подается на второй управляющий ьход счетчика 68 адреса и увеличивает его содержимое на 1. В ПМК 69 осуществляется выборка по новому адресу. Так продолжается до тех пор, пока на регистр 70 не будет выбрана микрокоманда передачи управления. Пусть выполняется одна из микрокоманд передачи -управления. Так как содержиг ое обоих старших разрядов микрокоманды в регистре 70 есть 11, то сигнал, образующийся на втором выходе дешифратора 67, открывает группы 64, 65 элементов И и поступает на первый вход элемента И 75. Если на вход 33 поступает сигнал, то элемент И 75 срабатывает, образующийся на его выходе сигнал через элемент ИЛИ 76 открывает группу 66 , элементов И и поступает на первый управляющий вход счетчика 68 адреса, обеспечивая занесение кода адреса. В этом случае содержимое девяти младших разрядов регистра 70 микрокоманд разряды 0-8) являет ся адресом и через группу 64 элеме тов И поступает на разряды 7-15 магистрали 4 и содержимое магистрального регистра 79) при этом не изменяется) далее через группы 65, 66 элементов И заносится в счетчик 68 адреса. При этом код с разрядов 12 - 15 магистрали 4 заносится в младшие разряды счетчика 68, а код с разрядов 7-11 магистрали 4 - в старшие разряды счетчика 68 адреса. В результате, например, содержимое 0-го разряда регистра 70 окажется в 4-м разряде счетчика 68, 1-го разряда - в 5-м, 4-го разряда - в 8-м, 5-го разряда - в 0-м, 6-го разряда - в 1-м и 8-го разряда регистра 70 - в 3-м разряде счетчика 68. Одновременно содержимое разрядов 9-12 регистра 70 микрокоманд по шинам 17 поступает, на дешифратор 22 коммутатора 7 ветвлений (фиг.З). В зависимости от поступив шего кода дешифратор 22 формирует сигнал на одном из своих 14-ти выходов, каждый из которых открывает соответствующий элемент И в группе 20. При этом в зависимости от кода анализируются следующие признаки:код 0000 - косвенно задаваемы признак ветвления, значение которо формируется на выходе элемента 25 коды 0001 -1000 - содержимое р гистра 2 состояний, причем инверсные выходы регистра 40 шинами 27 соединены с соответствупщимй входами группы 20 элементов И; коды 1001 - 1010 - прямое и инверсное значения признака равенства нулю содержимого операндного счетчика 51, поступающие через вхо ды 28-29 на соответствующие входы группы 20 элементов И; коды 1011 - .1100 - прямое и и версное значения признака равенств нулю содержимого операндного счетчика 52, поступающие через входы 3 31 на соответствующие входы Группы 20 элементов И; код 1101 - постоянное значени 1, схемно поданное на вход 32 в виде потенциала +4,5 В. ..При совпадении сигналов на обои входах один из элементов И в группе 20 формирует сигнал на своем вы ходе, который через элемент ИЛИ 24 и выход 33 обеспечивает занесение нового кода адреса в счетчик 68, т.е. передачу управления. При этом коды ОбОО - 1100 используются дл /VcnoBHojR передачи управления, код 1101 - для безусловной, а коды 1100 - 1111 являются резервными. Рассмотрим косвенно задаваемый признак ветвления. В этом случае номер анализируемого признака выраба тывается дешифратором 23 и задается разрядами 10 - 12 команды, интерпретируемой выполняемой в настоящий момент микрокомандной условного перехода. Содержимое соответствующих разрядов операционного регистра 50 через группу выходов 26 поступает на дешифратор 23. Последний формирует сигнал на одном из своих выходов , открывая соответствующий элемент И в группе 21. На вторые входы последних поступают прямые и инверсные значения содержимого регистра 2 состояний с группы входов 27. Если сигнал отсюда поступит на тот же элемент И, то на выходе последнего будет сформирован сигнал, который через элемент 25 ИЛИ поступит на вход элемента И группы 20. Если на группе 17 входов в этот момент находится код 0000, то этот сигнал через элемент И группы 20, элемент ИЛИ 24 и выход 33 поступит на вход устройства 5 микропрограммного управления, осуществляя тем самым передачу управления. Таким образом, коды 0001 - 1000 позволяют прямо задавать признак ветвления в коде микрокоманды, а код 0000 косвенно (в коде самой команды). Для уточнения некоторых особенностей взаимодействия узлов и блоков процессора между собой рассмотрим выполнение какой-либо командь-, например, сдвига на 5 разрядов влево содержимого четвертой ячейки СОИ 61 с контролем результата. Пусть команда имеет вид 0010001001000101, где четыре младших разряда 0101 )означают константу сдвига, разряды 7-4 (код 0100) - адрес ячейки СОП 61, а разряды 15-8 являются кодом операции. Выполнение очередной команды в процессоре начинается с информационной микрокоманды 001000000000001. По этой микрокоманде осуществляется занесение кода команды из магистрального регистра 79 в регистр 1 команд, для чего сигнал 12-гр разряда с выходов 46 устройства 5 микропрограммного управления поступит на вход регистра 1 команд, в результате чего в регистр 50 занесется код 00100010, в счетчик 51 - код 0100 и в счетчик 52 - код 0101, Одновременно сигнал с 12-го разряда выходов 46 через элемент ИЛИ 76 откроет группу 66 элементов И, в результате чего содержимое разрядов 15 - 12 кода команды из магистрали 4 занесется в рязряды 3 - О счетчика 68 гщреса (код 0010, определяя первый гщрес (в

остальные разряды занесется код 00000), После выборки содержимого из ПМК 69, соответствующего этому адресу, в регистре 70 оказывается следующая микрокоманда 111101010100101

Так как это есть микрокоманда передачи управления, то сигнал со второго выхода дешифратора 67 открывает группы 64, 65 элементов И и элемент И 75, в результате чего на магистрали 4 оказывается код 010100101000000, который однако не заносится в магистральный регистр 79. Одновременно содержимое разрядов 12-9 поступает с группы выходов 17 устройства 5 микропрограммного управления на группу входов коммутатора 7 ветвлений (код 1101. Осуществляется выборка элемента И в группе 20, связанного другим своим входом свходом 32. В результате на выходе этого элемента формируется сигнал, который через элемент ИЛИ 24 и выход 33 поступает на другой вход элемента И 75, формируя сигнал на его выходе. Этот сигнал через элемент ИЛИ 76 открывает группу 66 элементов И, через элемент НЕ 77 блокирует работу элемента И 74 и по первому управляющему входу поступает в счетчик 68 адреса. При этом 4 старших разряда кода с магистрали 4 (код 0101) занесутся в младшие разряды счетчика 68, а разряды 11-7 кода с магистрали 4 (код 00101 } - в старшие разряды счетчика 68 адреса. В результате в последний занесется код 001010101, .т.е. выборка следующей микрокоманды будет производиться по адресу 125 (адреса восьмеричные/, где расположена сама микропрограмма интерпретации. Такое расположение микропрограмм в ПМК 69 (в начальных адресах памяти хранится таблица адресов начала всех микропрограмм, реализующих выполнение операций) позволяет упростить кодирование команд и, в конечном итоге, может привести к экономии оборудования.

После вьаборки содержимого из ПМК 6 в регистре 70 оказывается микрокоманда (в скобках указан адрес в ПМК) 100000000000000 (125). / Так как это есть операционная микрокоманда с косвенным указанием адреса и микрооперации, то сигнал, образукадийся на третьем выходе дешиф ратора 67, через выход 19 поступает на дешифратор 12 адресного коммутатора 6, Так как на группу 17 входов поступает содержимое разрядов 12-9 регистра 70 микрокоманд, а содержимое 9-го разряда есть О, то сигнал формируется на первом выходе дешифратора 12. Группа 9 элементов И открывается и содержимое операндного счетчика 51 (код 0100)

через шины 15, группу 9 элементов И,

группу 13 элементов ИЛИ и группу 14 выходов задает адрес ячейки СОП 61 операционного устройства 3.

Одновременно сигнал с выхода 19 устройства 5 микропрограммного управления поступает на вход операционного коммутатора 8, запуская дешифратор 34, На группу входов 26 поступает код 0010 (содержимое разрядов 11 - 8 регистра 1 команд), на группу входов 37 - содержимое девяти младших разрядов регистра 70 микрокоманд; причем в двух младших разрядах содержится код 00. В результате на вход преобразователя 34 поступает код 001000, выбирая нулевое слово во втором словаре микроопераций . Пусть оно содержит код 000000001, старший разряд которого через выход 38 блокирует занесение в регистр 2 состояний. Восемь младших разрядов кода через группу 39 выходов поступают на входы операционного устройства 3, в результате чего содержимое четвертой ячейки СОП 6 занесется в магистральный регистр 79

Кроме этого,по второму такту генератор 71 формирует импульс, который через элемент И 74 поступает на второй управляющий вход счетчика 68. адреса, увеличивая его содержимое на 1. После выборки содержимого ПМК 69 в регистре 70 оказывается очередная микрокоманда: 100000000001001 (126). Это тоже операционная микрокоманда с косвенным указанием адреса и микрооперации.. Так как содержимое 3-го разряда есть 1, то на выходе элемента И 73 устройства 5 микропрограммного управления формируется сигнал, который через вход 58

содержимое счетчиуменьшит на

ка 52. Адресный коммутатор 6 будет функционировать аналогично описанному.

Операционный коммутатор 8 будет функционировать также аналогично описанному, но на вход преобразователя 34 поступит код 001001, выбирая первое слово во втором словаре микроопераций. Пусть оно содержит код 001001010, в результате выполнения которого содержимое регистра состояний не изменится, а содержимое магистрального регистра 79 че рез АЛБ 59 поступит на сдвигатель 60, сдвинется в нем на один раряд влево, а затем запишется в четвертую ячейку СОП 61.

Затем в регистре 70 окажется новая микрокоманда: 111100010100101 ((1271. Так как это есть микрокоманда передачи управления, то содержимое разрядов 12-9 (код 1100) по шинам 17 поступит в коммутатор 7 ветвлений. При этом анализируется вход 31j а так как содержимое счетчика 52 не равно нулю (равно четырем ), то на выходе 33 возникает сиг нал. В результате в счетчик 68 адреса заносится код 001010101, так что выборка следующей микрокоманды будет осуществляться по адресу 125 произошла передача управления. Этот цикл из трех микрокоманд будет повторяться до тех пор, пока Содержимое счетчика 52 не станет равным нулю, т.е. еще 4 раза. В последний раз при выполнении микрокоманды передачи управления сигнал на выходе 33 не образуется, передачи управления по адресу 125 не происхо дит и выбирается следующая микрокоманда. После выборки содержимого-ПМК 69 в регистре 70 сказывается очередная микрокоманда 100000000000000 (130) . Эта операционная микрокоманда с кос венным указанием адреса и микрооперации рассматривалась выше (она записана по адресу 125 ), в результате ее выполнения содержимое четвертой ячейки СОП 61 заносится в магистральный регистр 79. Затем в регистре 70 оказывается новая микрокоманда 100000000000010 1131). Это есть операционная микрокоманда с косвенным указанием адреса и микрооперации, так что процессор функционирует аналогично рассмотренному ранее. При этом на адресные входы СОП 61, как и ранее, поступает код адреса четвертой ячей ки, но на вход преобразователя 34 поступит код 001010, выбирая второе слово во втором словаре микроопераций. Пусть оно содержит код 100101110. В результате его выполнения в оп рационном устройстве 3 содержимое магистрального регистра 79 через АЛБ 59 и сдвигатель 60 без изменени запишется в четвертую ячейку СОП 61 Особенностью данного кода является наличие 1 в 9-ом разряде, вследствие чего сигнал с выхода 38 опера ционного коммутатора 8 поступит на вход регистра 2 состояний, разрешая занесение кода состояний в последни Код состояний формируется в АЛБ 59 при выполнении каких-либо микроопераций. Пусть имеется 4 признака сос тояний: UJ, - перенос из 4-го разряд Wj - перенос из 8-го разряда, uijперенос из 16-го разряда. Lo,- равенство нулю кода на сумматоре. Пусть также после пятикратного сдвига влево содержимое четвертой ячейки СОП 61 стало равным нулю. То да АЛБ 59 сформирует признак 014 1 так что код 1000 по шинам 47 и че рез группу 42 элементов И и груп-. пу 41 элементов ИЛИ занесется в регистр 40. Таким образом, набор из пяти мяк рокоманд, размещенных в ПМК 69, пра тически реализовал рассматриваемую команду: содержимое четвертой ячейки СОП 61 сдвинуто влево на 5 разрядов, результат контроля на нольпризнак u заслан в регистр 2 состоя.Далее выполняются действия по выборке следующей команды из управляющей памяти (на фиг.1 не показана). Для этого можно воспользоваться, например, двумя информационными микрокомандами: по первой - увеличить счетчик адреса памяти на 1, по второй - выбрать содержимое соответствующей ячейки памяти и занести его в магистральный регистр 79. Затем можно начать выполнение новой команды, заключающееся в исполнении заданной последовательности микрокоманд. Если, например, следующей коман- . дои будет команда условного перехода по признаку uj 1, то выполнение такой команды будет заключаться в следующем. Пусть она имеет вид 0101111011110010, где 10 младших разрядов означают адрес перехода (13621,а шесть старших - код операции . При выполнении первой информационной микрокоманды 001000000000001 код команды заносится к регистр 1 команд, а 4 старших разряда - в счетчик 68 адреса в устройстве 5 микропрограммного управления. Следующая микрокоманда (безусловная передача) 111101111000010 (005) передает управление по адресу 56. Очередная микрокоманда 11000010100011 является микрокомандой условного перехода. При этом разряды 12-9 (код 0000), из устройства 5 микропрограммного управления поступают на группу 17 входов коммутатора 7 ветвлений, в результате чего прОЕ1еряется косвенно задаваемый признак ветвлений. При этом на группу 27 входов поступает код состояний из регистру 2 (в данном случае код 10000000, а на группу 26 входов - содержимое трех разрядов операционного регистра 50, соответствующее разрядам 12 10 команды. Пусть принята следующая кодировка признаков в дешифраторе 23: 000ooj - 100 001ojj- 101 010. 110 011104- 111 На вход 26 поступает код 111, так что один из элементов И в группе 21 откроется (wJ 1) , образующийся на его выходе сигнал через элемент ИЛИ 25, соответствующий элемент И в группе 20,элемент ИЛИ 24 и выход 33 поступит-на вход устройства 5 микропрограммного управления. В результате в счетчик 68 за- . несется новый адрес - код 000111010

Следующая микрокоманда 000000101110000 (072 I является информационной. В этом случае образующийся на первом выходе дешифратора 67 сигнал откроет группу 63 элементов И, в результате чего на выходах 46 по- 5 явятся соответствующие сигналы. Сигнал с выхода 4-го разряда откроет группу 56 элементов И, сигнал с выхсда 5-го разряда откроет группу 55 элементов И и, наконец, сигнал с вы- 10 хода 6-го разряда откроет группу 54 элементов И. В результате на магистраль будет выдан код 0000001011110010.

Пусть сигнал с 8-го разряда уп равляет занесением нового адреса 5 в счетчик адреса управляющей памяти. Тогда при выполнении следующей микрокоманды произойдет выборка новой команды из ячейки с адресом 1362 и ее код занесется в магист- 20 ральный регистр 79. Затем начнется выполнение этой команды и т.д.

Для реализации какой-либо сложной команды может возникнуть необходимость сложения двух ячеек СОП 61,25 Это достигается последовательностью трех операционных микрокоманд с непосредственным указанием адреса и микрооперации: 010011001011101 означает выборку содержимого третьей 0 ячейки СОП 61 Сс занесением в магистральный регистр 79) и через открытые АЛБ 59 и сдвигатель 60 запись в регистр 62, 010110000000001 означает выборку содержимого шестой ,с ячейки СОП 61 и занесение его в магистральныйрегистр 79 (сдвигатель 60 закрыт), 010010101101110 означает сложение содержимых магистрального регистра 79 и регистра 62 в АЛБ 59, запись результата через крытый сдвигатель 60 во вторую ячейку СОП 61, а также занесение кода состояний в регистр 2 состояний.

Пусть необходимо проанализировать оба операнда в команде, Воспользо- 45 вавшись мусорной ячейкой с номером пятнадца- ь в СОП 61, это можно выполнить за четыре микрокоманды: 000000000100010 означает занесение содержимого операндного счетчика 51 jO в магистральный регистр 79, 011111001011110 означает выборку содержимого регистра 79 и занесение его в регистр 62 через открытые ЛБ 59 и сдвигатель 60 одновремен- с но это содержимое заносится в пятнадцатую ячейку) 000000000010010 значает занесение содержимого опеандного счетчика 52 в магистральый регистр 79; 011111111000010 озачает выполнение операции логичес- ого умножения над содержимыми реистров 62 и 79 с занесением кода остояний в регистр 2 состояний.

Из рассмотренного видно, что выолнение, например, команды сдвига 65

вправо будет отличаться от команды сдвига влево лишь содержанием микроопераций , выбираемых из дешифра тора 34 в операционном коммутаторе 8. Это позволяет все команды, выполняемые процессором, разделить на группы. В группы объединяются те команды, алгоритмы интерпретации которых имеют совпадающие граф-схемы и отличаются друг от друга лишь видом операций, выполняемых операционным устройством 3. Список микроопераций, использует мх при интерпретации какой-либо команды в операционном устройстве 3, образуют операционый словарь этой команды. Код операций в команде ( исключая команды передачи управления имеет два поля В одном из них указывается номер группы,к которой принадлежит данная команда,а в другом - номер операциЬного словаря в дешифраторе 34. В операционных микрокомандах с косвенным указанием адреса и микроопераций указывается лишь порядковый номер соответствующей микрооперации в заданном словаре.

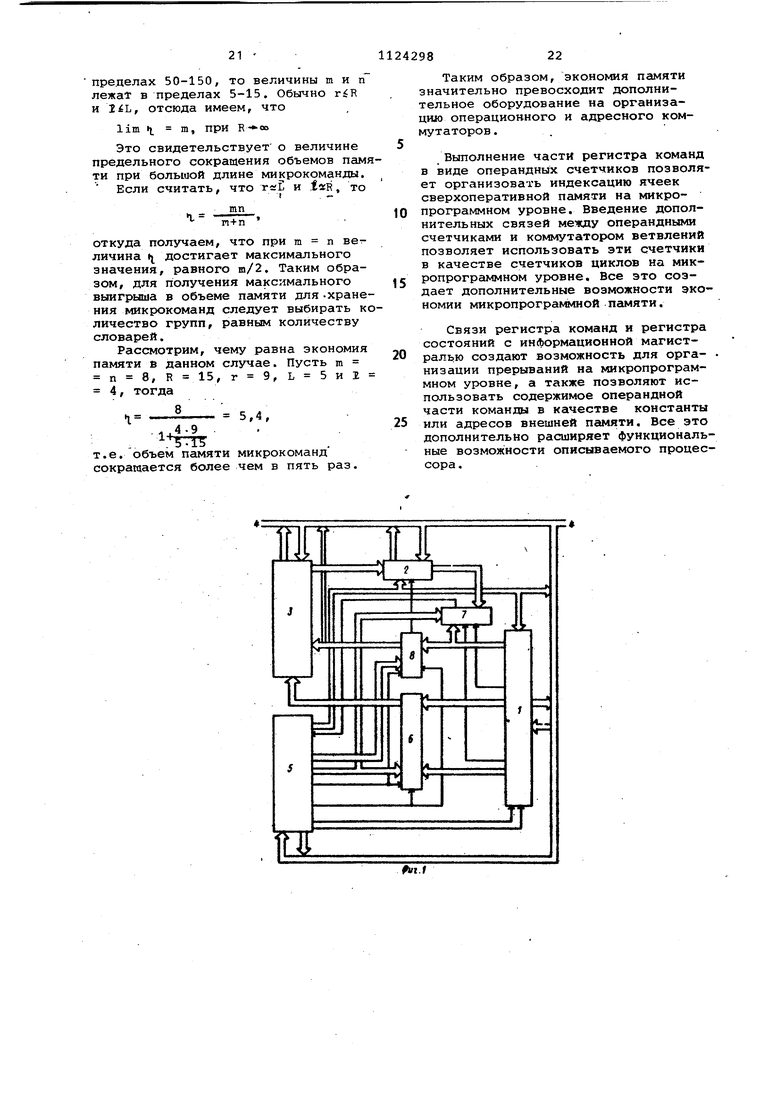

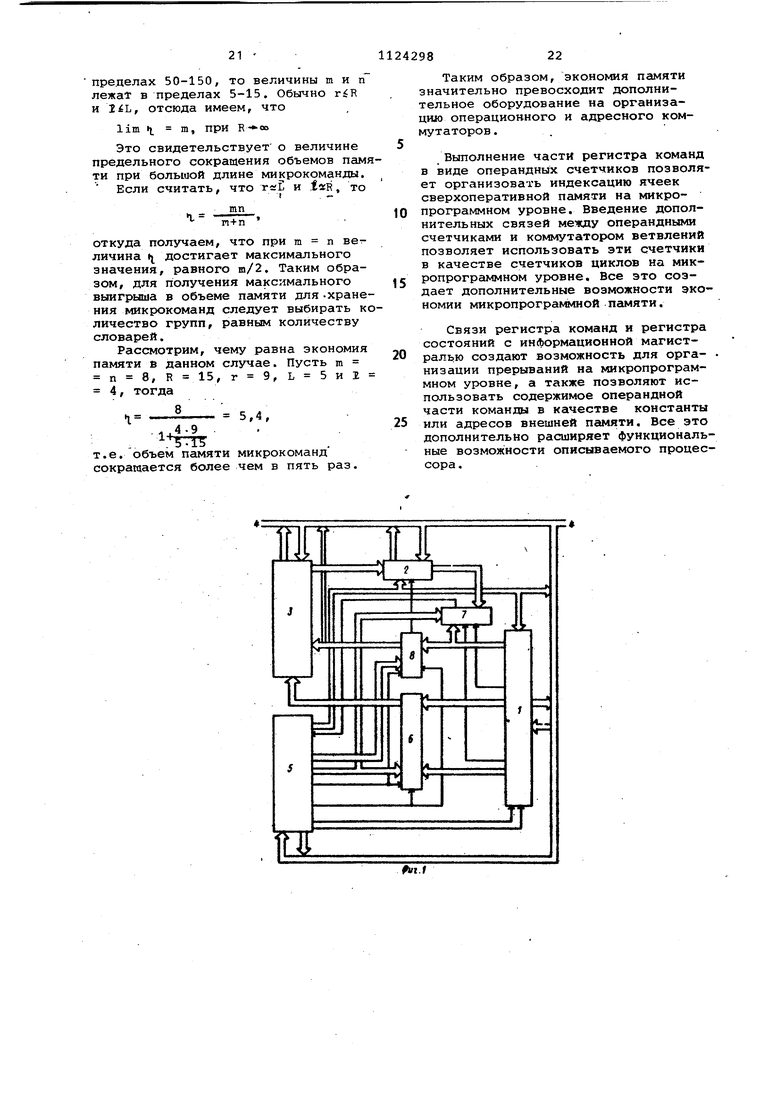

Таким образом, экономия оборудования в-процессоре достигается за счет уплотнения кодирования инфор1мации в памяти микрокоманд устройства 5 микропрограммного управления. Пусть п - количество групп, m количество словарей, R - разрядност микрокоманды, г - разрядность слова в словаре, L - количество микрокоманд в группе и - количество слов в словаре. Для прототипа, т.е. в случае использования традиционной структуры процессора объем памяти микрокоманд есть произведение количества возможных команд на количество микрокоманд, необходимых для реализации каждой из них. Если считать что последняя величина одинакова для всех команд, то объем памяти в битах есть

V mnLR.

В случае использования предлагаемого процессора объем памяти микрокоманд имеет вид

W nLR,

а объем памяти для словарей (считая что дешифратор 34 выполненв виде ПЗУ)

Wj тег, т.е. общий объем памяти есть

W nLR mEr.

Отсюда отношение объемов ерть

у m

г

W

mir

1 nLR

Так как обычно количество операций, выполняемых ЭВМ, находится в

пределах 50-150, то величины тип лежа в пределах 5-15, Обычно riR и , отсюда имеем, что

lim IL т при

Это свидетельствует о величине предельного сокращения объемов памяти при большой длине микрокоманды.

Если считать, что и 1 «R, то

Ч

откуда получаем, что при m п ветличина 1 достигает максимального значения, равного т/2, Таким образом, для получения максимального выигрыша в объеме памяти для -хранения микрокоманд следует выбирать количество групп, равным количеству словарей.

Рассмотрим, чему равна экономия памяти в данном случае, Пусть m п 8, R 15, , 4, тогда

1 5,4,

л . 4 .9

. Т

т,е, объем памяти микрокоманд сокрамается более чем в пять раз.

ПИ

Таким образом, экономия памяти значительно превосходит дополнительное оборудование на организацию операционного и адресного коммутаторов ,

Выполнение части регистра команд в виде операндных счетчиков позволяет организовать индексацию ячеек сверхоперативной памяти на микропрограммном уровне. Введение допол0нительных связей между операндными счетчиками и коммутатором ветвлений позволяет использовать эти счетчики в качестве счетчиков циклов на микропрограммном уровне. Все это соз5дает дополнительные возможности экономии микропрограммной памяти,

Связи регистра команд и регистра состояний с информационной магист0ралью создают возможность для орга- низации прерываний на микропрограммном уровне, а также позволяют использовать содержимое операндной части команды в качестве константы

5 или адресов внешней памяти. Все это дополнительно расширяет функциональные возможности описываемого процессора .

1

оэ

-ЛЗ

13

If

Illr

iT тг irr

1S 18 Ir/r-- Iw

523130 23 28

26

J7

II

О Ш

Риг.2

26

36

jf

ui.ff

ju

Tt If

fh

fS

OJtj

.«

lF

1Ц

f«JC:

fe7

kPfj

2

J

2«

11

I В1 --- во 81 |t1 8S

т ,т Ф

С

:J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Техническое описание, М., 1973 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Preliminary | |||

| KDll-E Processor Manuel | |||

| Digital Eguipment Corporation | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

Авторы

Даты

1984-11-15—Публикация

1982-04-26—Подача