00

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве устройства управления специализированных вычислительных систем. Целью изобретения является увеличение коэффициента использования емкости памяти микрокоманд. Для этого микропрограммное устройство управления содержит первый и второй блоки 1.2 памяти. регистр 3 микрокоманд, формирователь 4 детерминированной последовательности, триггер 10, мультиплексор 11, дешифратор 12, коммутатор 13 и элемент ИЛИ 14. Цель достигается введением дешифратора, элемента ИЛИ, триггера, коммутатора и обусловленных ими связей. 1 з.п. ф-лы. 2 ил.

Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве устройства управления специализированных вычислительных систем.

Целью изобретения является увеличение коэффициента использования емкости памяти микрокоманд путём равномерного размещения микрокомандного базиса в первом и втором блоках памяти.

Сущность изобретения состоит в равномерном распределении микрокомандного базиса в блоках памяти микропрограммного устройства управления. Это достигается за счет разделения множества микропрограмм на два подмножества. При реализации микропрограмм первого подмножества триггер формирователя после выполнения микрокоманд ветвления устанавливается в нулевое состояние, а при реализации микрокоманд второго подмножества - в единичное состояние.

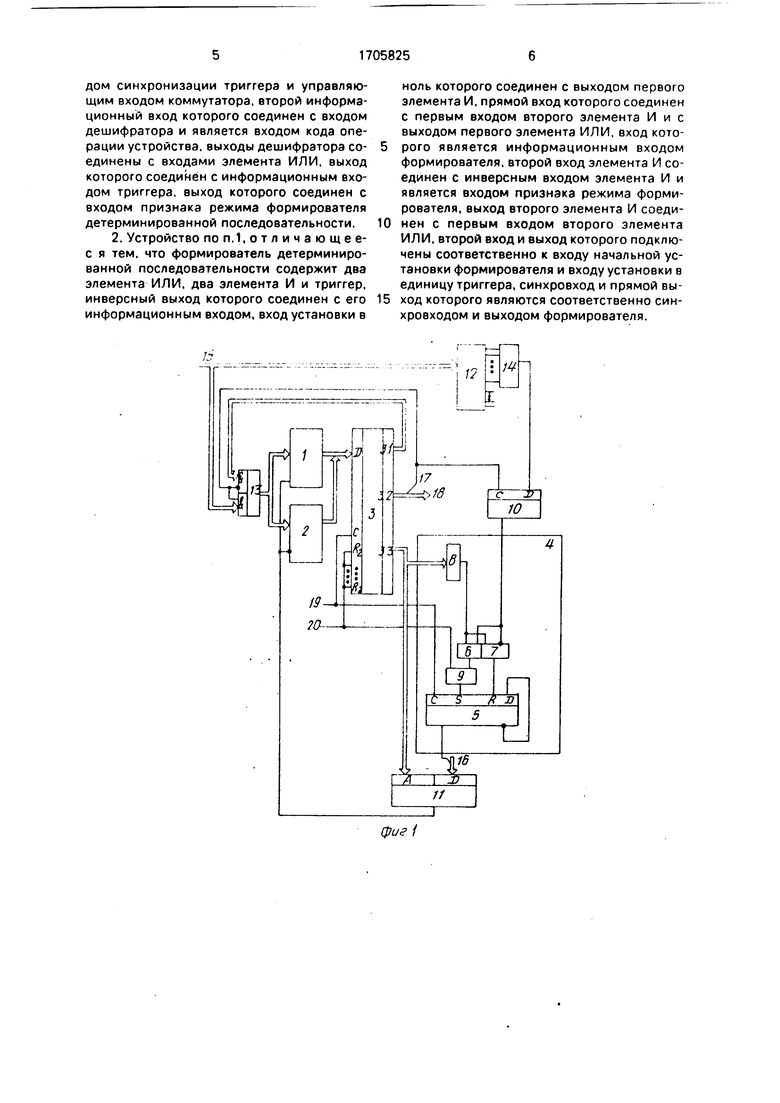

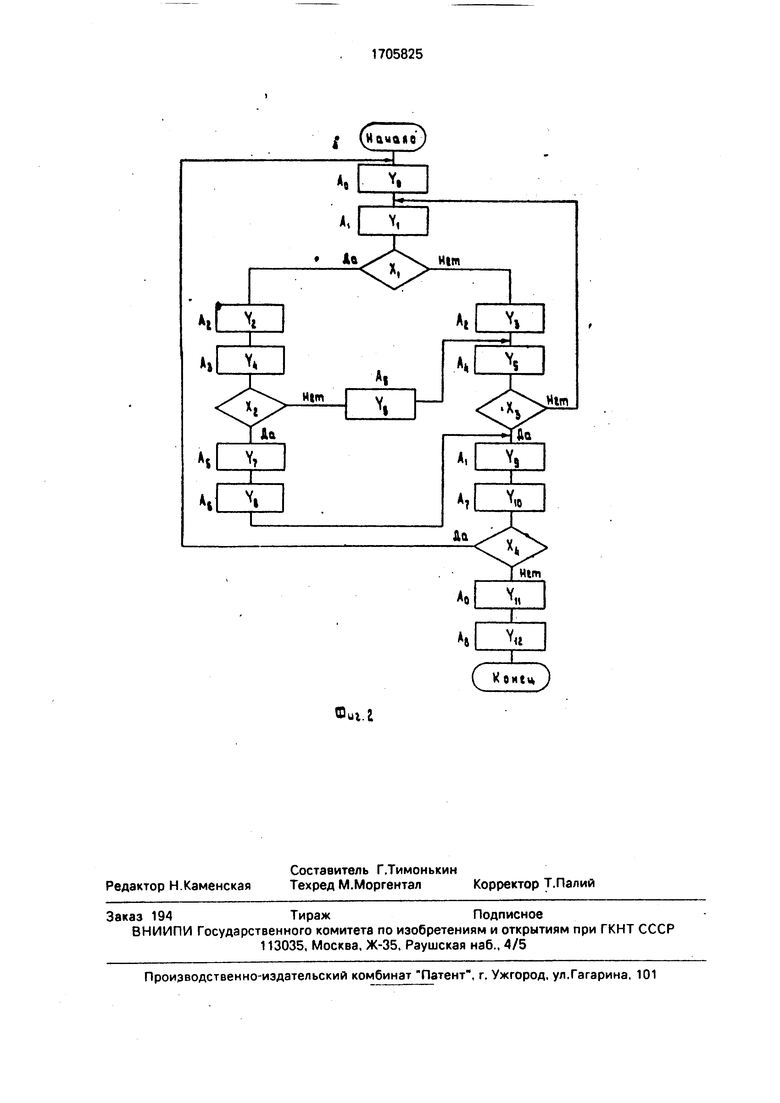

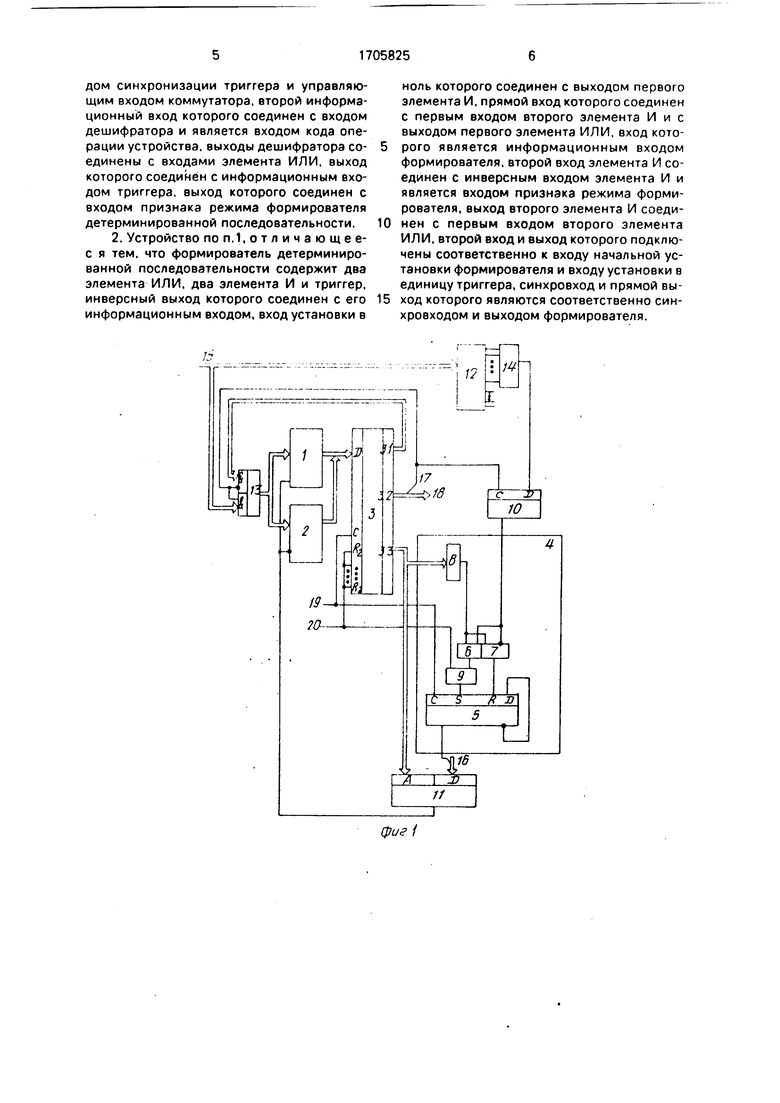

На фиг. 1 приведена функциональная схема микропрограммного устройства управления; на фиг.2 - пример алгоритма.

Микропрограммное устройство управления содержит первый и второй блоки 1, 2 памяти, регистр 3 микрокоманд с выходами 3.1 адреса очередной микрокоманды, выходом 3.2 микроопераций, выходом 3.3 кода проверяемого условия, формирователь 4 детерминированной последовательности, состоящей из триггера 5, элементов И 6 и 7, элементов ИЛИ 8, 9, триггер 10, мультиплексор 11, дешифратор 12. коммутатор 13. элемент ИЛИ 14, вход 15 кода операции, вход 16 сигналов логических условий, выход 17 сигнала микрооперации Конец команды, выход 18 микроопераций устройства, вход 19 синхронизации устройства, вход 20 начальной установки.

ч1

о

СП

со ю ел

ю

Микропрограммное устройство управления функционирует следующим образом.

Перед началом работы по сигналу начальной установки со входа 20 регистр 3 устанавливается в начальное состояние, все триггеры регистра 3 устанавливаются в нулевое состояние за исключением триггера, формирующего сигнал Конец команд на, выход 17, который устанавливается в единичное состояние, триггер 5 устанавливается в единичное состояние. Сигнал с выхода триггера 5 через мультиплексор 11 поступает на блоки 1,2 памяти и открывает блок 1 памяти. Код операции (адрес первой микрокоманды соответствующей микропрограммы) со входа 15 устройства поступает на дешифратор 12 и через коммутатор 13 - на адресные входы блоков 1. 2 памяти. При этом из блока 1 памяти выбирается микрокоманда и поступает на D-вход регистра 3 микрокоманд. По заднему фронту импульса, поступающего со входа 20 устройства, микрокоманда записывается в регистр 3, единичный сигнал на выходе 17 при этом исчезает, а триггер 5 переводится в нулевое состояние. Если выполняемая микропрограмма принадлежит к первому множеству, то на соответствующем выходе дешифратора 12 появляется сигнал. Этот сигнал с выхода элемента ИЛИ ,14 поступает на D-вход триггера 10. По заднему фронту сигнала с выхода 17 триггер Юустанавливается в единичное состояние.

Сигналы микроопераций с выхода 3.2 регистра 3 поступают на выходы 18 устройства, код адреса очередной микрокоманды с выхода 3.1 через коммутатор 13 поступает на адресные входы блоков 1,2 памяти, код проверяемого логического условия с выхода 3.3. блока 3 поступает на элемент ИЛИ 8 и на адресный вход мультиплексора 11. Сигнал на выходе мультиплексора 11 отсутствует, поэтому очередная микрокоманда будет выбираться из блока 2 памяти. По заднему фронту очередного синхроимпульса эта микрокоманда записывается в регистр 3 и триггер 5 переводится в противоположное состояние. Очередная микрокоманда, аналогично описанному выше алгоритму, будет выбираться из блока 1 памяти. Далее устройство будет функционировать аналогично описанному выше алгоритму. Если очередная микрокоманда является микрокомандой ветвления, то на выходе 3.3. будет присутствовать ненулевой код. При этом сигналом с выхода элемента И 6 триггер 5 переводится в единичное состояние. Сигнал проверяемого условия со входа 16 через мультиплексор 11 поступает на блоки 1, 2 памяти. В .зависимости от значения этого

сигнала очередная микрокоманда будет выбираться либо из блока 1 памяти (при единичном значении сигнала), либо из блока 2 памяти (при нулевом значении сигнала).

При выборке этой микрокоманды из блоков 1(2) памяти триггер 5 перейдет в нулевое состояние. Очередная микрокоманда при этом будет выбираться из блока 2 памяти.

0 Если же выполняемая микропрограмма принадлежит ко второму множеству, то перед ее выполнением на выходах дешифратора 12 сигналы будут отсутствовать и на выходе элемента ИЛИ 14 будет нулевой сиг5 нал.

При записи в регистр 3 первой микрокоманды микропрограммы триггера Юустанов- ливается в нулевое состояние. При выполнении линейных микрокоманд уст0 ройство функционирует аналогично описанному выше алгоритму. Если в регистр 3 записывается микрокоманда ветвления, то в процессе ее выполнения триггер 5 устанавливается в нулевое состояние. Микроко5 манда, следующая после микрокоманды ветвления, выбирается либо из блока 1 памяти (при единичном значении проверяемого логического условия), либо из блока 2 памяти (при нулевом значении проверяемо0 го логического условия), а очередная линейная микрокоманда- будет выбираться из блока 1 памяти. Далее устройство функционирует так, как и при выполнении микрокоманд микропрограмм первого подмножества.

5 Таким образом, при выполнении микро-/ программ первого подмножества микрокоманды, следующие после микрокоманд ветвления, выбираются из блока 2 памяти. При выполнении микропрограмм второго

0 подмножества микрокоманды, следующие после микрокоманд ветвления, выбираются из блока 1 памяти. Реализация такого подхода позволяет на этапе проектирования микрокомандный базис равномерно разме5 щать в первом и втором блоках 1, 2 памяти, уменьшать их информационную емкость и сложность устройства в целом, т.е. увеличивать коэффициент использования емкости памяти микрокоманд.

0 Формула изобретении я

5 микрокоманд, оно дополнительно содержит дешифратор, элемент ИЛИ, триггер и ком- - мутатор, первый информационный вход которого соединен с первым выходом регистра, выход сигнала микрооперации Конец команды которого соединен с входом синхронизации триггера и управляющим входом коммутатора, второй информационный вход которого соединен с входом дешифратора и является входом кода операции устройства, выходы дешифратора соединены с входами элемента ИЛИ, выход которого соединён с информационным входом триггера, выход которого соединен с входом признака режима формирователя детерминированной последовательности.

0

ноль которого соединен с выходом первого элемента И, прямой вход которого соединен с первым входом второго элемента И и с выходом первого элемента ИЛИ. вход которого является информационным входом формирователя, второй вход элемента И соединен с инверсным входом элемента И и является входом признака режима формирователя, выход второго элемента И соединен с первым входом второго элемента ИЛИ, второй вход и выход которого подключены соответственно к входу начальной установки формирователя и входу установки в единицу триггера, синхровход и прямой выход которого являются соответственно син- хровходом и выходом формирователя.

| Микропрограммное устройство управления | 1981 |

|

SU964640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1399738A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1992-01-15—Публикация

1990-02-05—Подача