ны с выходами регистра внутренних логических условий, информационный вход которого соединен с выходом кода внутренних логических условий блока памяти микрокоманд, выход признака анализа внутренних логических условий которого соединен с инверсным входом злемента И и со стробирующим входом коммутатора внутренних 4 логических условий, группа упраяляющих входов которого соединена с второй группой выходов дешифратора и с группой входов управления записью регистра внутренних логических условий, вход синхронизагщи которого соединен с выходом элемента И, прямой вход которого соединен с вторым выходом генератора тактовых импульсов ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ,содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, коммутатор адреса, коммутатор внешних логических уело- . ВИЙ, дешифратор, триггер пуска и генератор тактовых импульсов, причем вход кода команды устройства соединен с первым информационным входом коммутатора адреса, выход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, m адресных выходов (т - количество немодифицируемых разрядов адреса следующей микрокоманды) немодифицируемых разрядов которого соединены с соответствующими ш информационными входами второй группы коммутатора адреса, выход кода микроопераций блока памяти микрокоманд соединен с информационным входом регистра микроопераций, выход признака конца команды которого соединен с управляющим входом коммутатора адреса, выход признака конца работы регистра микроопераций соединен с входом установки в ноль триггера пуска, выход которого соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхронизации регистра адреса и регистра микроопераций, выход кода управления внешними устройствами которого является выходом устройства, выход кода логических условий блока памяти микрокоманд соединен с входом дешифратора, первая группа выходов которого соединена с группой (Л управляющих входов коммутатора внешних логических условий, группа информационных входов которого является группой входов логических условий устройства, вход установки в единицу триггера пуска является входом пуска устройства, отличающееся 4 тем, что, с целью сокращения объема ю оборудования, оно содержит регистр 00. внутренних логических условий, комСАд мутатор внутренних логических усло J вий, злемент И и элемент ИЛИ, причем адресньй выход модифицируемого разряда блока памяти микрокоманд соединен с первым входом элемента ИЛИ, выход которого соединен с (т +1)-м информационным входом второй группы коммутатора адреса, второй и третий входы элемента ИЛИ соединены соответственно с выходами коммутатора в нешних логических условий и коммутатора внутренних логических условий, информационные входы которого соедине-

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении центральных устройств управления ЭВМ и вычислительных систем.

Известно микропрограммное устройство управления, содержащее два блока памяти, дешифратор, регистр адреса,- триггер, злемент НЕ, два блока элементов И СО.

Недостатком этого устройства является узкая область применения, обусловленная ограничениями на топологию вьшолняемых микропрограмм.

Известно микропрограммное устройство управления,содержащее регистр адреса, дешифратор, блок памяти микрокоманд, триггер условия, злемент И 2.

Недостатком зтого устройства является низкая экономичность, обусловленная отсутствием специальных технических средств для исключения избыточности блока памяти.

Наиболее близким к предлагаемому по технической сущности и достигаемому зффекту является микропрограммное устройство управления с принудительной адресацией, содержащее триггер пуска, генератор тактовых импульсов, дешифратор логических условий, коммутатор внешних логических условий, постоянное запоминаюгцее устройство (ПЗУ) микрокоманд, регистры адреса и микрокоманд, дешифратор микроопераций, эпемент НЕ, коммутатор адреса, причем вход пуска устройства соединен с единичным входом триггера пуска, выход которого соединен с входом генератора тактовых импульсов, выход которого соединен с

входом считывания постоянного запоминающего устройства микрокоманд, адресный вход которого соединен с выходом регистра адреса, первьш и

второй выходы регистра микрокоманд соединены с входами дешифраторов . внешних логических условий и мирокопераций соответственно,группа выходов которого соединена с выходами устройства, а

выход Конец работы соединен с нулевым входом триггера пуска, выходы дешифратора логических условий сое-, динены с управляющими входами коммутатора внешних логических условий,

входы логических условий устройства соединены с информационными входами коммутатора внешних логических условий, выход которого через злемент НЕ соединен с управляющим входом

коммутатора адреса, выход которого соединен с входом регистра адреса, выход ПЗУ микрокоманд соединен с входом регистра микрокоманд, адресный выход которого соединен с информационными входами коммутатора адреса Сз .

Недостатком указанного устройства является большей объем оборудования ПЗУ микрокоманд, что обусловлено

отсутствием технических средств, позволяющих исключить повторное хранение многократно используемых участков микропрограмм, имеющих разных последователей.

Цель изобретения - сокращение объема оборудования.

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, коммутатор адреса, коммутатор внешних логических условий, дешифратор, триггер пуска и генератор тактовых импульсов, причем вход кода KGмaндьL устройства соединен с первым информационным входом коммутатора адреса, выход .которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, m адресных выходов (т - количество немодифицирузмых разрядов адреса следунщей микрокоманды) немодифицируемых {Разрядов которого соединены с соответствующими п информационными входами второй группы коммутатора.адреса,выход кода микроопераций блока памяти микрокоманд соединен с информационным входом ре гистра микроопераций, выход признака конца команды которого соединен с управляющим входом коммутатора адреса, выход признака конца работы регистра микроопераций соединен с входом установки в ноль триггера пуска, выход которого соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого сое динены соответственно с входами синхронизации регистра адреса и регистр микроопераций, выход кода управления внешними устройствами Которого является выходом устройства, выход кода логических условий блока памяти микрокоманд соединен с входом дешифратора, первая группа выходов которого соединена с группой управляющих входов коммутатора внещних логических условий, группа информационных входов которого является группой входов логических условий устройства, вход установки в единицу триггера пуска является входом пуска устройства, введены регистр внутренних логических условий, коммутатор внутренних логических условий, элемент И и элемент ИЛИ, причем адресный выход модифицируемого разряда блока памяти микрокоманд соединен с первым входом элемента ИЛИ, выход которого соеднней с (т + 1)-м информационным входЬм

второй группы коммутатора адреса, второй и третий входы элемента ИЛИ .соединены соответственно с выходами коммутатора внешних логических условий и коммутатора внутренних логи- 55 ческих условий, информационные входы которого соединены с выходами регистра внутренних логических условий

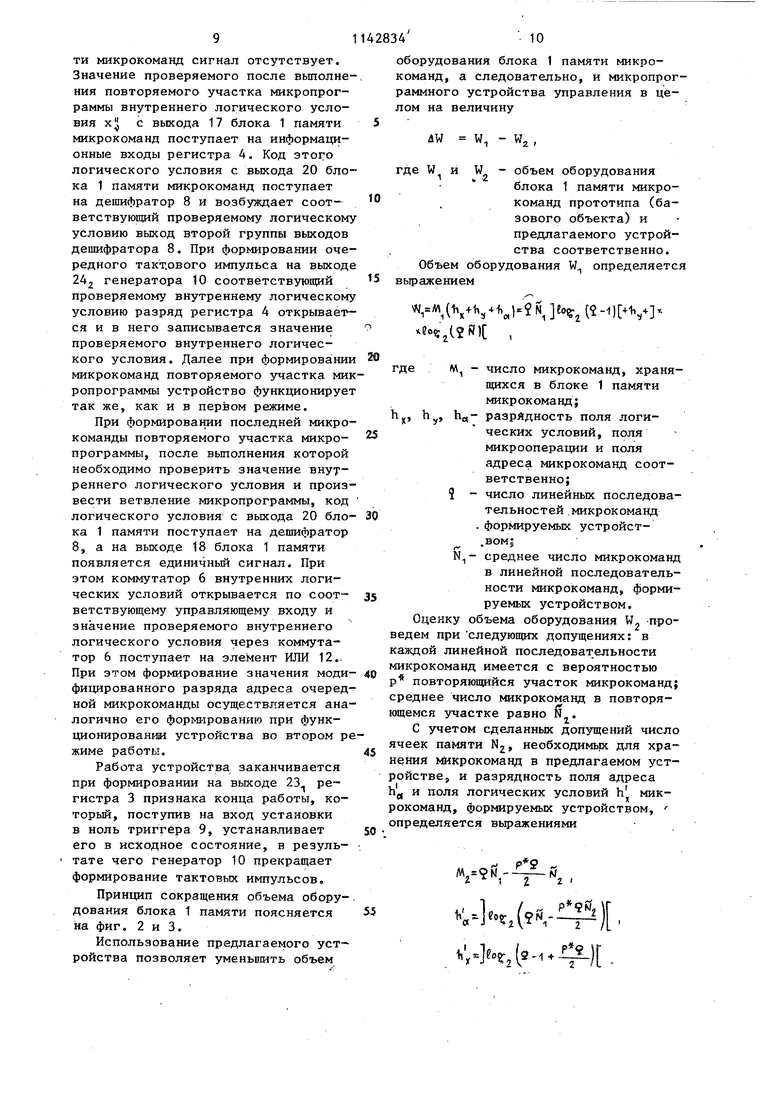

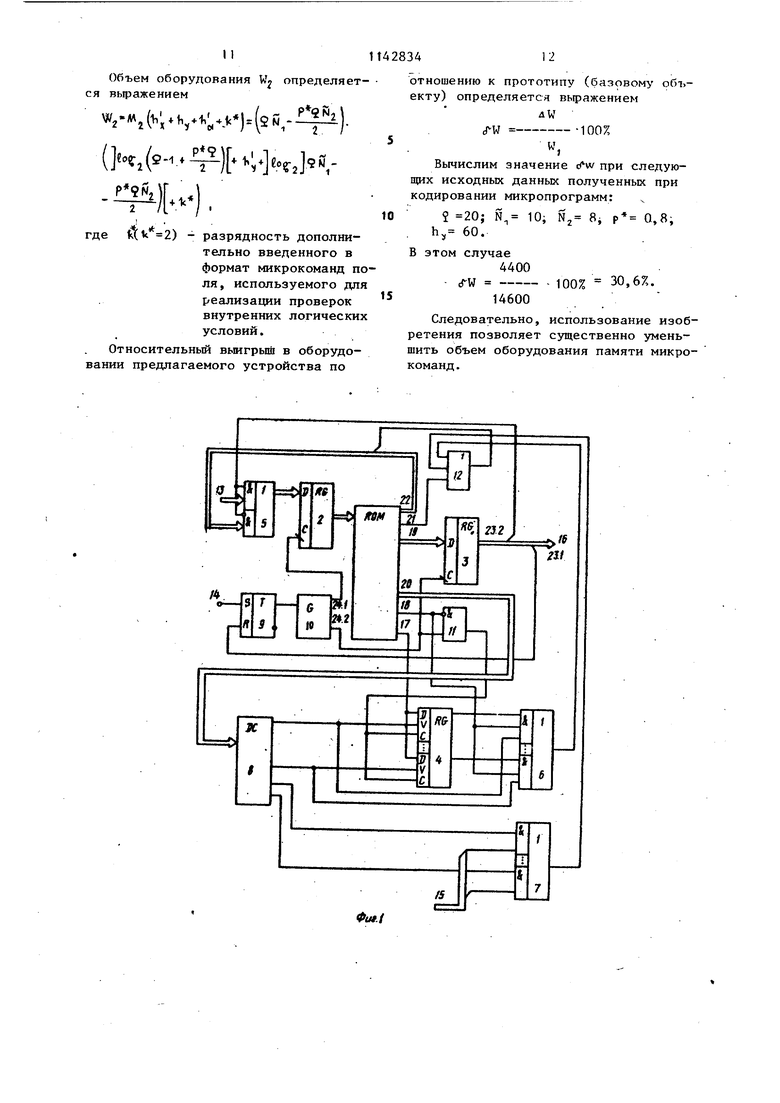

устройства, вход 15 логических условий и выход 16,

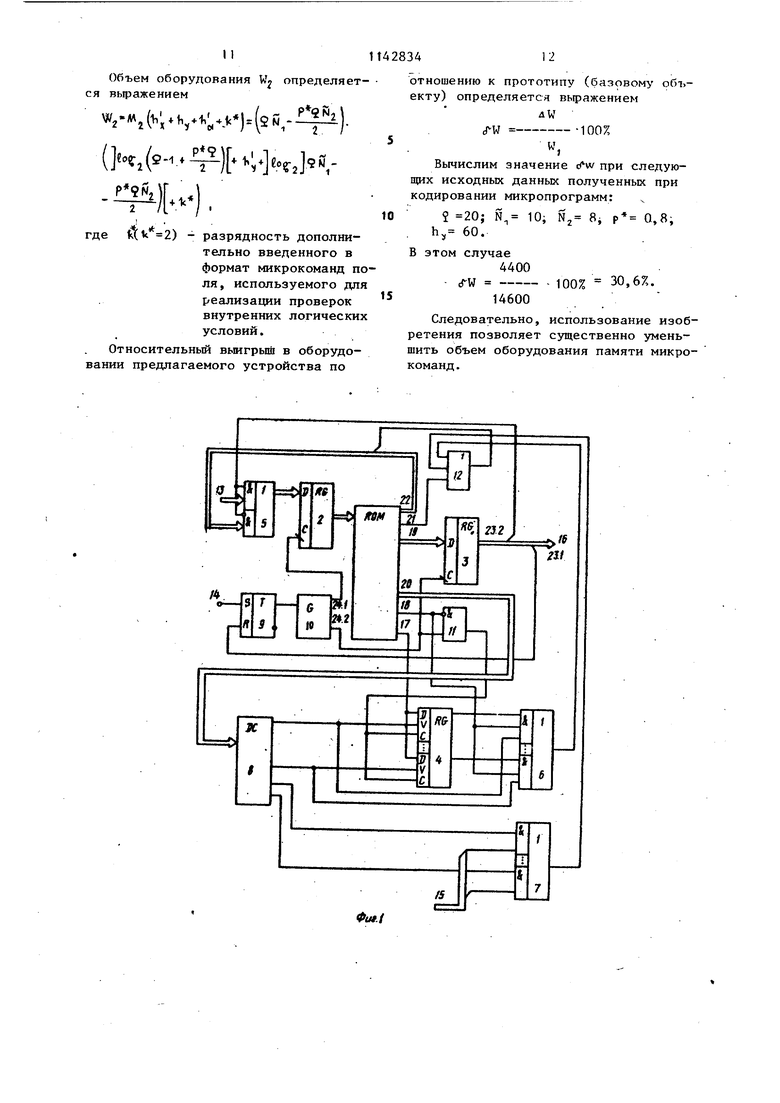

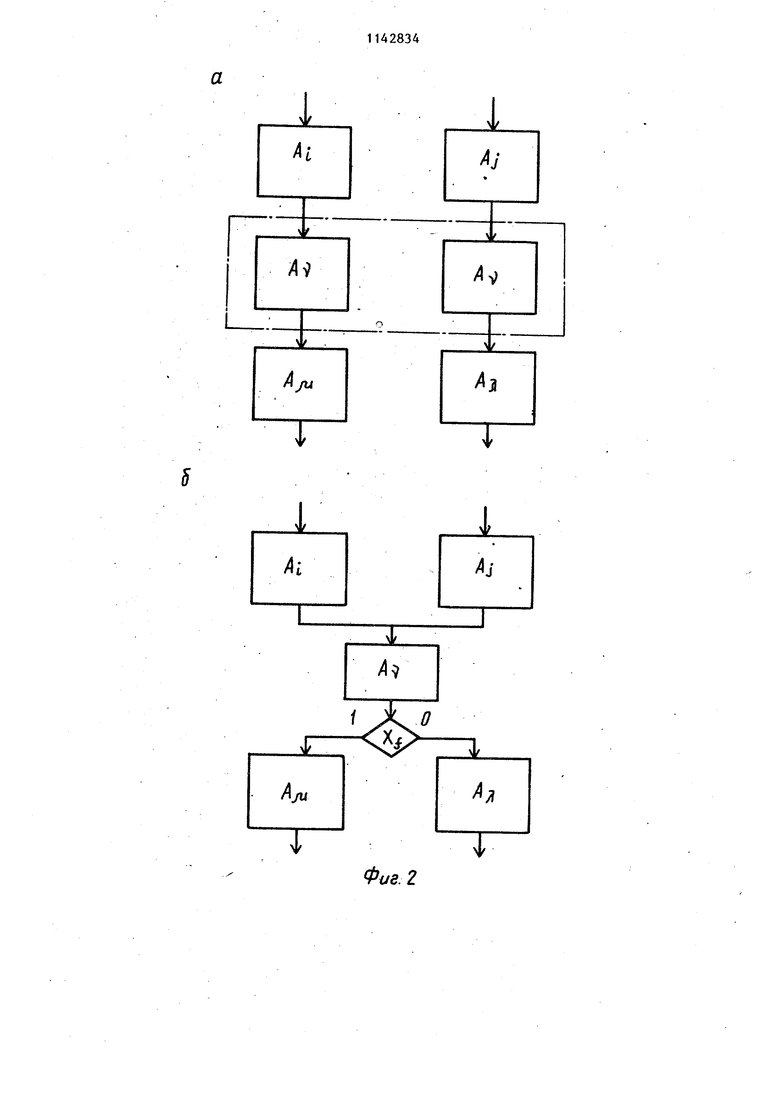

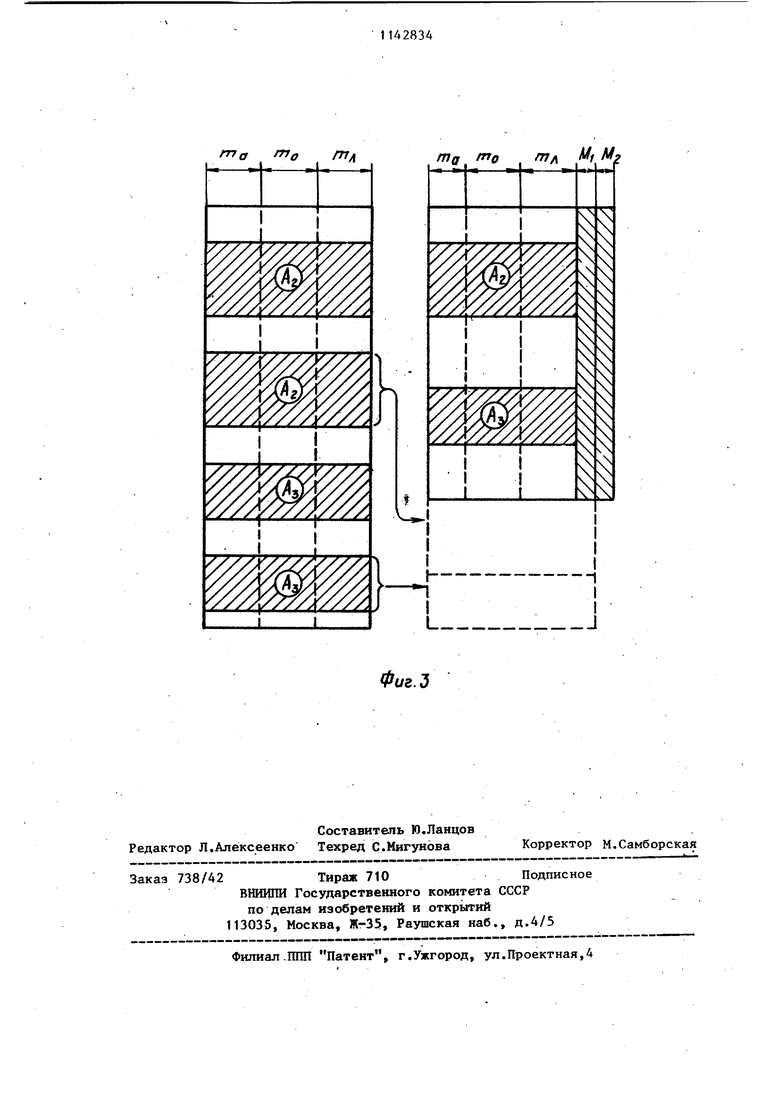

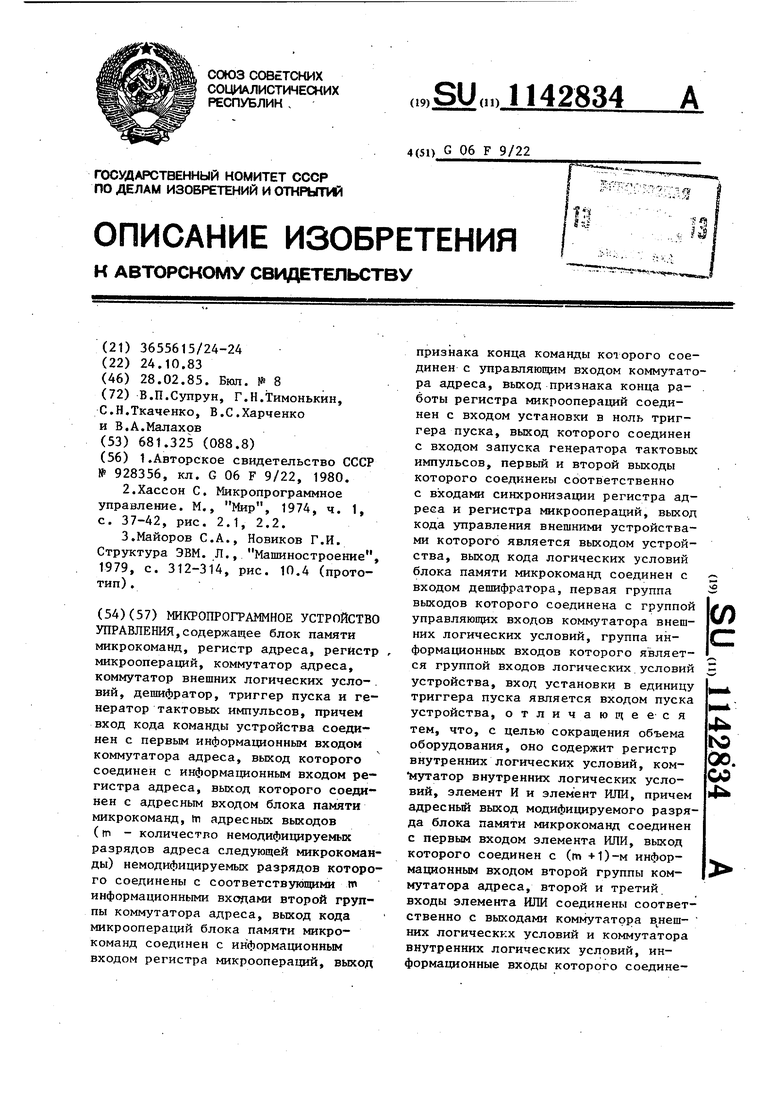

Кроме того, на фиг. 1 показаны выход 17 значения внутреннего логического условия, выход 18 признака анализа внутренних логических уело- , ВИЙ, выход 19 кода микроопераций, выход 20 кода логических условий. информационный вход которого соединен с выходом кода внутренних логических условий блока памяти микрокоманд, выход признака анализа внутренних логических условий которого соединен с инверсным входом элемента И и со стробирующим входом коммутатора внутренних логических условий, группа управляющих входов которого соединена с второй группой выходов дешифратора и с группой входов управления записью регистра внутренних логических условий, вход синхронизации которого соединен с выходом элемента И, прямой вход к.оторого соединен с вторым выходом генератора тактовых импульсов. Сущность изобретения состоит в сокращении объема оборудования памяти микрокоманд путем исключения повторяющихся участков микропрограмм, имеющих разных последователей. Это достигается за счет взедения внутренних логических условий формирования их значений, хранения с использованием специальных технических средств и проверки их после выполнения соответствующих участков микропрограмм. На фиг. 1 приведена функциональная схема предлагаемого микропрограммного устройства управления; на фиг.2фрагмент микропрограммы, реализуемой в прототипе (а) и в предлагаемом устройстве (б); на фиг. поясняется принцип сокращения объема ПЗУ в предлагаемом устройстве (б) по сравнению с прототипом (а). Микропрограммное устройство управления (фиг, 1) содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микроопераций, регистр 4 внутренних логических условий, коммутатор 5 адреса, коммутатор 6 внутренних логических условий, коммутатор 7 внешних логических условий, дешифратор 8, триггер 9 пуска, гене- , ратор 10 TaKTOBbtx импульсов, элемент И 11, элемент ИЛИ 12, вход 13 кода команды устройства, вход 14 пуска выход 21 модифицируемого разряда адреса очередной микрокоманды, выход 2 немодифицируемых разрядов адреса очередной микрокоманды блока 1 памяти микрокоманд, выходы признака конца работы 23 и признака конца команды 23 регистра микроопераций, первый 24 и второй 24 выходы генератора 10 тактовых импульсов. На фиг. 2 и 3 использованы следующие обозначения: А,, А, А;, А,, А, - микроподпрограммы; Хг - логическое условие; m, тп, m - разряд ности адресной и операционной частей и поля логических условий; М и М, - метки, соответствующие выходам 17 и 18 блока 1 соответственно. Рассмотрим функциональное назначение элементов и связей предлагаемо го микропрограммного устройства управления (фиг. 1). Блок 1 памяти микрокоманд предназначен для хранения кодов микрокоман Коммутатор 5 осуществляет передачу на информационный вход регистра 2 адреса либо кода команды, поступающего с входа 13 устройства, либо модифицированного адреса очередной микрокоманды по второму информацион ному входу при единичном или нулево значении сигнала Конец команды на выходе 232 соответственно. Регистр 2 адреса микрокоманд пре назначен для приема, хренения и выдачи кодов адресов микрокоманд в блок 1 памяти микрокоманд. Запись кода адреса очередной микрокоманды в регистр 2 адреса микрокоманд прои водится С; выхода 5 коммутатора при поступлении на синхровход импульса выхода 24, генератора 10 тактовых импульсов. Регистр 3 микроопера1щй предназн чен для приема, хранения и выдачи кодов микроопераций на выхо 16 уст ройства. Запись информации в регист 3 микроопераций осзоцествляется при наличии на его синхровходе сигнала, формируемого на выходе 24 генерато ра 10 тактовых импульсов. Генератор 10 тактовых импульсов на первом 24 и втором 24, выходах формирует последовательности тактовых импульсов, сдвинутых один относительного другого на время записи в регистр 2 адреса очередной микрокоманды и выборки микрокоманды из блока 1 памяти микрокоманд и обеспе чивающих синхронизацию работы устройства. Формирование последовательностей импульсов на выходах ген-оратора 10 тактовых импульсов производится только при наличии единичного сигнала на его управляющем входе. Триггер 9 пуска управляет работой генератора 10 тактовых импульсов. Он устанавливается в единичное состояние при поступлении единичного сиг- , нала на вход 14 пуска устройства, который соединен с его входом установки в единицу, Единичньй сигнал на выходе триггера 9 пуска разрешает функционирование генератора 10 тактовых импульсов. Триггер 9 пуска устанавливается в нулевое состояние при оступлении на его вход установки в ноль сигнала Конец работы,которьй формируется на выходе 23, регистра 3 микроопераций. Коммутатор 7 внешних логических условий осуществляет выделение значения проверяемого внешнего логического условия и вьщачу его на элемент ИЛИ 12. Элемент ИЛИ 12 осуществляет формирование значения младшего разряда адреса очередной микрокоманды и вьщачу его на один из информа1щонных входов коммутатора 5 адреса. Формирование мпадшего разряда адреса ol очередной микрокоманды осуществляется путем реализации функции ctr ci;,v xl V х), где d - значение модифи1шруемого разряда адреса очередной микрокоманды на выходе 21 блока 1 памяти микрокоманд;х . - значение проверяемого внутреннего логического условия на выходе коммутатора 6 внутренних логических условий;Х - значение проверяемого внешнего логического условия на выходе коммутатора 7 . внешних логических условий. Элемент И 11 предназначен для управления записью проверяемого внутреннего логического условия в регист р 4 внутренних логических условий. Регистр 4 внутренних логических условий служит для записи, хранения и вьздачи значений внутренних логических условий на информационные входы коммутатора 6 внутренних логических условий. Коммутатор 6 внутренних логических условий осуществляет вьщеление значения проверяемого внутреннего логического условия и вьщачи его на элемент ИЛИ 12 для модификации адреса очередной микрокоманды. Микропрограммное устройство управ ления работает следующим образом. В исходном состоянии все элементы схемы находятся в нулевом состоянии, а в разряде регистра 3 микрооперации соответствующем признаку конца команды (выход 23j), записана единица (цепи начальной установки условно не показаны). По сигналу Пуск, поступающему через вход 14 устройства на вход установки в единицу триггера 9, последний устанавливается в единичное состояние. При этом на выходах 24, и 24 генератора 10 возбуждаются последовательности тактовых импульсов По первому тактовому импульсу, по ступающему на синхровход регистра 2 адреса, последний открывается. При этом код команды, являюпщйся адресом первой микрокоманды выполняемой микропрограммы, через коммутатор 5 поступает на информационньш вход регистра 2 адреса. По записанному адре су в регистре 2 адреса, в блоке 1 памяти микрокоманд выбирается соот ветствующай микрокоманда и поступает на его выходы 17-22. При наличии сигнала на синхровходе регистра 3. микроопераций операционная часть микрокоманды с выхода 19 микроопераций поступает на информационный вход регистра 3 микроопераций. Сигналы микроопераций с регистра 3 поступают на выход 16 устройства. При формировании адреса очередной микрокоманды возможны три режима работы устройства: 1) формирование адреса очередной микрокоманды при выполнении линейных участков микропрограмм (проверка внутренних и внешних логических условий не осуществля ется) ; 2) формирование адреса очеред ной микрокоманды при проверке внешних логических условий; 3) формирова ние адреса очередной микрокоманды при проверке внутренних логических условий. Рассмотрим работу устройства в этих режимах. Первьш режим. При считывании микрокоманды из блока 1 памяти микрокоманд адрес очередной микрокоманды формируется следующим образом. Немодифицируемая часть адреса очередной микрокоманды с выхода 22 поступает на информащюнные входы второй группы коммутатора 5 адреса. Значение модифицируемого разряда адреса очередной микрокоманды-поступает с выхода 21 блока 1 памяти микрокоманд через элемент ИПИ 12 на один из информационных входов второй группы коммутатора 5 адреса. Поскольку сигнал признака конца команды отсутствует, адрес очередной микрокоманды через коммутатор 5 адреса поступает на информационный вход регистра 2 адреса. При формировании на выходе 24 генератора 10 очередного тактового импульса адрес микрокоманды записывается в регистр 2 адреса. Далее устройство функционирует в этом режиме аналогичным образом. Второй режим. Если при выполнении текущей микрокоманды необходимо проверить значение внешнего логического условия и произвести ветвление микропрограммы, то на выходе 20 блока 1 памяти микрокоманд считывается код этого логического условия. Этот код поступает на дешифратор 8 и возбужда- ет соответствующий проверяемому логическому условию выход первой группы выходов дешифратора 8. Значение проверяемого внешнего логического условия с входа 15 через коммутатор 7 внешних логических условий поступает на элемент ИЛИ 12. Формирование значения модифицированного разряда адреса очередной микрокоманды, осуществляется на элементе ИЛИ 12 путем реализации логической функции cLg ( ) значение которой поступает на один из информационных входов второй группы коммутатора 5 адреса. Далее устройство функционирует аналогичным образом. Третий режим. Запись значения внутреннего логического условия х , в регистр 4 осуществляется следующим образом. При считывании последней микрокоманды фрагмента микропрограммы, после выполнения которого должен выполняться повторяемый участок микропрограммы, на выходе блока 1 памяти микрокоманд сигнал отсутствует. Значение проверяемого после выполнения повторяемого участка микропрограммы внутреннего логического условия х с выхода 17 блока 1 памяти микрокоманд поступает на информационные входы регистра 4. Код этого логического условия с выхода 20 блока 1 памяти микрокоманд поступает на дешифратор 8 и возбуждает соответствующий проверяемому логическому условию выход второй группы выходов дешифратора В. При формировании очередного такт.ового импульса на выходе 24 генератора 10 соответствующий проверяемому внутреннему логическому условию разряд регистра 4 открывается и в него записывается значение проверяемого внутреннего логического условия. Далее при формирова нии микрокоманд повторяемого участка микропрограммы устройство функционирует так же, как и в первом режиме.

При формировании последней микрокоманды повторяемого участка микропрограммы, после вьшолнения которой необходимо проверить значение внутреннего логического условия и произвести ветвление микропрограммы, код логического условия с выхода 20 блока 1 памяти поступает на дешифратор 8, а на выходе 18 блока 1 памяти появляется единичный сигнал. При этом коммутатор 6 внутренних логических условий открывается по соответствующему управляющему входу и значение проверяемого внутреннего логического условия через коммутатор 6 поступает на элемент ИЛИ 12.. При этом формирование значения модифицированного разряда адреса очередной микрокоманды осуществляется аналогично его формированию при функционировании устройства во втором режиме работы,

Работа устройства заканчивается при формировании на выходе 23 регистра 3 признака конца работы, которьй, поступив на вход установки в ноль триггера 9, устанавливает его в исходное состояние, в результате чего генератор 10 прекращает формирование тактовых импульсов.

Принцип сокращения объема оборудования блока 1 памяти поясняется на фиг. 2 и 3.

Использование предлагаемого устройства позволяет уменьпшть объем

оборудования блока 1 памяти микрокоманд, а следовательно, и микропрограммного устройства управления в целом на величину

W, - W ,

dW

где W и W объем оборудования

блока 1 памяти микрокоманд прототипа (базового объекта) и предлагаемого устройства соответственно. Объем оборудования W определяетс

вьфажением

х4,( н ь (-i).() ,

где м - число микрокоманд, хранящихся в блоке 1 памяти микрокоманд;

hjj, hy, Ьд- разрядность поля логических условий, поля микрооперации и поля адреса микрокоманд соответственно;

9 - число линейных последовательностей .микрокоманд . формируемых устройст .вом;

среднее число микрокоманд в линейной последовательности микрокоманд, формируемых устройством. Оценку объема оборудования W, проведем при следующих допущениях: в каждой линейной последовательности микрокоманд имеется с вероятностью Р повторяющийся участок микрокоманд; среднее число микрокомавд в повторяющемся участке равно N.

С учетом сделанньк допущений число ячеек памяти N, необходимьк для хранения 1 крокоманд в предлагаемом устройстве, и разрядность поля адреса Ьд и поля логических условий h микрокоманд, формируемых устройством, определяется выражениями и Объем оборудования W определяется выражением W,.MjV,.b,.i,.n)(26,-). (K(9H..-).ecfj9M. )где 2) - разрядность дополнительно введенного в формат микрокоманд п ля, используемого дл реализации проверок внутренних логически условий. Относительный вьигрыш в оборудовании предлагаемого устройства по 41 отношению к прототипу (базовому объекту) определяется выражением дУ rw -100% Вычислим значение при следующих исходных данных полученных при кодировании микропрограмм: 20; N, 10; N2 8 Р 0,8, hy 60. В этом случае . w 100% 30,6%. 14600 Следовательно, использование изобретения позволяет существенно уменьшить объем оборудования памяти микрокоманд.

Фиг 2

т 0 т о /77yf

то т А 1 2

тд

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное управление | |||

| М., Мир, 1974, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| З.Майоров С.А., Новиков Г.И | |||

| Структура ЭВМ | |||

| Л., Машиностроение, 1979, с | |||

| Способ обработки шкур | 1921 |

|

SU312A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1985-02-28—Публикация

1983-10-24—Подача