ного регистра соединена с группой формационных входов блока памяти, 1129613 ин- товый вход устройства соединен с тактак- товым входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168940A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

УСТРОЙСТВО АДРЕСАЦИИ МНОГОПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ, содержащее блок элементов И-ИЛИ, буферньй регистр, блок памяти, блок элементов И, сумматор, первая группа входов сумматора подключена к группе выходов блока памяти, отличающееся тем, что, с целью . расширения функгрюнальных возможностей за счет формирования адресов команд, реализующих множество рабочих программ для множества локальных вычислителей, в него введен блок микропрограммного управления, состоящий из триггера, генератора импульсов, адресного регистра, накопителя микропрограмм и регистра микрокоманд, восемь выходов которого соединены соответственно с управляющим входом буферного регистра, управ.ляющими входами записи и чтения блока памяти, с управляющим входом блока элементов И, с входом младшего раэ ряда сумматора, с обнуляющим входом триггера и с первым и вторым сигнальными выходами устройства, информационные входы регистра микрокоманд подсоединены к информационньм выходам накопителя /микропрогрш4м, два разрядных выхода которого связаны с первым и вторым управляющими входами блока элементов И-ИЛИ, группа выходов блока элементов ИЧ1ЛИ соединена с группой входов буферного регистра, группа выходов которого соединена с группой информационных входов блока элементов И, группа выходов которого соединена с второй группой входов сумматора, группа выходов которого соединена с первой группой входов блока элементов И-ИЛИ и с группой выходов устройства, вторая группа входов блока элементов И-ИЛИ (Л соединена с группой информационных входов устройства и с первой группой с информационных входов адресного регистра, вторая группа информационных входов которого соединена с первой группой адресных выходов накопителя гдакропрограмм, вторая группа выходов ;О которого соединена с первой группой адресных входов блока памяти, э вторая группа адресных входов которого соединена с группой кодовых входов устройства, единичный выход 9 триггера соединен с сбросовыми входами буферного регистра, регистра микрокоманд и с первым синхровходом адресного регистра и с входом запуска генератора импульсов, прямой выход которого соединен с вторым синхровходом адресного регистра, инверсный выход генератора импульсов связан с синхровходом регистра микрокоманд, выходы адресного регистра соединены с группой адресных входов накопителя микропрограмм, группа выходов буфер

1

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных и многопрограммных вычислительных системах и комплексах.

Известно многопрограммное устройство управления.памятью многопроцессорной вычислительной системы, содержащее блок приема информации, блок памяти, блок классификации запросов, блок упаковки командного слова EI

Недостатком такого устройства является сравнительно ограниченные функциональные возможности, не поз олякщие формировать адреса сразу для нескольких рабочих программ, реализуемых несколькими процессорами.

Наиболее близким по технической сущности к изобретению является устройство для формирования адресов ЦВМ, содержащее первый коммутатор, регистр команд, дешифратор кода операций, децифратор адресу, блок элементов И, дешифратор микроопераций, генератор тактовых импульсов, сумматор, буферный регистр, блок памяти, регистр реконфигураций, второй коммутатор, дешифратор реконфигураций, причем первый вход первого коммута,тора является информационным выходом устройства, второй выход первого коммутатора соединен с первым информационным входом регистра команд и с первым входом блока памяти,первый и вто рой разрядные выходы регистра команд соединены соответственно с первым и вторым входами дешифратора кода операций, третий разрядный выход регистра команд соединен с входом дешифратора адреса, четвертый разрядны| выход регистра команд соединен с пер вым входом блока элементов И, выход дешифра-цора кода операций соединен с п ервым входом дешифратора микроопераций-, выход дешифратора адреса соединен с вторым входом дешифратора, микроопераций, первьй выход блока элементов И соединен с первым входом

сумматора, группа выходов генератора тактовых импульсов соединена с группой управляющих входов дешифратора микроопераций, первый выход дешифратора микроопераций соединен с первым входом буферного регистра, второй вход которого соединен с выходом сумматора, второй вход сумматора соединен с выходом блока памяти, выход буферного регистра соединен с вторым входом первого коммутатора, а первый выход второго коммутатора соединен с вторым входом блока памяти, второй выход блока элементов И соединен с первым входом второго коммутатора, второй вход второго ком1 татора соединен с выкодом дешифратора реконфигураций, группа разрядных выходов регистра реконфигураций соединена с группой входов дешифратора реконфигураций, управляющий вход дешифратора реконфигураций является первым управляющим входом устройства, информационный вход регистра реконфигураций соединен с вторым выходом первого коммутатора, второй вход сумматора является вторым управляющим входом устройства, разрядный выход регистра конфигурации соединен с вторым информацио;;кым входом регистра команд и с третьим входом дешифратора микроопераций, второй выход дешифратора микроопераций соединен с третьим входом блока памяти и с третьим входом первого коммутатора 2 ,

Недостатками известного устройства являются сравнительно узкие функциональные возможности, узость класса решаемых задач и сравнительно большие затраты реализующего оборудования

Цель изобретения - расширение функциональных возможностей за счет формирования адресов команд, реапизующих множество рабочих программ для множества локальных вычислителей.

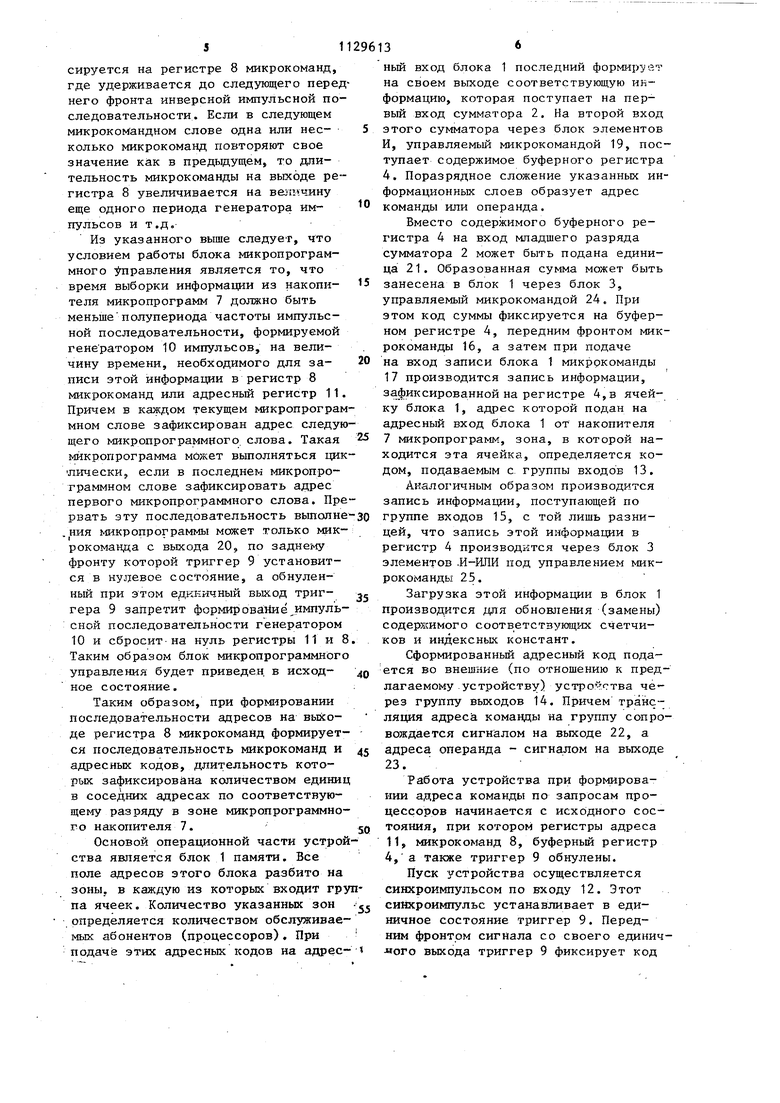

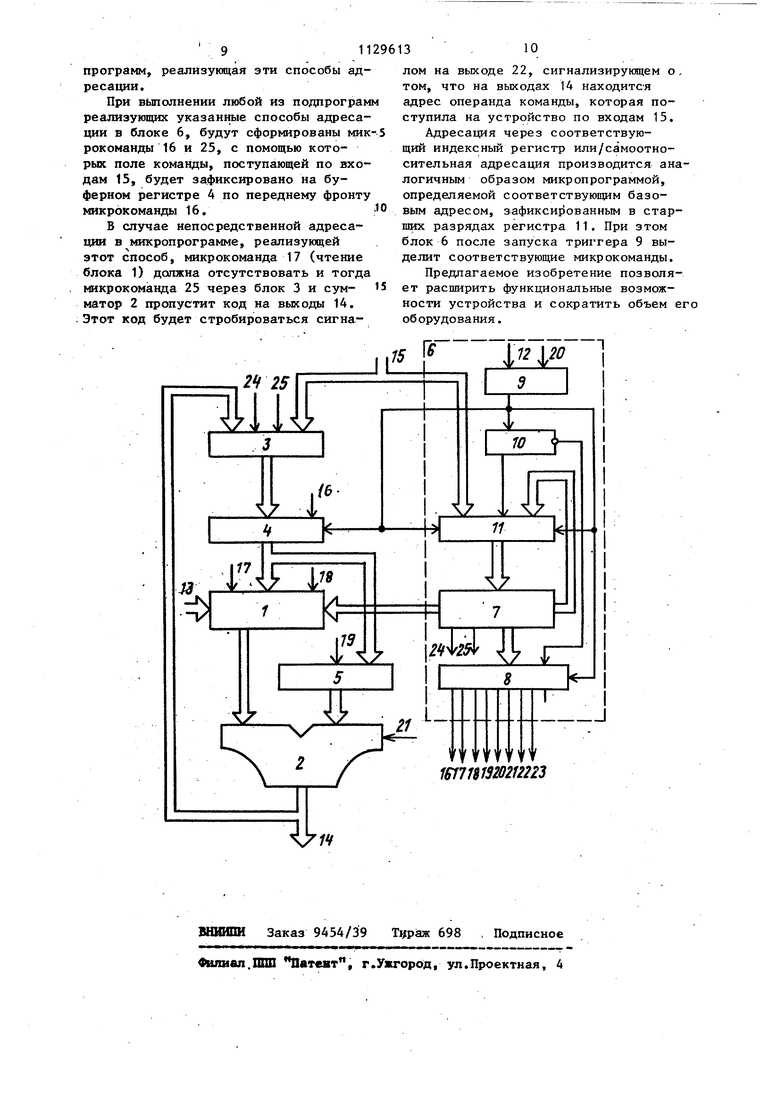

Поставленная цель достигается тем, что в устройство адресации многопроиессорной вычислительной нашины, содержащее блок элементов И-ИЛИ, буфер ный регистр, блок памяти, блок элементов И, сумматор, первая группа входов сумматора подключена к группе выходов блока памяти, введен блок MtycponporpaMMHoro управления, состоя щий из триггера, буферного.импульсов, адресного регистра, накопителя микропрограмм и регистра микрокоманд восемь выходов которого соединены Соответственно с управляющим входом -буферного регистра, управляющими вХо I. дами записи и- чтения блока памяти, с управляющим входом блока элементов И, с входом младшего разряда сумматора, с обнуляющим входом триггера и с первым и вторым сигнальньми выходами устройства, информационные входы регистра микрокоманд подсоединены к информационным выходам накопителя микропрограмм, два разрядных выхода которого связаны с первым и вторым управляющими входами блока элементов И-РШИ, группа выходов блока элементов И-ИЛИ соедине«а с группой входов буферного регистра, группа выходов которого соединена с группой информационных входов бло- ка элементов И, группа выходов которого соединена с второй группой входов сумматора, группа выходов которого соединена с первой группой входов блока элементов И-ИЛИ и с группой выходов устройства, вторая группа входов блока элементов И-ИЛИ соединена с группой информационных входов устройства и с первой группой ин формационных входов адресного регист ра, вторая группа информационных вхо дов которого соединена с первой груп пой адресных выходов накопителя микропрограмм, вторая группа выходов которого соединена с первой группой адресных входов блока памяти, вторая группа адресных входов которого соединена с группой кодовых входов устройства, единичный выход триггера со динен с сбросовыми входами буферного регистра, регистра микрокоманд и с первым синхровходом адресного регист ра и с входом запуска генератора имцульсов, прямой выход которого соеди нен с вторьпу синхровходом адресного регистра, инверсный выход генератора импульсов связан с синхровходом регистра микрокоманд, выходы адресного регистра соединены с группой адресных входов накопителя микропрограмм, группа выходов буферного регистра соединена с группой информационных входов блока памяти, тактовый вход устройства соединен с тактовым входом триггера. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит блок 1 памяти, сумматор 2, блок 3 элементов И-ИЛИ, буферный регистр 4, блок элементов И 5, блок 6 микропрограммного управления. Блок 6 микропрограммного управления включает в себя накопитель 7 микропрограмм, регистр 8 микрокоманд, триггер 9, генератор 10 импульсов, адресный регистр 11, тактовый вход 12 устройства, группу кодовых входов il3 устройства, группу выходов 14 yci:lройства, группу информационных .15 устройства, сигналы на выходах микрокоманды 16-21 регистра 8 микрокоманд, сигнальные выходы 22 и 23 устройства, сигналы с выходов накопителя - микрокоманды 24 и 25, Блок 6 микропрограммного управления обеспечивает формирование микрокоманд, управляющих работбй устройства. Основой блока микропрограммного управления является накопитель 7 микропрограмм, представляющий собой постоянное или полупостоянное запоминающее устройство, в ячейках которого зафиксированы микропрограммные слова. Каждой из ячеек соответствует свой адрес, подаваемый на адресный вход накопителя 7 микропрограмм с выхода адресного регистра 11. Синхроимпульс, поступающий по шине 12 запускает триггер 9, который своим единичным .выходом разрешает работу генератора 10 импульсов. Последний формирует на своем прямом и ниверсном выходах взаимоинверсные последовательности импульсов. По положительному фронту триггера 9 и переднему фронту прямой последовательности импульсов в адресном регистре 11 фиксируется код адреса, первая часть которого поступает по входам 15, а вторая с накопителя микропрограмм 7 от считывания - по предыдущему адресу, в исходном состоянии содержимое регистра 11 равно О. По переднему фронту инверсной последовательносли импульсов с генератора 10 информация группы выходов накопителя 7 фик-: сируется на регистре 8 микрокоманд, где удерживается до следующего перед него фронта инверсной импульсной последовательности. Если в следующем микрокомандном слове одна или несколько микрокоманд повторяют свое значение как в предыдущем, то длительность микрокоманды на выходе регистра 8 увеличивается на величину еще одного периода генератора импульсов и т.д. Из указанного выше следует, что условием работы блока микропрограммного правления является то, что время выборки информации из накопителя микропрограмм 7 должно быть меньшеполупериода частоты импульсной последовательности, формируемой генератором 10 импульсов, на величину времени, необходимого для записи этой информации в регистр 8 микрокоманд или адресньш регистр 11 Причем в каждом текущем микропрограм мном слове зафиксирован адрес следую щего микропрограммного слова. Такая микропрограмма может выполняться цик лически, если в последнем микропрограммном слове зафиксировать адрес первого микропрограммного слова. Пре рвать эту последовательность выполне ,ния микропрограммы может только микрокоманда с выхода 20, по заднему фронту которой триггер 9 установится в нулевое состояние, а обнуленный при этом единичный выход триггера 9 запретит формирование,импульсной последовательности генератором 10 и сбросит-на нуль регистры 11 и 8 Таким образом блок микропрограммного управления будет приведен, в исходное состояние. Таким образом, при формировании последовательности адресов на выходе регистра 8 микрокоманд формируется последовательность микрокоманд и адресных кодов, длительность которых зафиксирована количеством единиц в соседних адресах по соответствующe ry разряду в зоне микропрограммного накопителя 7. Основой операционной части устрой ства является блок 1 памяти. Все поле адресов этого блока разбито на зоны, в каждую из которых входит гру па ячеек. Количество указанных зон определяется количеством обслуживаемых абонентов (процессоров). При подаче этих адресных кодов на адресный вход блока 1 последний формир ет на своем выходе соответствующую информацию, которая поступает на первый вход сумматора 2. На второй вход этого сумматора через блок элементов И, управляемьй микрокомандой 19, поступает содержимое буферного регистра 4. Поразрядное сложение указанных информационных слоев образует адрес команды или операнда. Вместо содержимого буферного регистра 4 на вход младшего разряда сумматора 2 может быть подана единица 21. Образованная сумма может быть занесена в блок 1 через блок 3, управляемый микрокомандой 24. При этом код суммы фиксируется на буферном регистре 4, передним фронтом микрокоманды 16, а затем при подаче на вход записи блока 1 микрокоманды 17 производится запись информации, зафиксированной на регистре 4,в ячейку блока 1, адрес которой подан на адресный вход блока 1 от накопителя 7 микропрограмм, зона, в которой находится эта ячейка, определяется кодом, подаваемым с группы входов 13. Аналогичным образом производится запись информации, поступающей по группе входов 15, с той лишь разницей, что запись этой информации в регистр 4 производится через блок 3 элементов .И-РШИ под управлением микрокоманды 25. Загрузка этой информации в блок 1 производится для обновления (замены) содержимого соответствующих счетчиков и индекснььч констант. Сформированный адресный код подается во внешние (по отношению к предлагаемому устройству) устро ства че-рез группу выходов 14. Причем трансляция адреса команды на группу сопровождается сигналом на выходе 22, а адреса операнда - сигналом на выходе 23. Работа устройства при формировании адреса команды по запросам процессоров начинается с исхЬдного состояния, при котором регистры адреса 11, микрокоманд 8, буферный регистр 4,а также триггер 9 обнулены. Пуск устройства осуществляется синхроимпульсом по входу 12. Этот синхроимпульс устанавливает в единичное состояние триггер 9. Передним фронтом сигнала со своего единич-ного выхода триггер 9 фиксирует код

признака адресации, поступающий по группе входов 15. Этот код определяет базовый адрес микропрограммы, которая зафиксирована в накопителе 7 микропрограмм.Эта микропрограмма, реализуемая в блоке 6 микропрограммного управления, формирует адрес, указывающий совместно с базовым адресом полный адрес ячейки блока 1, в которой зафиксировано содержимое счетчика команд данного процессора программы.

При подаче на вход чтения блока 1 сигнала 17 по указанному адресу чере время выборки информации из блока 1 будет считан адрес команды, который поступит на второй вход сумматора 2.

Так как. сумматор 2 является комбинационным, то на его выходах, т.е. на группе выходов 14, будет сформирован код адреса данной команды. Этот код сопровождается маркирующим импульсом микрокоманды на выходе 22. Для формирования адреса следующей команды на блоке 6 микропрограммного управления выделится последовательность импульсов, которая произведет суммирование единицы к сформированному адресу команды путем подачи микрокоманды 21 на вход младшего разряда сумматора 2. Шкрокоманда 24 открывает блок 3 элементов И-ИЛИ, и этот код поступает на входы буферного регистра 4, где фиксируется передним фронтом микрокоманды 16, после чего микрокоманда 17 заменяется микрокомандой 18, т.е. записью в блок 1. Так как.адрес на блоке 1 не изменился, то в ячейку, с которой бьш считан адрес данной команд буде записан адрес следующей команды. Затем будет сформирована микрокоманда 20, которая сбросит триггер 9 в исходное состояние, а последний приведет в исходное состояние все устройство, сбросив все регистры.

Формирование адреса команды при ветвлении рабочих программ осуществл..ется следующим образом.

Как и в предьиущем случае код признака адресации с группой входов 15 сигналом с единичного выхода триггера 9 фиксируется на адресный регистр 11, с помощью этого адресного кода вызывается подпрограмма формирова- ния микрокоманд.

Микрокоманда 25 разрешает прохождение через блок 3 кода смещения на

информационные входы буферного регисра 4, где этот код фиксируется микрокомандой 16.

Одновременно на вход запис.и бло ка 1 подается микрокоманда 18, а на адресный вход блока 1 - адрес ячейки, в которую должен зафиксироваться код. Этот же кодчерез блок 5, стробируемый микрокомандой 19, через сумматор 2 поступает на группу выходов.

Прохождение этого кода на группу выходов 14 сопровождается сигналом с выхода 22.

По адресу команды, сформированному согласно приведенному алгоритму. Из запоминающего устройства ЦВМ (не показано) поступает код команды. Код команды поступает в устройство по группе входов 15 и сопровождается синхроимпульсом по входу 12. Отличием кода команды от всех предыдущих кодов по группе входов 15 есть наличие кода операции, который совместно с признаком составляет базовый адрес микропрограммы.

Задачей устройства адресации при обработке поступившего кода команды является формирование адреса операнда.

Формирование адреса операнда проиводится в следующем порядке.

Синхроимпульс с входа 12 установи триггер в единичное состояние и за- пустит генератор 10 импульсов, который зафиксирует в старших разрядах аресного регистра 11 значение кодовых полей команды. Коды составляют старшую часть адресного кода микропрограмного накопителя, т.е. этот базовый адрес определит микропрограмму формирования адреса операнда для конкретной операции. Причем код признака адресации в зависимости от своего значения обеспечивает кодирование нескольких способов формирования адреса операнда.

Непосредственной считается такая адресация, когда адрес указывается полем смещения команды, т.е. адресный код кодирующих разрядов поля команды фиксируется на буферном регистре 4, передается через блок 3 и сумматор 2 на группу выходов 14.

При необходимости могут быть реа 1изованы и другие способы адресации, в этом случае меняется лишь микпропрограмма в накопителе 7 микро- 911 реализующая эти способы адпрограмм, ресации. При выполнении любой из подпрограм реализующих указанные способы адресации в блоке 6, будут сформированы мик рокоманды 16 и 25, с помощью которых поле команды, поступающей по входам 15, будет зафиксировано на буферном регистре 4 по переднему фронту микрокоманды 16, В случае непосредственной адресации в микропрограмме, реализующей этот способ, микрокоманда 17 (чтение блока 1) должна отсутствовать и тогда микрокоманда 25 через блок 3 и сумматор 2 пропустит код на выходы 14. Этот код будет стробироваться сигна--,2f

1Ж

/6

i

7

I , 1 „. гчп

т

7

..П

I 3 лом на выходе 22, сигнализирунлцем о, том, что на выходах 14 находится адрес операнда команды, которая поступила на устройство по входам 15. Адресация через соответствующий индексный регистр или/самоотносительная адресация производится аналогичным образом микропрограммой, определяемой соответствующим базовым адресом, зафиксированным в старших разрядах регистра 11. При этом блок 6 после запуска триггера 9 выделит соответствующие микрокоманды. Предлагаемое изобретение позволяет расширить функциональные возможности устройства и сократить объем его оборудования.

|1

8

1

.I

f 1 г MMf V

iei7W3202J22 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления памятью в многопроцессорной вычислительной системе | 1974 |

|

SU522501A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 812046, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-15—Публикация

1983-07-08—Подача