(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАЧАЛЬНЫХ

Изобретение относится к цифровой вычислительной и измерительной технике и может найти применение в системах оперативного статического анализа квазистационарных случайных процессов при решении задач гидрометеорологии, связи, биологии, радиоэлектроники и др.

Известны цифровые устройства для определения одномерных начальных моментов случайных процессов. Указанное устройство при вычислении начальных моментов вьгсших порядков характеризуется значительной сложностью в виду наличия в нем (ум-l) функциональных тфеобразователей, которые по существу являются многоразрядными блоками умножения, а также блоков памяти, усреднения и формирователей интервалов, .ующих каждый, помимо собственного местного блока управления, еще и центрального блока управления. Значительное упрощение устройств подобного типа с одновременным сохранением или улучшением других технико-экономических

МОМЕНТОВ

показателей (точность, быстродействие) достигается использованием вероятностного способа кодирования дискретной информации, по которому полноразрядное двоичное число-отображается одноразрядным, а входная совокупность ординат преобразуется в бернуллиевскую последовательность импульсов-результатов вероятностного гфеобразования li.

Наиболее близким к изобретению по

10 технической сущности является устройство для вычисленияНачальных моментов, содержащее вероятностный двоичный элемент, два интегратора, блок управления, делитель частоты, группу элементов И и триггер .

Недостатком известного устройства являются ограниченные функциональныевозможности, определяемые невозможностью вычисления начальных моментов

20 высщих порядков.

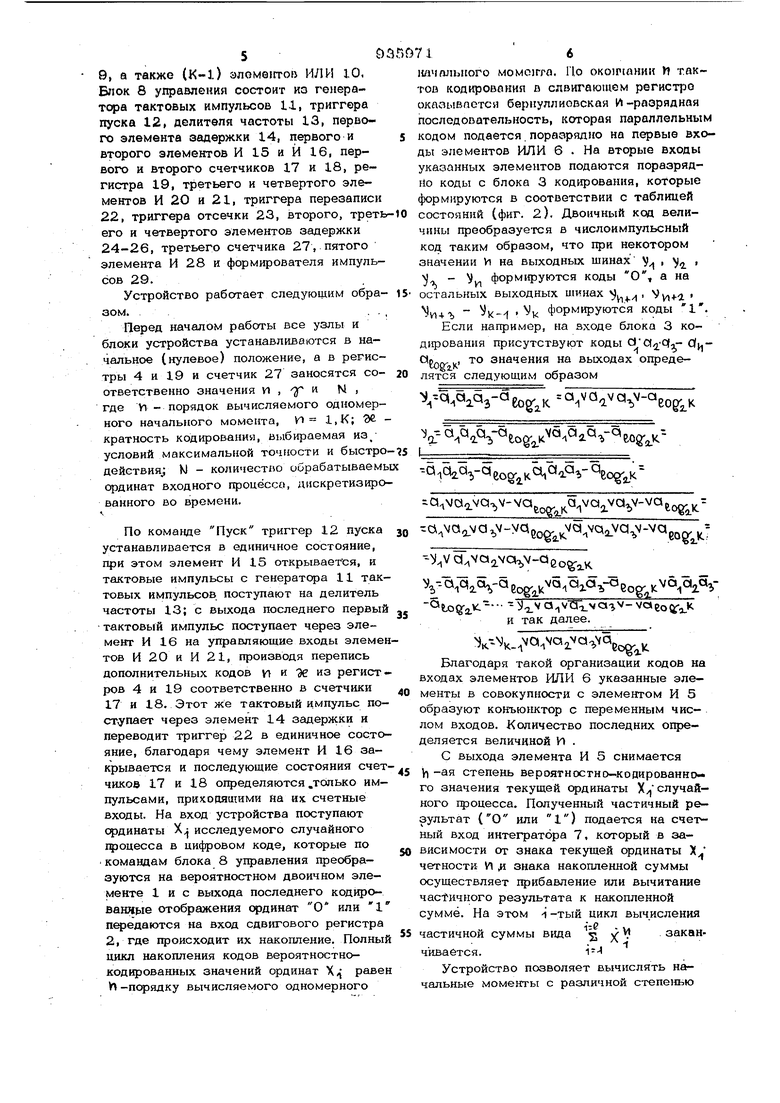

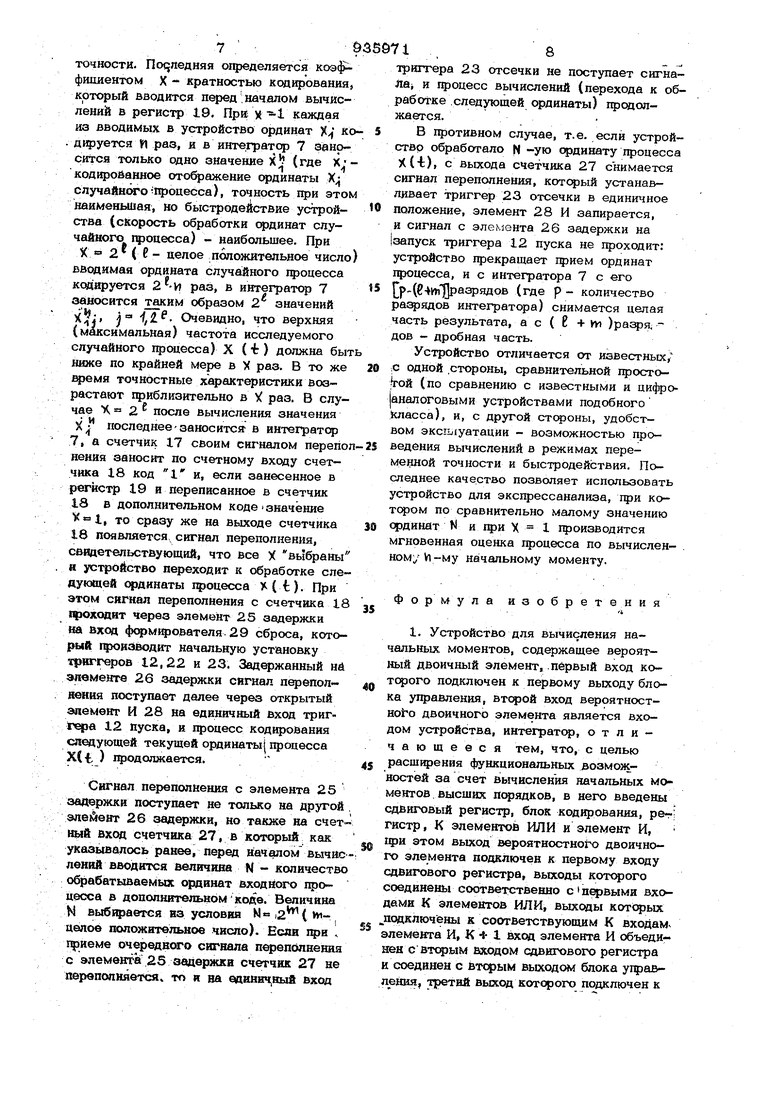

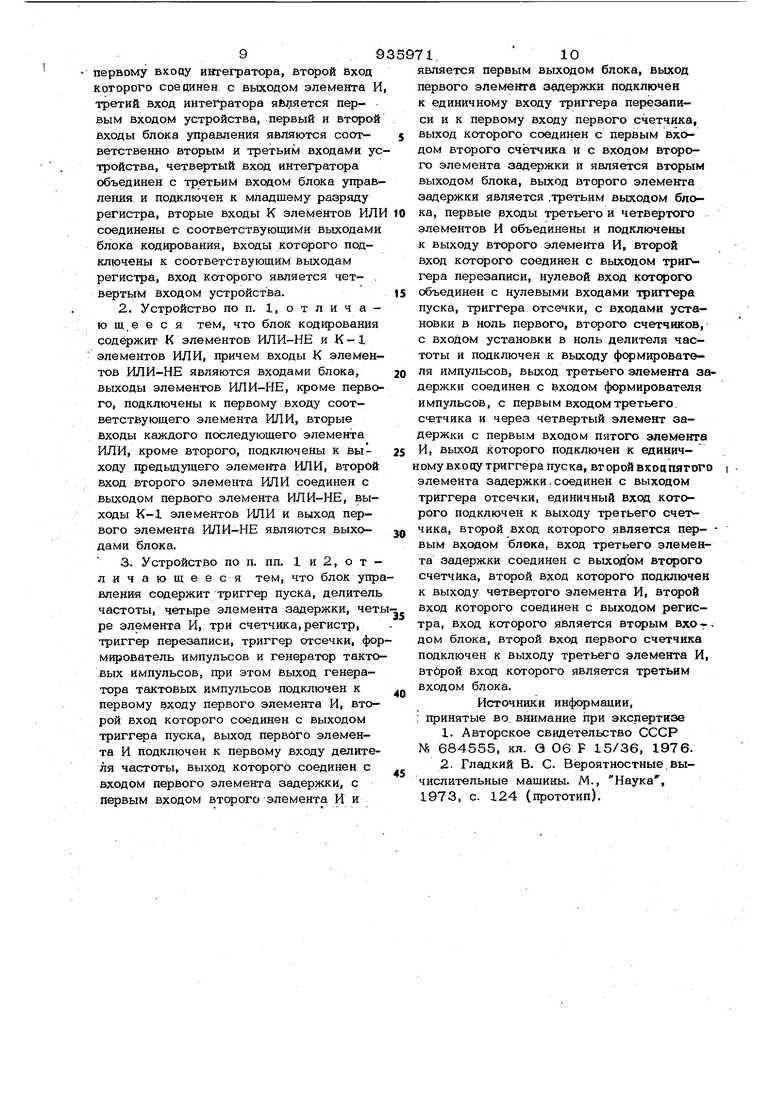

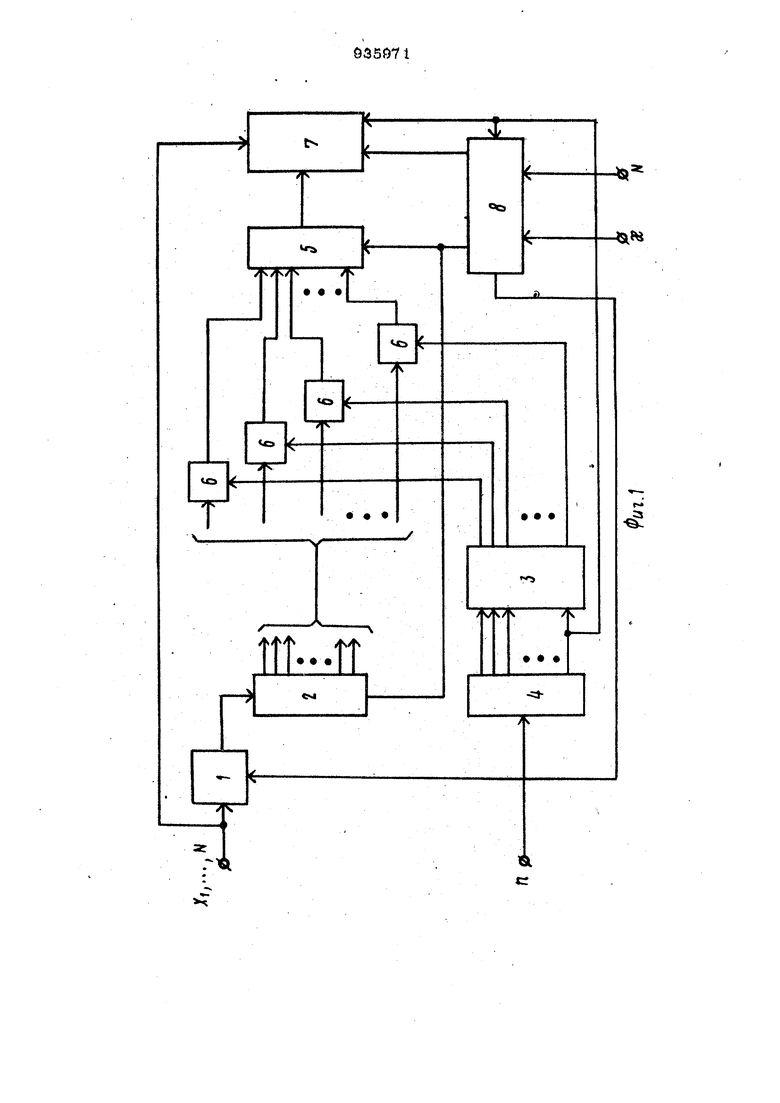

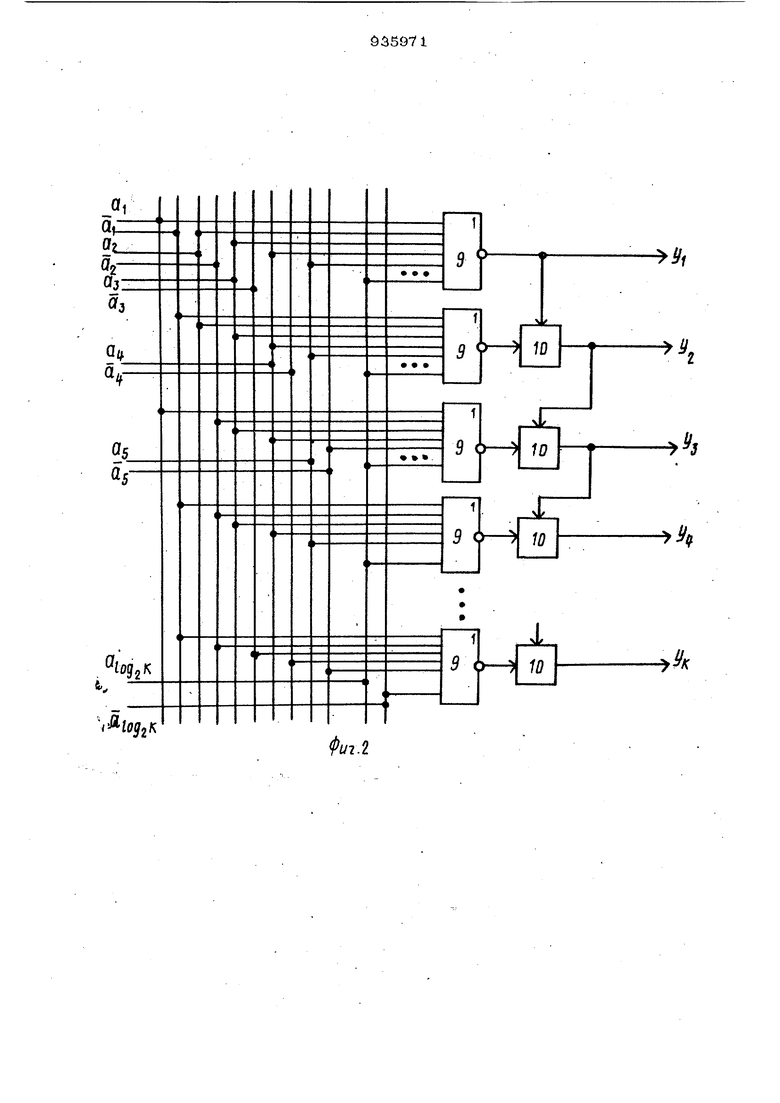

Цель изобретения - расширениефункциональных возможностей за счет вычисления моментов высших порядков. Поставленная цель достигается тем, что в устройство для вычисления начальных моментов содержащее вероятностный двоичный элемент, первый вход которого подключен к первому выходу блока yi aBления, втсрой вход вероятностного двоично го элемента входом устройства и интегратс, введены сдвиговый регистр, блок кодирования, регистр, К элементов ИЛИ и элемент И, при этом выход вероятноетного двоичного элемента подключён к первому входу сдвигового регистра, выходы которого соединены соответственно с первыми входами К элементов ИЛИ, выходы которых подключены к соотйетствующим К входам элемента И, K-f I вход элемента И объединен со вторым входом сдвигового регистра и соединен со вторым выходом блока управления, третий выход которого подключен к первому входу интегратора, второй вход которого соединен с выходом элемента И, третий вход интегратора является первым входо устройства, первый и второй входы блока улравления являются соответственно вторым и третьим Входами устройства, четвертый вход интегратора объединен с третьим входом блока управления и подключен к младшему разряду сдвигового регистра, входы К элементов ИЛ соединены с соответствующими выходами блока кодирования, входы котороТго подключены к соответствующим выходам сдвигового регистра, вход которого является четвертым входом устройства. Кроме того, блок кодирования содержит К элементов ИЛИ-НЕ и К-1 элементов ИЛИ, причем входы К элементов ЙЛИ-НЕ являются входами блока, выкоды элементов ИЛИ-НЕ, кроме первого,поаклю чены к первому вхоцу соответствующего элемента ИЛИ, вторые вхоцы каждого последующего элемента ИЛИ, кроме второго, подключены к выходу i предыдущего элемента ИЛИ, второй вход-втс ого элемента ИЛИ соединен с вьрсодом первого элемента ИЛИ-НЕ, выходы К-1 элементов ИЛИ и Выход первого элемента ИЯИ-НЕ являются соответствующими выходами блока. Блок у1фавления содержит триггер пуска, делитель частоты, четыре элемен та задержки, четьфе элемента И, три счетчика, регистр, триггер п езаписи, тригг отсечки, формирователь импульсов и генератор тактовых импульсов, при этом выход генератора тактовых импульсов подключен к первому входу первого элемента И, второй вход котоого соединен с выходом триггера пуска, выход первого элемента И подключен к первому входу делителя частоты, выход которого соединен с входом первого элемента задержки, с первым входом второго элемента И и является первым выходом блока, выход первого элемента задержки подключен к единичному входу триггера перезаписи и к первому входу первого счетчика, выход которого соединен с первым входом второго счетчика и с Входом второго элемента задержки и является вторым выходом блока, выход второго элемента задержки является третьим Выходом блока, первые axoni.i третьего и четвертого элементов И объединены и| подключены к выходу второго элемента И, второй вход которого соединен с выходом триггера перезаписи, нулевой вход которого объединен с нулевыми входами триггера пуска, триггера отсечки, с Входами установки в нуль первого, второго счетчиков, с входом установки в нуль делителя частоты и подключен к выходу формирователя импульсов. Выход третьего элемента задержки соединен со входом формирователя импульсов, с первым входом третьего счетчика и через четвертый элемент задержки с первым входом пятого элемента И, выход которого подключен к единичному входу триггера пуска, второй вход пятого элемента задержки соединен с выходом триггера отсечки, единичный вход которого подключен к выходу третьего счетчика, второй вход которого является первым входом блока, вход третьего элемента задержки соединен с выходом второго :;четчика, второй вход которого подключен к выходу четвертого элемента И, второй вход которого соединен с выходом регистра, вход которого является вторым входом блока, второй вход первого счетчика подключен к выходу третьего элемента И, второй вход которого является третьим входом блока. На фиг- 1 изображена функциональная схема устройства; на фиг. 2 - схема блока кодирования; на фиг. 3 - схема блока уг5 авления. Устройство содержит вероятностный двоичный элемент 1, сдвиговый регистр 2, блок 3 кодирования, регистр 4, элемент И 5, К элементов ИЛИ б, интегратор 7, блок 8 управления. Блок 3 кодирования содержит К элементов ИЛИ-НЕ 9, а также (K-l) эпоментоп ИЛИ Ю, Блок 8 ущэавпения состоит из геиератор& тактовых нмпульсов II, триггера пуска 12, делителя частоты 13, первого элемента задержки 14, первого и второго элементов И 15 и И 16, первого и второго счетчиков 17 и 18, регистра 19, третьего и четвертого элементов И 20 и 21, триггера перезапис 22, триггера отсечки 23, второго, трет его и четвертого элементов задержки 24-26, третьего счетчика 27, пятого элемента И 28 и формирователя импульсов 29. Устройство работает следующим обрааом. Перед началом работы все узлы и блоки устройства устанавливаются в начальное (нулевое) положение, а в регистры 4 и 19 и счетчик 27 заносятся соответственно значения Y , п N , где VI - порядок вычисляемого одномерного начального момента, Ki 1,К; Эб. кратность кодирования, выбираемая из условий максимальной точности и быстро действия К) - количество обрабатываемы ординат входного процёссо, дискретизиро ванного во времени. По команде Пуск триггер 12 пуска устанавливается в единичное состояние, при этом элемент И 15 открывается, и тактовые импульсы с генератора 11 тактовых импульсов поступают на делитель частоты 13; с выхода последнего первый тактовый импульс поступает через элемент И 16 на управляющие входы элемен тов И 20 и И 21, производя перепись дополнительных кодов У1 и Эе из регистров 4 и 19 соответственно в счетчики 17 и 18. Этот же тактовый импульс поступает через элемент 14 задержки и переводит триггер 22 в единичное состояние, благодаря чему элемент И 16 закрывается и последующие состояния счет чнкое 17 и 18 определяются .только импульсами, приходящими на их счетные входы. На вход устройства поступают ординаты Х исследуемого случайного гфоцесса в цифровом коде, которые по командам блока 8 управления преобразуются на вероятностном двоичном элементе 1 и с выхода последнего кодированные отображения срдинат О или I передаются на вход сдвигового регистра 2, где происходит их накопление. Полный цикл накопления кодов вероятностнокодированных значений ординат Х равен V -порядку вычисляемого одномерного 716 ИЛЧШ1Ы1ОГО МОМ01ГГО. По око)р1ании И тактов кодирования в спвигающем регист1зо окааывоетси берцуллиовская И-разрядная последовательность, которая параллельным кодом подается. поразрядно на первые входы элементов ИЛИ 6 . На вторые входы указанных элементов подаются поразрядно коды с блока 3 кодирования, которые формируются в соответствии с таблицей состояний (фиг. 2). Двоичный коа величины преобразуется в числоимпульсный код таким образом, что при некотором значении И на выходных шинах V/i , Va л и коды О, а на остальных выходных шинах % V , .i - VK-( формируются коды . Если например, на входе блока 3 коД1фоваш1я присутствуют коды dct/ Olv- к. ° значения на выходах определятся следующим образом V..K V .. eog- tcI. --aAV eog,,K - eogj,,,,.,v-vaeog --,v ,va,,v-aeo.K ,-0 ,,va,,rqeog- ic aiqiq . ,,v o vTrL a-jv-vcseo, и так далее. V-NK..a2. Благодаря такой организации кодов на входах элементов ИЛИ 6 указанные элементы в совокупности с элементом И 5 образуют конъюнктор с переменным числом входов. Количество последних определяется величиной И . С выхода элемента И 5 снимается степень вероятностно-кодированно значения текущей сфдинаты Х случайного щэоцесса. Полученный частичный результат (О или 1) подается на счетный вход интегратора 7, который в за- висимости от знака текущей ординаты Х четности V знака накопленной суммы осуществляет прибавление или вычитание 4actH4Horo результата к накопленной сумме. На этом -1-тый цикл вычисления 1-.е - VI S Х частичной суммы вида iM чивается. Устройство позволяет вычислять начальные моменты с различной степешзю

точности. Псч педняя определяется коэ$ фициентом X - кратностью кодирования} который вводится перед .началом вычислений в регистр 19. При X каждая из вводимых в устройство ординат Х// код|фуется Vl раз, и в интегратор 7 заносится только одно значение Х (где Х -кодированное ото ажение qpдинaты Х случайното-процесса), точность при этом наименьшая, но быстродействие устройства (скорость обработки срдинат случайного ipouecca) - наибольшее. При Х 2 f Р - целое положительное число) вводимая ордината случайного npo:iecca кой1фуется раз, в интегратор 7

заносится таким образом 2 значений i j Очевидно, что верхняя (максимальная) частота исследуемого случайного процесса) X (t) должна быт ниже по крайней мере в X раз. В то же емя точностные характеристики возрастают приблизительно в У раз. В случае после вычисления значения X j послед нее-занос ится в интегратор 7, а счетчИк 17 своим сигналом перепол нения заносит по счетному входу счетчика 18 код и, если занесенное в регистр 19 и переписанное в счетчик 18 в дополнительном кодезначение 1, то сразу же на выходе счетчика 18 появляется переполнения, свидетельствующий, что все X выбраны и устройство переходит к обработке следующей ординаты щюцесса X ( t). При этом Сигнал переполнения с счетчика 18 1ФОХ01ДИТ через элемент 25 задержки на вход фqpмlфoвaтeля 29 сброса, который 1 к иаводит начальную установку триггеров 12,22 и 23. Задержанный ни элементе 26 задержки сигнал переполнения поступает далее через открытый элемент И 28 на единичный вход триг.гера 12 пуска, и процесс кодирования следующей текущей ординаты| процесса Х( t ) 14)одолжается.

Сигнал переполнения с элемента 25 задержки поступает не только на другой элейент 26 задержки, но также на счетный вхад счетчика 27, в который как указывалось ранее, перед началом вычислений вводится величива N - количество обрабатываемых ординат входного процесса в дополнительномкоде. Величава М выбирается яз условия Ne,2(wiцепое жшожательное число). Еслн очередного сигнала пе зеполнения с элемента 25 задержки счетчнк 27 не переполняется, тп и ва единеч ный вход

триггера 23 отсечки не поступает сигнаЯа и процесс вычислений (перехода к обработке следующей ординаты) продолжается.

В противном случае, т.е. если устройство обработало N -ую ординату процесса /(t), с выхода счетчика 27 снимается сигнал переполнения, который устанавливает триггер 23 отсечки в единичное положение, элемент 28 И запирается, и сигнал с элемента 26 задержки на |запуск триггера 12 пуска не проходит: устройство прекращает гфием ординат процесса, и с интегратора 7 с его Гр-(С4№ |раарадов (где р - количество разрядов интегратора) снимается целая часть результата, а с ( + VM ) дов - дробная часть.

Устройство отличается от известных, ,с одной стороны, сравнительной просто1гой (по сравнению с известными и цифро аналоговыми устройствами подобного loiacca), и, с другой стороны, удобством эксь(уатации - возможностью проведения вычислений в режимах переменной точности и быстродействия. Последнее качество позволяет использовать устройство для экспрессанализа, при котаром по сравнительно малому значению ординат N и при X 1 гдэоизводится мгновенная оценка процесса по вычисленному И-му начальному моменту.

Формула изобретения

1. Устройство для вычисления начальных моментов, содержащее вероятный двоичный элемент, .первый вход которого подключен к первому выходу блока управления, вход вероятностHoto двоичного элемента является входом устройства, интегратор, отличающееся тем, что, с целью расщ1фения функциональных возможностей за счет вычисления начальных моментов высщих порядков, в него введены сдвиговый регистр, блок кодирования, ре гистр, К элементов ИЛИ и элемент И, 1фи этом выход вероятностного двоичного элемента подключен к первому входу СДВИГОВОГО) регистра, выходы KOTqporo Соединены соответственно спервыми входами К элементов ИЛИ, выходы котярых одключ ены к соответствующим К вxoдaм элемента И, К 1 вход элемента И объеди.аен с вторым входом сдвигового регистра и соединен с вторым выходом блока угфавления, третий выход которого подключен к которого соединен с выходом элемента И, третий вход интегратора я6;;1яется первым входом устройства, первый и второй входы блока управления являются соответственно вторым и третьим входами устройства, четвертый вход интегратора объединен с третьим входом блока управления и подключен к младшему разряду регистра, вторые входы К элементов ИЛИ соединены с соответствующими выходами блока кодирования, входы которого подключены к соответствующим выходам регистра, вход которого является чет- . вертым входом устройства. 2. Устройство по п. 1, о т л и ч а ю щ.е е с я тем, что блок кодирования содержит К элементов ИЛИ-НЕ и К -1 элементов ИЛИ, причем входы К элементов ИЛИ-НЕ являются входами блока, выходы элементов ИЛИ-НЕ, кроме перво го, подключены к первому входу соответствующего элемента ИЛИ, вторые входы каждого последующего элемента ИЛИ, кроме второго, подключены к выходу 1федьщущего элемента ИЛИ, второй вход второго элемента ИЛИ соединен с выходом первого элемента ИЛИ-НЕ, выходы К-1 элементов ИЛИ и выход первого элемента ИЛИ-НЕ являются выходами блока. 3. Устройство по п. пп. 1 и 2, о т ли чающееся тем, что блок упр вления содержит триггер пуска, делитель частоты, четыре элемента задержки, чет ре элемента И, три счетчика, регистр, триггер перезаписи, триггер отсечки, фор мирователь импульсов и генератор такто вых импульсов, при этом выход генератора тактовых импульсов подключен к первому входу первого элемента И, второй вход которого соединен с выходом триггера пуска, выход первйго элемента И подключен к первому входу делителя частоты, выход которого соединен с входом первого элемента задержки, с первым входом второго элемента И и первого элемента задержки подключен к единичному входу триггера перезаписи и к первому входу первого счетчика, выход которого соединен с первым входом второго счётчика и с входом второго элемента задержки и является вторым выходом блока, выход второго элемента задержки является .третьим выходом блока, первые входы третьего и четвертого элементов И объединены и подключены к выходу второго элемента И, второй вход которого соединен с выходом триггера перезаписи, нулевой вход которого объединен с нулевыми входами триггера пуска, триггера отсечки, с входами установки в ноль первого, второго счетчиков, с входом установки в ноль делителя частоты и подключен к выходу фсрмирователя импульсов, выход третьего элеменгга задержки соединен с входом формирователя импульсов, с первым входом третьего, с-етчика и через четвертый элемент задержки с первым входом пятого элемента И, выход которого подключен к единичому входу триггера пуска, вт орой вход пятого элемента задержки.соединен с выходом триггера отсечки, единичный вход которого подключен к выходу третьего счет чика, второй вход которого является пер- вым входом блока, вход третьего элемента задержки соединен с выходом счетчика, второй вход которого подключен к выходу четвертого элемента И, второй вход которого соединен с выходом регистра, вход которого является вхо-гдом блока, второй вход первого счетчика подключен к выходу третьего элемента И, втброй Вход которого является третьим входом блока. Источники информации, ; принятые во. внимание при 1.Авторское свидетельство СССР NS 684555, кя. Q 06 F 15/36, 1976. 2.Гладкий В. С. Вероятностные. вычислительные машины. М., Наука, 1973, с. 124 (прототип).

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный коррелометр | 1980 |

|

SU932500A1 |

| Устройство для определения законов распределения вероятностей | 1978 |

|

SU922765A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Устройство распознавания изображений | 1989 |

|

SU1674153A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| ВЕРОЯТНОСТНЫЙ АНАЛИЗАТОР | 1972 |

|

SU342191A1 |

| Вероятностный измеритель спектра мощности | 1975 |

|

SU690494A1 |

| Анализатор случайных процессов | 1979 |

|

SU809204A1 |

nt...n

г

a С

Авторы

Даты

1982-06-15—Публикация

1980-07-16—Подача