I

Изобретение относится к вычислительной технике и предназначено для использования в специализированных вычислительных машинах..

Известно устройство для вычисления законов распределения вероятностей , содержащее пересчетную схему, ключи, линии задержки, схемы совпадения, триггер, переключатель установки уровня анализа til.

Недостаток данного устрой ства сложность коммутации перечисленных узлов.

Наиболее близким техническим решением к предложенному является цифровой вычислитель законов распределения вероятностей, содержащий буферное запоминающее устройство, сМетчик зон, дешифраторы,промежуточное устройство, сумматор, схему управления нахождением функции плотности распределения веройтностёй и схему управления нахождением функ.ции распределения вероятностей

управл «ющий tpHrrep, задающий генератор импульсов, переключатель, логические схемы 2.

Однако наличие s схеме цифрового вычислителя двух запоминающих устройств , схем управления нахождением вышеуказанных функций существенно увеличивает аппаратурными объем и усложняет устройство.

Цель изобретения - повышение быст

ГО родействия и упрощение устройства.

Поставленная цель достигается тем что в устройство для опреде;ления законов распределения вероятностей, содержащее первый элемент И, блок .

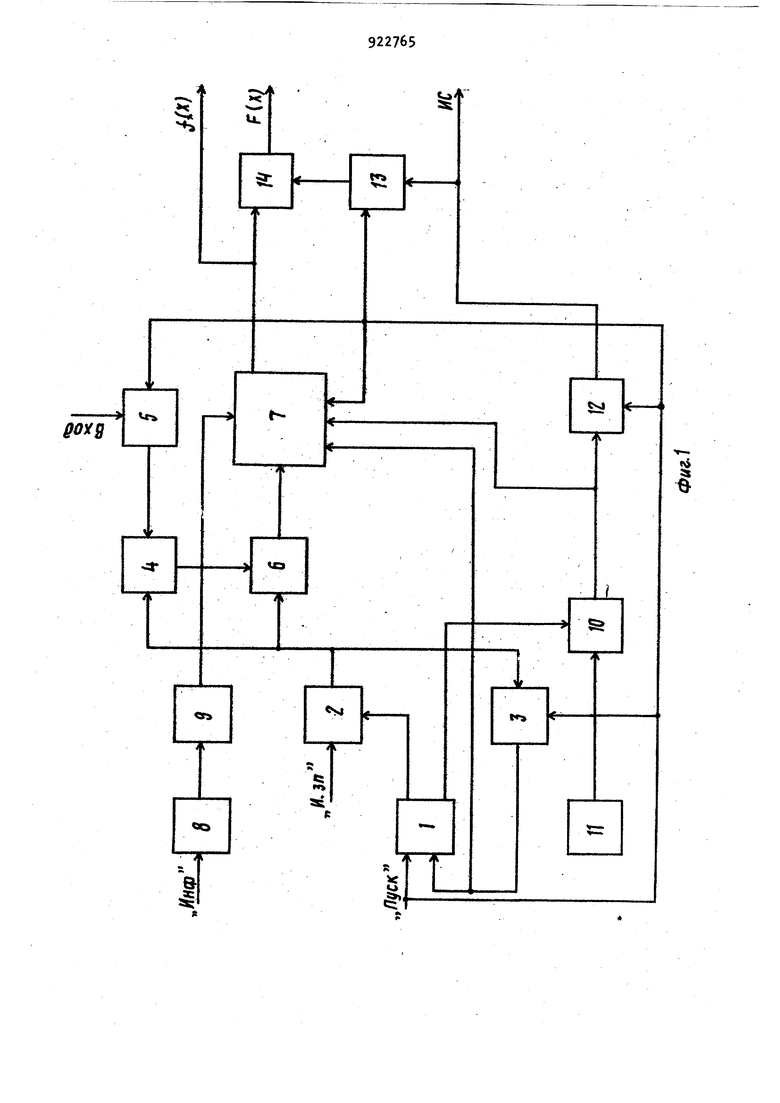

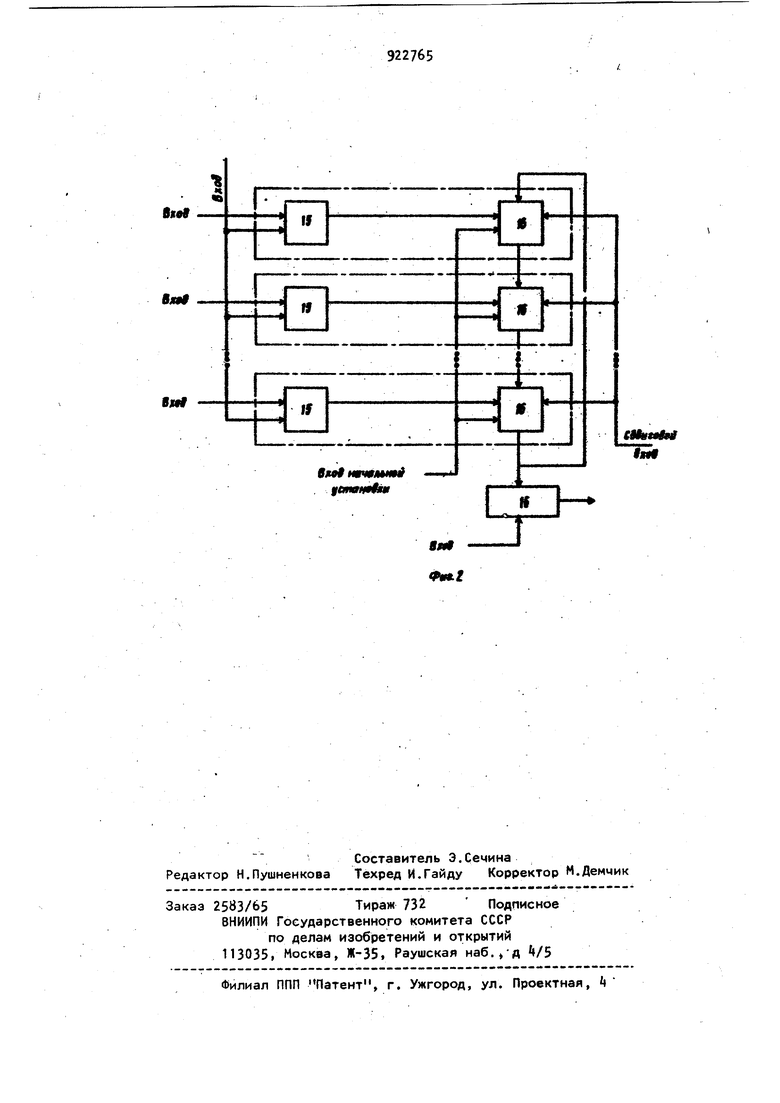

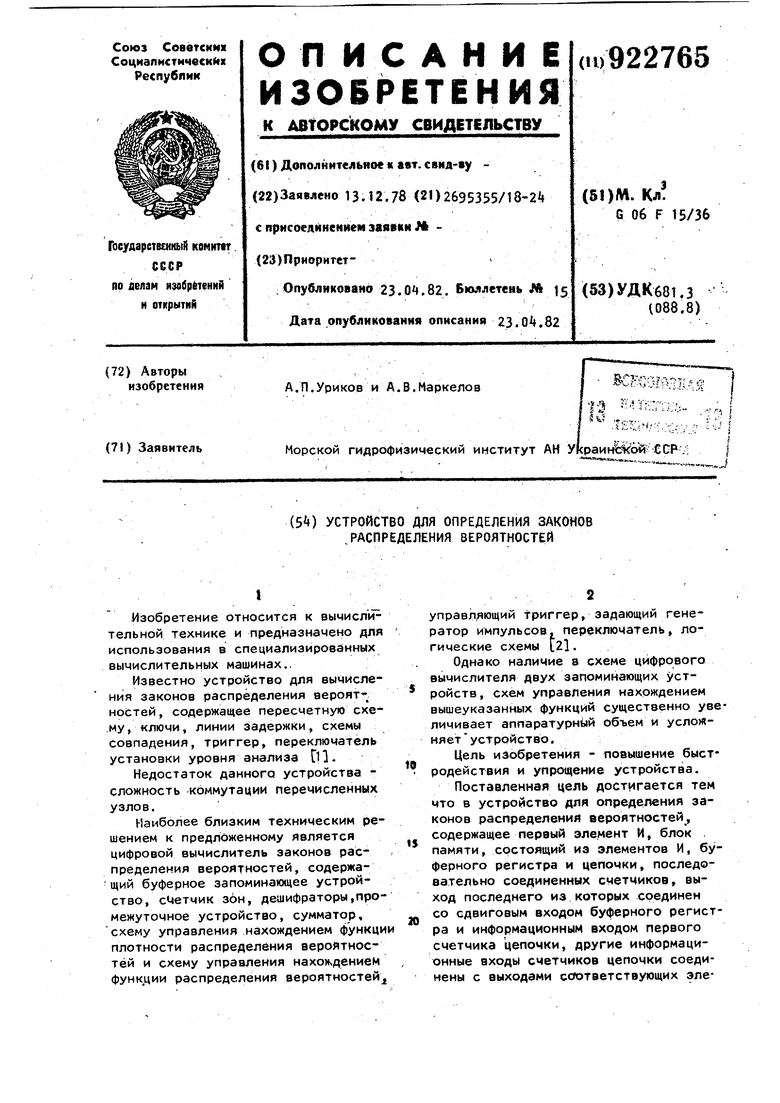

is памяти, состоящий из элементов И, буферного регистра и цепочки, последовательно соединенных счетчиков, выход последнего из которых соединен со сдвиговым входом буферного регисттра и информационным входом первого счетчика цепочки, другие информационные входы счетчиков цепочки соединены с выходами ссютветствующих элементов И блока памяти, приемный регистр, вход которого является первым информационным входом устройсвта, а выход через дешифратор соединен с информационными входами эле ментов И блока памяти, элемент ИЛИ, первый вход которого подключен к выходу счетчика зон и является первым выходом устройства, а второй вход элемента ИЛИ соединен с управляющими входами запоминающего регистра, с входом начальной установки счетчиков цепочки счетчиков блок памяти, счетчика зон, счетчика чисе единичным входом управляющего тригге и является входом Пуск устройства нулевой вход управляющего триггера соединен с управляющим входом буфер ного регистра блока памяти, с выходом сЧетчика чисел, информационный вход которого соединен с управляющим входом второго элемента И, выхо которого соединен с управляющими входами элементов И блока памяти, нулевой выход управляющего триггера соединен с первым входом третьего элемента И, второй вход которого подключен к генератору тактовых импульсов, а выход третьего элемента И подключен к сдвиговому входу счет чиков цепочки счетчиков блока памят и к информационному входу счетчика 3oHj при этом информационный вход запоминающего регистра является вто рым информационным входом устройств введены вероятностный двоичный элемент и накапливающий сумматор, выход которого является вторым выхо- дом устройства, первый вход соединен с выходом буферного регистра блока памяти и является третьим выходом устройства, выход запоминающе регистра соединен с первым входом вероятностного двоичного элемента, второй вход подключен к выходу первого элемента И, первый вход которого соединен с единичным выходом устройства, выход вероятностно двоичного элемента соединен с информационным входом второго элемента It. На фигЛ приведена функциональная схема устройства; на фиг.2 - сх ма блока памяти. Схема содержит управляющий триггер 1, элемент 2И, счетчик 3 чисел, вероятностный двоичный элемент k, запоминающий регистр 5, элемент 6 И, блок 7 памяти, приемный регист 8, дешифратор 9, элемент 10 И, гене ратор 11 тактовых импульсов, счетчик 12 зон, элемент 13 ИЛИ, накапливающий сумматор И, элемент 15И, цепочка 16 счетчиков, буферный регистр 17. Устройство работает следующим образом. Подачей сигнала Пуск в исходное О состояние устанавливается управляющий триггер 1, счетчик 3 чисел, счетчик 12 зон, счетчики 16 блока 7 памяти, накапливающий сумматор 1, а на запоминающий регистр 5 заносится число 1/Х , где X - заданное количество чисел входного ряда. Эта величинаг записанная в двоичном коде и сдвинутая на К разрядов до первой значащей цифры 3 старшем разряде, является вероятностью накопления чисел входного ряда в блоке 7 памяти, при этом управляющий триггер дает потенциал разрешения на элемент И2. На и -разрядный приемный регистр 8 заносится число входного ряда, сопровождающееся импульсом записи, который через открытый элемент И2 поступает на управляющий вход вероятностного двоичного элемента, одновременно с этим на счетчике 3 чисел фиксируется поступление первого числа входного ряда. Датчик равномерно распределенных случайных чисел, входящий в вероятностный двоичный элемент ,выдает код, который на цифровой схеме сравнения сравнивается с числом , записанном на запоминающем регистре 5- Если выработанный код -l/X , то с выхода вероятностного двоичного элемента сигнал через открытый элемент Иб поступает в блок 7 памяти на входы элементов И15, и число входного ряда через дешифратор 9 заносится на соответствующий счетчик 16 блока памяти. Если же выработанный код |/х , то устройство будет ожидать поступления следующего числа входного ряда. Как только последнее число заданного входного ряда занесется в блок памяти, счетчик чисел выработает импульс, который на буферном регистре 17 блока памяти зафиксирует запятую на К разрядов вправо от старшего разряда, т.е. практически осуществляя деление на 2 и перебрасывает управляющий триггер, в 1 состояние. Импульсы с генератора 11 тактовых импульсов через открытый элемент И 10 поступают на сдвиговые входы счетчиков 16 и вся информация из блока

памяти параллельно через буферный регистр выдается для отображения функции плотности распределения вероятностей f(x) и через накапливающий сумматор 14 для отображения функции распределения вероятностей F(х). Одновременно с этим тактовые импульсы поступают на сметчик 12 зон, который фиксирует число сдвигов в блоке памяти и при достижении их числа тп обнуляет через элемент ИЛИ 13 накапливающий сумматор, выдает на регистратор импульс внешней синхронизации, при этом счетчик зон обнуляется При поступлении нового сигнала Пуск процесс вычисления вероятностных характеристик повторяется;

Технико-экономический эффект изобретения заключатеся в том, что за счет исключения времени, необходимог на проведение операций деления,увеличивается быстродействие а за счет использования одного блока памяти уменьшается аппаратурный объем,.

Формула изобретения

Устройство для определения законов распределения вероятностей , содержащее первый элемент И, блок пег мяти, состоящий из элементов И, буферного регистра и цепочки, последовательно соединенйых счетчиков выход последнего из которых соединен со сдвиговым входом буферного регистра и информационным входом первого счет.мика цепочки, другие информационные входы счетчиков цепочки соединены с выходами соответствующих элементов И блока памяти, приемный регистр, вход которого является первым инсрормационным входом устройства, а выход через дешифратор соединен с информационными входами элементов И блока памяти, элемент ИЛИ, первый вход которого подключен к выходу счетчика зон и является первым выходом устройства а второй вход элемента ИЛИ соединен с управляющими входами запоминающего регистра с входом начальной установки счетчиков цепочки сче1чи1сов блока памяти, счетчика зон, счетчика чисел, единичным входом управляющего триггера и является входом Пуск устройства, нулевой вход управляющего триггера соединен с управляющим входом буферного регистра блока памяти, с выходом счетчика чисел, информационный вход которого соединен с управляющим входом второго элемента И, выход которого соединен с управляющими входами элементов И блока памяти, нулевой выход управляющего триггера соединен с первым входом третьего элемента И,| второй вход которого подключен к генератору тактовых импульсов, а выход третьего элемента И подкг.ючен к сдвиговому входу счетчиков цепочк счетчиков блока памяти и к информационному входу счетчика зон, при этом информационный вход гйпоминающего регистра является вторым информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия иупрощения устройства, оно содержит вероятностный двоичный элемент и накапливающий сумматор, вйход которого является вторым выходом устройства, первый вход соединен с выходом буферного регистра блока памяти и является третьим выходом устройства, выход запоминающего регистра соеди}чен с первым входом вероятностного двоичного элемента, второй вход-которого подключен к выходу первого элемента И, первый вход которого соединен с единичным выходом управляющего триггера, а второй вход является третьим информационным входом устройства, выход вероятностйого двоичного элемента соединен с информационным входом второго элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР If 18511, кл. G 06 F 15/36, 196.

2.Авторское свидетельство СССР № 369575, кл. G 06 F 15/36, 1971 прототип).

X

U.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения законов распределения вероятностей | 1984 |

|

SU1188753A2 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Адаптивный цифровой измеритель параметров сигнала | 1981 |

|

SU1013867A1 |

| Цифровой статистический анализатор случайных интервалов времени | 1980 |

|

SU943745A1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Цифровой генератор колоколообразных функций | 1978 |

|

SU737936A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

Й1

Vp

ffoxg

«SI

Cr

l«

4 i i i

ICUntetft

ПЕ5§

ЯмГ

Att/

Авторы

Даты

1982-04-23—Публикация

1978-12-13—Подача