1

Изобретение относится к вычислительной и электроизмерительной технике и может быть использовано в устройствах, в которых осуществляется преобразование аналоговых сигналов в цифровой код.

Известен аналого-цифровой преобразователь, содержащий блок управления регистр чисел, двуматричный цифроаналоговый преобразователь, два ком ,0 паратора,устройство вычитания,источник образцового напряжения и логический блок П.

Недостатком данного аналого-цифрового преобразователя является не- js высокая точность преобразования.

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем, что в аналого-цифровой преобразова- 20 тель, содержащий блок управлений, установочный выход которого соединен с входом установки начального состоя-, ния триггеров регистра, а тактовые

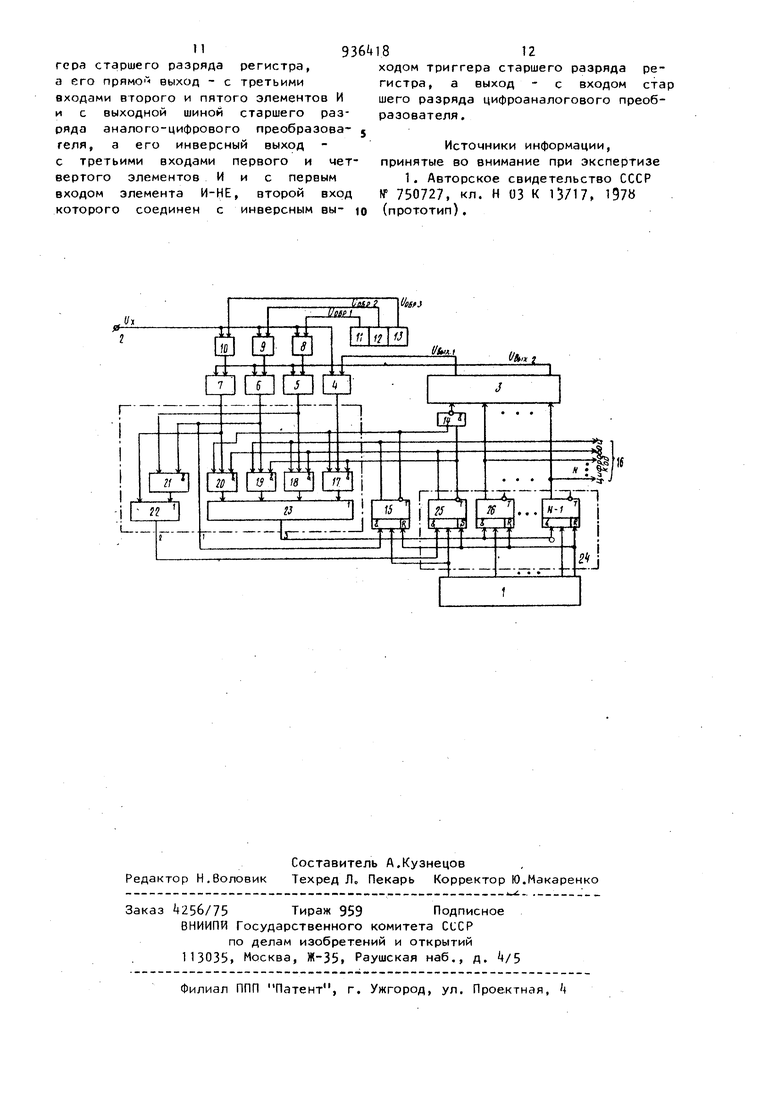

выходы - с входами синхронизации триггеров регистра, прямые выходы которых соединены с выходными шинами и, кроме прямого выхода триггера старшего разряда регистра - с. входами двуматричного цифро-аналогового преобразователя, первый выход которого соединен с первым входом первого компаратора, второй вход которого соединен с входной шиной, а выход с первым входом первого элемента И, второй вход которого соединен с инверсным выходом триггра старшего разряда регистра, а его выход - с первым входом первого элемента ИЛИ, второй выход двуматричного цифроаналогового преобразователя соединен с первым входом второго компаратора, второй вход которого соединен с выходом первого блока вычитания,первый вход которого соединен с выходом первого источника образцового напряжения, второй вход - с входной шиной, выхода второго компаратора соединен с первыми входами второго и третьего элемен тов И, второй вход второго элемента И соединен с первым входом четвертог элемента И и прямым выходом триггера старшего разряда регистра, а выход с втopы л входом первого элемента ИЛИ, выход четвертого элемента И сое динен с третьим входом первого элемента ИЛИ, первый вход пятого элемен та И соединен с вторым входом первого элемента И, а выход - с четвертым входом первого элемента ИЛИ, выход которого соединен с информационн1 ми входами триггеров младших разрядов регистра, выход третьего элемента И соединен с первым входом Элемента ИЛИ, выход которого соединен с инфор мационным входом триггера старшего разряда регистра, введены два компаратора, два блока вычитания, два источника образцового напряжения,: элемент И-НЕ и триггер старшего разряда аналого-цифрового преобразователя, причем первые входы третьего и четвертого компараторов соединены с вторым выходом двуматрично цифроаналогового преобразователя, второй вход третьего компаратора соединен с выходом-второго блока вычитанияу первый вход которого соединен с выходом второго источника образцового напряжения, а выход третьего компаратора соединен с вторыми входами третьего и пятого элемента И и информационным входом триггера старшего разряда аналого-цифрового преобразователя, второй вход четвертого компаратора соединен с выходом третьего блока вычитания, первы вход которого соединен с выходом третьего источника образцового напряжения, выход четвертого компаратора соединен со вторыми входами четвертого элемента И и второго эле мента ИЛИ, а вторые входы второго и третьего блоков вычитания соединены с входной шиной, вход синхро.низации триггера старшего разряда аналого-цифрового преобразователя соединен с входом синхронизации три гера старшего разряда регистра, а его прямой выход соединен с третьим входами второго и пятого элементов И и с выходной шиной старшего разряда аналого-цифрового преобразователя, а его инверсный выход с треть ими входами первого и четвертого элементов И и с первым входом элеме та И-НЕ, второй вход которого соеди инверсным выходом триггера старшего разряда регистра, а выходс входом старшего разряда цифро-аналогового преобразователя, На чертеже представлена функцио- нальная схема предлагаемого устройства. Аналого-цифровой преобразователь содержит блок 1 управления, входную шину 2, двуматричный цифроаналоговый преобразователь 3f компараторы -7, блоки 8-10, вычитания, источники 11-13 образцового напряжения, элемент И-НЕ Н, триггер 15 старшего разряда аналого-цифрового преобразователя, выходные шины 16, элементы И 17-21 и элементы ИЛИ 22 , и 23, регистр 2k, выполеннный на триг-. герах 25, 26... (N-1). Уровни сигналов на выходах компараторов U равны для первого компаратора 4 если Ux ивых.1 1-1 если Ux / ивычи; для компараторов и,ивых.г; 1-1 если U,,g; iUebW.i; если и)в.г ивЬ1И.«1г если U,jgi$UBb n.i; если изв..а , если U,,e..l, ffl J:/B.I Ув.1 .з напряжение на выходе, соответственно первого блока б вычитания, второго блока 9 вычитания третьего блока 10 вычиtaния. Ъв.1 Uo5p. - Ux s)в.1 - Ux в.з обР.з - Ux oбp.-1 Uo6p.at Uo5p.3v Напряжение источников образцового напряжения 11-13 соответственно равных oбp..) вых.тпах и - .М 4- -и оБР.14 Bbw.max п вых. max uU ,. - - и -о обР.З 1 вмх.тах .так Аналого-цифровой преобразователь работает следующим образом. в исходном состоянии на прямом выходе триггера 15 старшего разряда аналого-цифрового преобразователя установлен сигнал О, а на его инверсном выходе - сигнал 1, на прямом выходе триггера 25 старшего разряда регистра 2 установлен сигнал 1, а на его инверсном выходе сигнал О, на прямых выходах тригг ра 26 младших разрядов регистра Zt установлены сигналы О, на первом выходе двуматричного цифро-аналогов го преобразвоателя 3 установлено на пряжение Ugt,ty .равное эталону ста u|gro разряда цифро-аналогового прео разователя, равное U tyiv-f л- 9Ш так ; где Uebivinair максимальная величина преобразуемого напряжения, на втором выходе двуматричного цифро-аналогового преобра-t зователя 3 установлено напряжение Увыха При поступлении напряжения Ux величина которого находится в диапа зоне О Ux U0b(xmci4. на выходе компараторов -J установлены ;сигналы , соответственно. Цикл поразрядного кодирования начинается с установки сигнала 1 на тактовом выходе старшего разряда блока управления 1, который воздействует на синхронизационные входы триггеров 15 и 25. Под воздействием сигнала 1, с тактового выхода стар шего разряда блока 1 управления и сигнала О с выхода третьего компаратора 6 триггер 15 не изменяет своего состояния и в старшем разряде ВЫХОДНОГО кода записывается О. Под воздействием сигнала 1 с тактового выхода старшего разряда блока 1 управления и сигнала О с выхода второго элемента ИЛИ 23 триггер 25 регистра 2 изменяет свое состояние, на его прямом выходе устанавливается сигнал О , а. на инверсном выходе . В следующий за старшим сигнал разряд выходного кода М аналого-цифрового преобразователя записывается О, На входах элемента И-НЕ устанавливается сигнал 1, а на его выходе - сигнал О. Сигналом О, с выхода элемента И-НЕ k эталон старшего разряда цифро-аналогового преобразователя 3 отключается от i%(,i В конце первого такта блокируются выходы компараторов через элемен ты И 18-20, и разрешается прохождени сигналов с выхода первого компаратора k через элемент И 17. Во втором и последующих тактах преобразования формирование выходного кода Н аналого-цифрового преобразователя осу186ществляется по сигналам с выхода первого компаратора Ц, сравнивающего напряжения U и ид.,, Сигналы с выхода компаратора ч через элементы ,И 17 и ИЛИ 22 поступают на информационные входы триггера 2б,... N регистра 2. Аналого-цифровой преобразователь работает по способу поразрядного кодирования. Поскольку преобразование напряжения Ux осущест вляется.без участия эталонов, величины которых равны 1/2 UgbwrndxH ц &blxmaxTO погрешность преобразования находится в интервале ° %n 4 mo xПри поступлении напряжения U;( , величина которого находится в диа1 ВЫХтс|х пазоне вЬ1Х max на выходах компараторов и 7 установлены сигналы 1, а на выходах компараторов 5 и ответственно, на выходах первого и и ИЛИ 22 и 23 сигнавторого элемента лы 1. Цикл поразрядного кодирования начинается с установки сигнала 1 на тактовом выходе старшего разряда блока 1 упрайления. Под воздействием сигнала 1, с тактового выхода старшего разряда блока 1 управления и сигнала О, с выхода третьего компаратора 6 триггер 15 не изменяет своего состояния, т.е. в старшем разряде выходного кода N записывается . Под воздейстием сигнала 1 с тактового выхода старшего разряда блока 1 управления и сигнала 1 с выхода второго элемента ИЛИ 23 гер 25 регистра 2k не изменяет своего состояния и в следующий за старшим разряд выходного кода аналого-цифрового преобразователя записывается О. На первом входе элемента И-НЕ I устанавливается на его втором входе сигнал . , О, устанавливается сигнал его выходе - сигнал 1, по которому эталон старшего разряда цифро-аналогового преобразователя 3 остается подключенным к выходу Ugj,,. В конце первого такта блокируются выходы компаратов через элементы И и разрешается прохождение сигналов 1 . с выхода четвертого компаратора 7 через элемент И 20, Во втором и посл дующих тактах преобразования формиро вание выходного кодаМ яналого-цифро вого преобразователя осуществляется по сигналам с выхода компаратор ; 7 сравнивающего напряжения U%/giM -выхО. Л злого-цифровой преобразоватепь работает по способу поразрядного кодирования. Поскольку преобразование напряжения U осуществляется путем его уравновешивания эталонным напряжением с второго выхода цифро-ачалогового преобразователя 3 , участия эталонов, величины которых равны йых.тах 4 бых. шах погрешность преобразования находится в интервале О : V : 1V ЛЦЛ 4 При поступлении напряжения Ux , величина которого находится в диапат зоне ill :и -U 12. BbtX.max- ftblC.fnciX то в исходном состоянии на выходах компараторов 4 и 6 установлены сигналы 1, на выходах компараторов 5 и 7 установлены сигналы О. Цикл поразрядного кодирования начинается с установки сигнала 1 на тактовом выходе старшего разряда блока 1 управления. Под воздействием сигнала 1 с тактового выхода старшего разряда блока 1 управления и сигнала 1 с выхода третьего компаратора 6 триггер 15 изменяет свое состояние, на его прямом выходе уста навливается сигнал Il, а на инверсном выходе - сигнал О. В . старшем разряде выходного кoдaN записывается 1, Под воздействием сигнала 1 с тактового выхода старшего разряда блока 1 управления и сигнала О с выхода второго элемента ИЛИ 22 триггер 25 регистра 2k изменяет свое состояние, на его прямом выходе устанавливается сигнал О, а на инверсном выходе - сигнал 1. В следующий за старшим разряд выходного кода N аналого-цифрового пре образователя записывается О. На первом входе элемента И-НЕ Н устанавливается сигнал О, на его втором входе устанавливается сигнал 1, а на его выходе - сигнал 1, 88 по которому эталон старшего разряда цифро-ауахюгового преобразователя 3 остается подключенным к выходу Usbix - конце первого такта блокируются выходы компараторов 4,5 и 7 через элементы И 17, 1Ь и 20 и разрешается прохождение сигналов с выхода третьего компаратора 6 через элемент И 19. Во втором и последующих тактах преобразования формирование выходного кода N аналого-цифрого преобразователя осуществляется по сигналам с выхода компаратора 6, сравнивающего напряжения Ughiyo Аналого-цифровой преобразователь работает по способу поразрядного кодирования. Поскольку преобразование напряжения Uy осуществляется при отключенных от U,«2 эталонах старших разрядов цифро-аналогового преобразователя 3, равных jLuU -и а вых.тпах 4 BbW-wax погрешность преобразования находится в интервале При поступлении напряжения U по своей величине находится в диапазоне 4 ВЫХ.ттгах Х е |х.таХ то в исходном состоянии на выходах компараторов -6 установлены сигналы 1, на выходе компаратора 7 установлен сигнал О на выходе второго элемента ИЛИ , а на его третьем выходеС41гнал О. Цикл поразрядного кодирования начинается с установления сигнала 1 на тактовом выходе старшего разряда блока 1 управления. Под воздействием сигнала 1 с тактового выхода старшего разряда блока 1 управления и си|- нала 1 с выхода третьего компаратора 6 триггер 15 изменяет свое состояние, на его прямом выходе устанавливается сигнал 1, а на инверсном выходе - сигнал О. В старший разряд выходного кодам записывается 1. Под воздействием сигнала 1 с тактового выхода старшего разряда блока 1 управ ления и сигнала i с выхода второго элемента ИЛИ 23 триггер 25 регистра 2k не изменяет своего состояния и в следующий за старшим разрядом выходного кода N аналого-цифрового преобразовтеля записывает 1. На входах элемента И-НЕ устанавлива99ются сигналы О, а на его выходе сигнал 1, по которому эталон старшег разряда цифро-аналогового преобразователя 3 остается подключенным к eblx-i В конце первого такта блокиру ются выходы компараторов А,6 и 7 через элементы И 17, 19 и 20. и разрешается прохождение сигналов с выход второго компаратора 5 через элемент 18. Во втором и последующих тактах преобразования формирование выходного кода N аналого-цифрового преобра зователя осуществляется по сигналам с выхода компаратора 5 сравнивающего напряжения Uy и Ug iyiАналогоцифровой преобразователь работает по способу поразрядного кодирования. Поскольку преобразование напряжения Ux осуществляется при отключенных от эталонах старших разрядов цифр аналогового преобразователя 3 равным7. йых.тох 4- BWX. погрешность преобразования находится в интервале AU, После окончания цикла преобразова ния аналого-цифровой преобразователь в исходное состояустанавливаетсяние. Формула изобретения Аналого-цифровой преобразователь поразрядного кодирования, содержащий блок управления, установовчный выход которого соединен с входами начального состояния триггеоов регистра, а тактовые выходы - с входами синхронизации триггеров регистра, прямые выходы которых соединены с выходными шинами и, кроме прямого выхода тригрегистра, гера старшего разряда с входами двуматричного цифроаналогового преобразователя первый выход которого соединен с первым входом первого компаратора, второй вход которого соединен с входной шиной, а выход - с первым входом первого элемента И, второй вход которого соединен с инверсным выходом триггера старшего разряда, а его выход с первым входом первого элемента ИЛИ, второй вход двуматричного цифроаналогового преобразователя соединен с первым входом второго компаратора, второй вход которого соеди- , l8 С выходом первого блока вычитанейния, первый вход которого соединен с выходом первого источника образцового напряжения, второй вход с входной шиной, выход второго компаратора соединен с первыми входами второго и третьего элементов И, второй вход второго элемента И соединен с первым входом четвертого элемента И и прямьм выходом триггера старшего разряда регистра, а выход - со вторым входом первого элемента ИЛИ, выход четвертого элемента И соединен с третьим входом первого элемента ИЛИ, первый вход пятого элемента И соединен с вторым входом первого элемента И, а выход - с четвертым входом первого элемента ИЛИ, выход которого соединен с информационными входами триггеров младших разрядов регистра, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с информационным входом три1- гер старшего разряда регистра, отличающи йся тем, что, с целью повышения точности преобразования, в него дополнительно введены два компаратора, два блока вычитания, -два источника образцового напряжения, элемент И-НЕ и триггер старшего разряда аналого-цифрового преобразователя, причем первые входы третьего и четвертого компараторов соедин ены с вторым выходом двуматричного цифроаналогового преобразователя, второй вход третьего компаратора соединен с выходом второго блока вычитания, первый вход которого соединен с выходом второго источника образцового напряжения, а выход третьего компаратора соединен с вторыми входами третьего и пятого элементов И и информационным входом триггера старшего разряда аналогоцифрового преобразо;вателя, второй вход четвертого компаратора соединен с выходом третьего блока вычитаия, первый вход которого соединен выходом третьего источника образового напряжения, выход четвертоо компаратора соединен с вторыми ходами четвертого элемента И и втоого элемента ИЛИ,а вторые входы втоого и.третьего блоков вычитания соеинены с входной шиной, вход синхроизации триггера старшего разряда налого-цифрювого преобразователя оединен с входом синхронизации триг 9364

гера старшего разряда регистра, а его прямо выход - с третьими входами второго и пятого элементов И и с выходной шиной старшего разряда аналого-цифрового преобразова- j геля, а его инверсный выход с третьими входами первого и четвертого элементов И и с первым входом элемента И-НЕ, второй вход которого соединен с инверсным вы- to

1812

ходом триггера старшего разряда регистра, а выход - с входом ста шего разряда цифроаналогового преобразователя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 750727, кл. н 03 К 15/17, 197« (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1981 |

|

SU999157A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU750727A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU945977A1 |

Авторы

Даты

1982-06-15—Публикация

1980-10-02—Подача