Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения различных датчиков с вычислительными устройствами, функционирующими в системе остаточных классов (СОК) и в двоичной системе счисления, а также для преобразования напряжения в цифровой код СОК и двоичный код в измерительных устройствах и устройствах обработки сигналов.

Известен аналого-цифровой преобразователь поразрядного кодирования (1), содержащий компаратор, регистр последовательных приближений и цифроаналого- вый преобразователь.

Однако этот преобразователь не позволяет получить код в системе остаточных классов,

Наиболее близким к предлагаемому является преобразователь напряжения в код системы остаточных классов (2, содержащий первый аналого-цифровой преобразователь конвейерного типа разрядности п

m log2 П Pi,

i 2

где Р|-основания системы остаточных классов, an- число оснований;

второй аналого-цифровой преобразователь разрядности I log2Pi, n-1 шифратоXI

О

сл

00

ю

ров, п-1 сумматоров по модулям других оснований системы ос-таточных классов, кроме наименьшего, m элементов И, первые входы которых являются m управляющими входными шинами преобразователя, выхо- ды подключены к соответствующим первым входам п-1 шфраторов, вторые входы подключены к цифровым выходам первого аналого-цифрового преобразователя конвейерного типа, аналоговый вход которого является входной шиной преобразователя, аналоговый выход подключен к входу второго аналого-цифрового преобразователя, выходы которого являются выходными шинами преобразователя по наименьшему основанию и подключены к соответствующим входам блока ключей, управляющий вход которого является т+1 управляющей входной шиной преобразователя, выходы подключены к соответствующим вторым входам п-1 шифраторов, выходы которых подключены к входам п-1 сумматоров по модулям других оснований системы остаточных классов, кроме наименьшего, выходы которых являются выходными шинами преобразователя по соответствующим основаниям,

Но это устройство характеризуется большими аппаратными затратами, большим количеством управляющих шин и шин источников эталонных напряжений, обеспечивающих работу устройства, и невозможностью получения цифрового эквивалента входного напряжения в двоичном коде.

Целью изобретения является сокраще- ние аппаратных затрат и расширение функ- циональных возможностей за счет возможности получения двоичного кода и кода в СОК одновременно.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь в код системы остаточных классов, содержащий п-1 сумматоров по модулям оснований системы остаточных классов, где п - количество оснований, выходы которых являются пер- вой выходной шиной кодов соответствующих остатков, блок аналого-цифрового преобразования, первые выходы которого являются второй выходной шиной, второй выход соединен с первым входом элемента И, а первый вход является входной информационной шиной, и шифратор, введены сумматор по модулю n-го основания, выход которого является первой выходной шиной кода n-го остатка, элемент задержки и запо- минающее устройство, шифратор выполнен на приоритетном шифраторе, а блок аналого-цифрового преобразования выполнен в виде последовательно соединенных компаратора, первый вход и выход которого является одноименным входом и вторым входом блока аналого-цифрового преобразования, регистра последовательных приближений, выходы разрядов которого являются первыми выходами блока аналого-цифрового преобразования, и цифроаналогового преобразователя, выход которого подключен ко второму входу компаратора, второй вход регистра последовательных приближений является входной шиной запуска, а третий вход является входной шиной тактовых импульсов и объединен со входом элемента задержки, выход которого соединен со вторым входом элемента И, выход которого соединен со входами разрешения суммирования п сумматоров по модулю оснований системы остаточных классов, входы суммирования которых через запоминающее устройство подключены соответственно к выходам приоритетного шифратора, входы с меньшим приоритетом которого подключены соответственно к выходам старших разрядов регистра последовательных приближений, выходы младших разрядов которого соответственно соединены к входам с большим приоритетом приоритетного шифратора.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием постоянного запоминающего устройства, сумматора по модулю n-го основания, АЦП поразрядного кодирования, элемента задержки и новыми связями между элементами.

Таким образом заявляемое устройство соответствует критерию изобретения новизна.

Сравнение заявляемого устройства с другими техническими решениями показывает, что блоки, входящие в структуру устройства, известны, но связи между ними создают новые свойства, обеспечивающие экономию оборудования и расширение функциональных возможностей, что позволяет сделать вывод о соответствии технического решения критерию существенные отличия.

При патентных исследованиях использование тех же узлов с аналогичной целью не обнаружено.

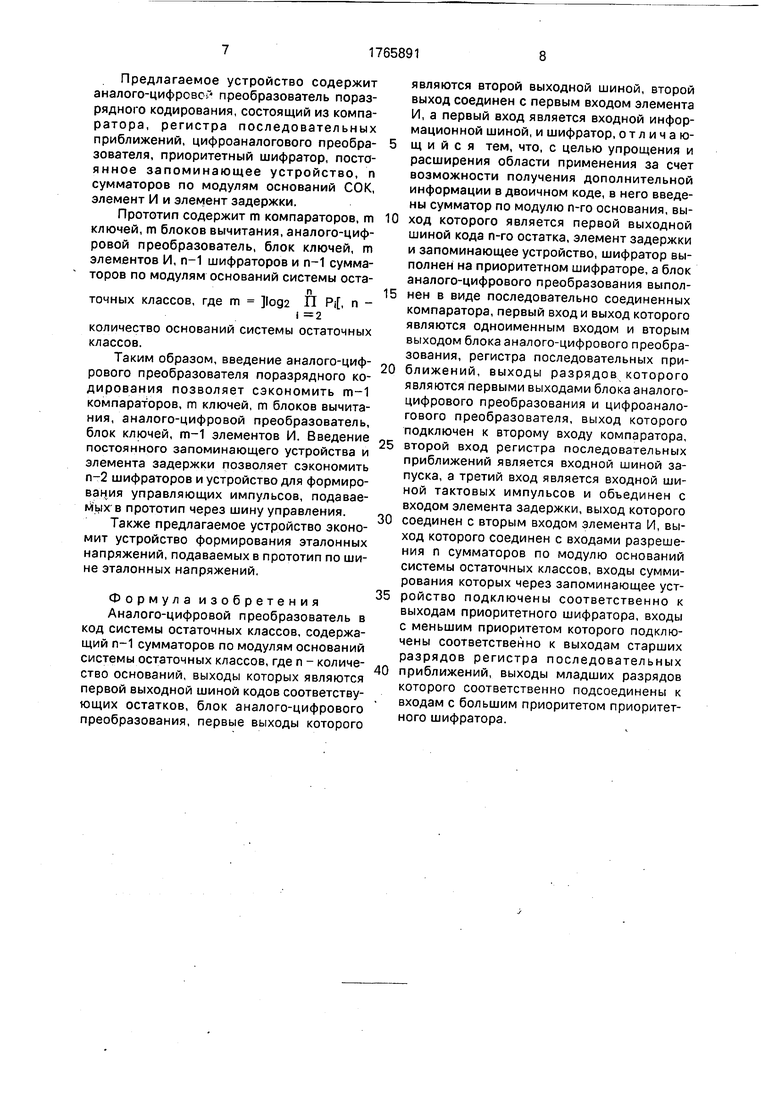

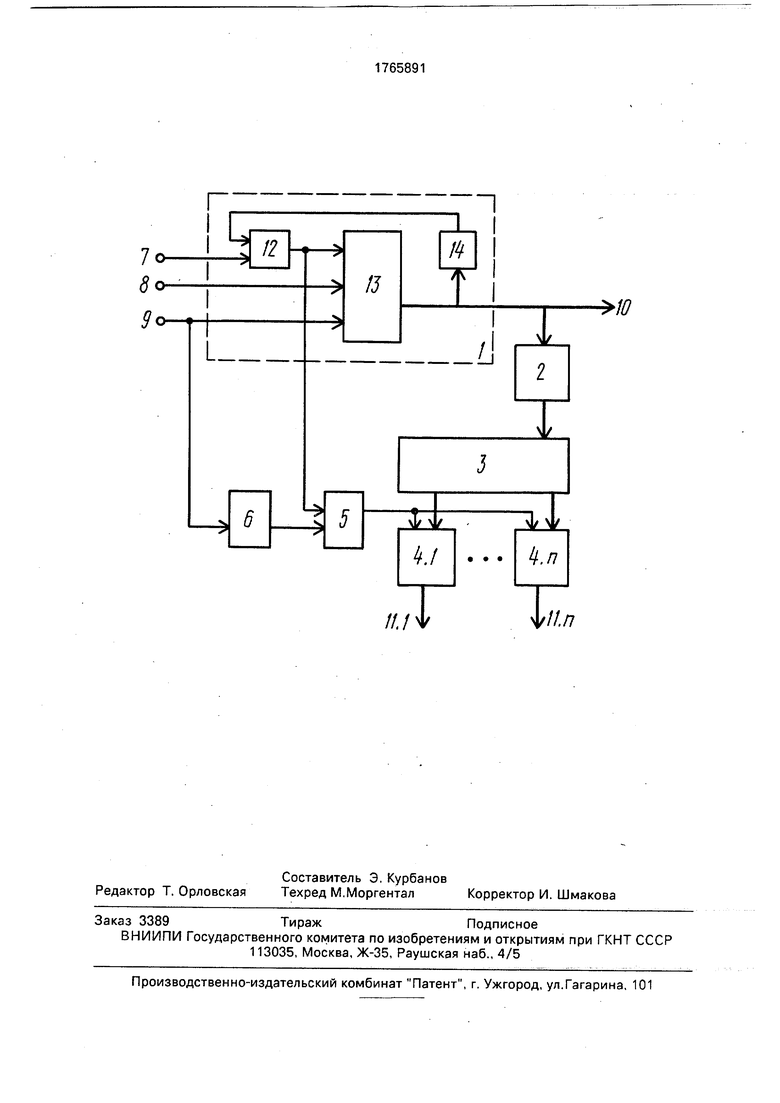

На фиг.1 представлена структурная схема аналого-цифрового преобразователя в код системы остаточных классов.

Устройство содержит айалого-цифро- вый преобразователь 1 поразрядного кодирования, приоритетный шифратор 2, постоянное запоминающее устройство 3, сумматоры 4.1-4.П по модулям оснований СОК, элемент И 5, элемент задержки 6, входную шину 7, управляющую шину 8 запускающего импульса, шину 9 тактовых импульсов, выходную шину 10 двоичного кода, выходные шины 11.1-11.п остатков СОК, где п - количество оснований СОК.

Аналого-цифровой преобразователь 1 поразрядного кодирования выполнен на компараторе 12, регистре последовательных приближений 13 и цифроаналоговом преобразователе 14.

Устройство работает следующим образом.

Преобразуемому напряжению DX ставится в соответствие цифровой эквивалент А в двоичном коде и в системе остаточных классов:

UX A -Д±н,

где А - величина шага квантования; н - погрешность преобразования. Разрядные цифры Xi, X2, ..., Хп, которыми представляется цифровой эквивалент А в СОК, определяются из выражения:

А + Xi,

где Pj - величины выбранных взаимно простых оснований СОК, с помощью которых представляется число А в диапазоне

пп

П Pi - 1; т.е. имеется И Pi уровней кванто-

вания. Величину А можно представить в двоичном коде:

A ai2° + a221 + ... + , где а - разрядные цифры числа А в двоичном представлении, принимающие значения 0 и 1 ;

п

m log2 П PI - ближайшее целое

i 1

п число, не меньшее числа Iog2 П PI. Регистр

i 1

последовательных приближений 13 и циф- роаналоговый преобразователь имеют разрядность, равную т.

В исходном состоянии регистр последовательных приближений 13 и сумматоры 4.1-4.П по модулям СОК обнулены.

Преобразуемое напряжение Ux подается по шине 7 на первый вход компаратора 12. После подачи по шине 8 запускающего импульса начинается процесс поразрядного кодирования, в первом такте которого в старшем разряде регистра последовательных приближений 13 выставляется уровень огической единицы. Приоритетный шифраор 2 имеет m входов и I log2m выходов. Старшие разряды регистра последовательных приближений 13 подключены к входам приоритетного шифратора 2, имеющим меньший приоритет, а младшие - к входам

с большим приоритетом. Поэтому на выходе шифратора 2 имеем код, соответствующий входу с наименьшим приоритетом. Этот код подается на адресные входы постоянного запоминающего устройства 3 емкостью плх х К, где К - разрядность кода в выбранный СОК. В постоянной запоминающее устройство 3 записаны m кодов в СОК, являющиеся эквивалентными чисел 2,2, ..., .

Таким образом, в первом такте на выходных шинах постоянного запоминающего устройства 3 появятся остатки СОК, соответствующие числу , которые подаются на сумматоры 4.1-4.П по модулям соответствующих оснований СОК.

На выходе цифроаналогового преобразователя 14 вырабатывается напряжение 2т А , которое сравнивается компаратором 12 с преобразуемым напряжением Ux.

Если Ux«Ј A, то на выходе компаратора 12 низкий логический уровень и с приходом следующего тактового импульса единица в старшем разряде регистра последовательных приближений 13 не сохранится. Если

же Ux A, то высокий логический уровень на выходе компаратора 12 через элемент И 5 разрешает суммирование сумматором 4.1-4.П по модулям оснований СОК с приходом задержанного элементом

задержки б тактового импульса. Задержка необходима для установления переходных процессов на выходах постоянного запоминающего устройства Зина выходе компаратора 12.

Во втором такте устанавливается логическая единица в следующем разряде регистра последовательных приближений 13 и шифратором 2 выбирается код СОК на выходах постоянного запоминающего устройства 3, соответствующий числу ,

На выходе цифроаналогового преобразователя 14 имеем напряжение (ат 2 + ) А, где ат - старший разряд регистра последовательных приближений 13, имеющий значение 0 или 1.

По результатам сравнения компаратором 12 напряжения Ux и напряжения на выходе цифроаналогового преобразователя 14 либо дается, либо не дается разрешение

суммирования сумматором 4.1-4,.п по модулям оснований СОК.

Таким образом за т+1 тактов на шине 10 получим цифровой эквивалент преобразуемого напряжения в двоичной системе

счисления, а на шинах 11.1-11.п образуются

остатки XL X2Хп в системе остаточных

классов.

Подсчитаем выигрыш аппаратурных затрат.

Предлагаемое устройство содержит аналого-цифровое преобразователь поразрядного кодирования, состоящий из компаратора, регистра последовательных приближений, цифроаналогового преобра- зователя, приоритетный шифратор, постоянное запоминающее устройство, п сумматоров по модулям оснований СОК, элемент И и элемент задержки.

Прототип содержит m компараторов, m ключей, m блоков вычитания, аналого-цифровой преобразователь, блок ключей, m элементов И, п-1 шифраторов и п-1 сумматоров по модулям оснований системы остап

точных классов, где m Jloga П Pi, n I 2

количество оснований системы остаточных классов.

Таким образом, введение аналого-циф- рового преобразователя поразрядного кодирования позволяет сэкономить т-1 компараторов, m ключей, m блоков вычитания, аналого-цифровой преобразователь, блок ключей, т-1 элементов И. Введение постоянного запоминающего устройства и элемента задержки позволяет сэкономить п-2 шифраторов и устройство для формирования управляющих импульсов, подаваемых в прототип через шину управления.

Также предлагаемое устройство экономит устройство формирования эталонных напряжений, подаваемых в прототип по шине эталонных напряжений.

Формула изобретения Аналого-цифровой преобразователь в код системы остаточных классов, содержащий п-1 сумматоров по модулям оснований системы остаточных классов, где п - количество оснований, выходы которых являются первой выходной шиной кодов соответствующих остатков, блок аналого-цифрового преобразования, первые выходы которого

5

0

5

п с

5

0

являются второй выходной шиной, второй выход соединен с первым входом элемента И, а первый вход является входной информационной шиной, и шифратор, отличающийся тем, что, с целью упрощения и расширения области применения за счет возможности получения дополнительной информации в двоичном коде, в него введены сумматор по модулю n-го основания, выход которого является первой выходной шиной кода n-го остатка, элемент задержки и запоминающее устройство, шифратор выполнен на приоритетном шифраторе, а блок аналого-цифрового преобразования выполнен в виде последовательно соединенных компаратора, первый входи выход которого являются одноименным входом и вторым выходом блока аналого-цифрового преобразования, регистра последовательных приближений, выходы разрядов которого являются первыми выходами блока аналого- цифрового преобразования и цифроаналогового преобразователя, выход которого подключен к второму входу компаратора, второй вход регистра последовательных приближений является входной шиной запуска, а третий вход является входной шиной тактовых импульсов и объединен с входом элемента задержки, выход которого соединен с вторым входом элемента И, выход которого соединен с входами разрешения п сумматоров по модулю оснований системы остаточных классов, входы суммирования которых через запоминающее устройство подключены соответственно к выходам приоритетного шифратора, входы с меньшим приоритетом которого подключены соответственно к выходам старших разрядов регистра последовательных приближений, выходы младших разрядов которого соответственно подсоединены к входам с большим приоритетом приоритетного шифратора.

//./Ф

i

tin

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2010 |

|

RU2433527C1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1983 |

|

SU1181140A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1983 |

|

SU1181141A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1034170A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1986 |

|

SU1368989A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения различных датчиков с вычислительными устройствами, функционирующими в системе остаточных классов (СОК) и в двоичной системе счисления, а также для преобразования напряжения в цифровой код СОК. Целью изобретения является упрощение и расширение области применения за счет возможности получения дополнительной информации в двоичном коде. Цель достигается тем, что в аналого-цифровой преобразователь в код системы СОК, содержащий п-1 сумматоров по модулям оснований системы остаточных классов, блок аналого-цифрового преобразования, элемент И и шифратор, введены сумматор по модулю n-го основания, выход которого является первой выходной шиной кода n-го остатка, элемент задержки и запоминающее устройство, шифратор выполнен на приоритетном шифраторе, а блок аналого-цифрового преобразования выполнен в виде последовательно соединенных компаратора, регистра последовательных приближений и цифроаналогового преобразователя. 1 ил. у Ё

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И., Пискулев Е,А | |||

| Аналого- цифровые преобразователи | |||

| Учебное пособие для вузов | |||

| М.: Энергоиздат, 1981 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь напряжения в код системы остаточных классов | 1983 |

|

SU1181139A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-09-30—Публикация

1990-09-10—Подача